可重新配置的互补金属氧化物半导体装置及方法与流程

1.本发明涉及阈值电压可编程场效应晶体管(例如,铁电场效应晶体管(ferroelectric field effect transistor;fefet)等),尤其涉及可重新配置的互补金属氧化物半导体(complementary metal oxide semiconductor;cmos)装置、形成该装置的方法以及重新配置(也就是,编程)该装置的方法的实施例。

背景技术:

2.倍频器是无线通信系统(其中需要稳定的高频振荡)的基本组件。当前最新的倍频器包括滤波及放大电路。遗憾的是,此类滤波放大电路消耗大量的芯片面积及功率。

技术实现要素:

3.本文中揭示可重新配置的互补金属氧化物半导体(cmos)装置的实施例。该装置包括多个场效应晶体管(fet),尤其n型场效应晶体管(nfet)及p型场效应晶体管(pfet)。该nfet及该pfet都可为阈值电压可编程fet。此外,该nfet与该pfet可并联电性连接,并可具有电性连接的栅极。利用此配置,该nfet及该pfet的阈值电压可通过施加特定的一组电压条件来同时编程(如具体实施方式部分中进一步讨论)。作为所述施加该特定组电压条件的结果,可在该两个fet中达到多个可能阈值电压组合中的一个特定阈值电压组合,以使该装置可操作于多种可能操作模式(例如,倍频操作模式、正信号传输模式、信号阻挡模式等)中的一种特定操作模式。利用此配置,该nfet及该pfet的阈值电压可选地通过施加不同的一组电压条件来重新编程(例如,在现场(in the field)),以在该两个fet中达到一个不同的特定阈值电压组合,并因此将该装置切换至该多种可能操作模式中的不同的一种操作模式。

4.本文中还揭示形成如上所述的可重新配置的互补金属氧化物半导体(cmos)装置的方法的实施例。该方法可包括提供衬底,以及在该衬底上形成该可重新配置的互补金属氧化物半导体(cmos)装置。具体地说,该方法可包括在该衬底上形成互补的一对场效应晶体管(fet),尤其n型fet(nfet)与p型fet(pfet)。该nfet及pfet可经形成以使它们为阈值电压可编程fet。此外,该nfet及该pfet可经形成以使它们并联电性连接并使它们具有电性连接的栅极。

5.本文中还揭示用于重新配置(在本文也称为编程)如上所述的可重新配置的互补金属氧化物半导体(cmos)装置的方法的实施例。具体地说,该方法可包括提供这样的可重新配置的cmos装置。该方法还可包括同时编程该nfet及该pfet的阈值电压。具体地说,该nfet及该pfet的阈值电压可通过施加特定的一组电压条件来同时编程(如具体实施方式部分中进一步讨论)。作为所述施加该特定组电压条件的结果,可在该两个fet中达到多个可能阈值电压组合中的一个特定阈值电压组合,以使该装置可操作于多种可能操作模式(例如,倍频操作模式、正信号传输模式、信号阻挡模式等)中的一种特定操作模式。可选地,该方法还可包括通过施加不同的一组电压条件来同时重新编程该nfet及该pfet的阈值电压

(例如,在现场),以在该两个fet中达到一个不同的特定阈值电压组合,并因此将该装置切换至该多种可能操作模式中的不同的一种操作模式。

附图说明

6.通过参照附图自下面的详细说明将更好地理解本发明,该些附图并不一定按比例绘制,且其中:

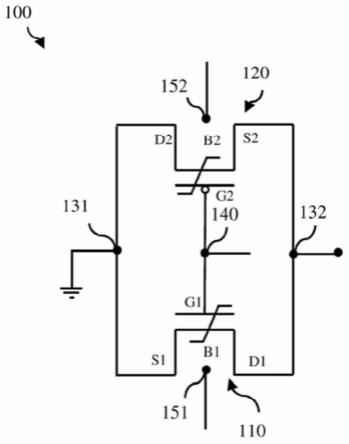

7.图1是显示所揭示的可重新配置的互补金属氧化物半导体(cmos)装置的实施例的示意图;

8.图2a显示该可重新配置的cmos装置的实施例的示例布局图,且图2b及2c显示可被包含于该可重新配置的cmos装置的实施例中的示例阈值电压可编程fet(例如,n型及p型铁电场效应晶体管(fefet))的剖视图;

9.图3是显示可用以重新配置包括n型及p型fefet的该可重新配置的cmos装置的实施例的示例组电压条件的表格;

10.图4a-1是显示第一装置状态的负和正阈值电压曲线的图形,且图4a-2显示包括针对图3的表格中所列出的且与该第一装置状态相关的倍频模式的漏极电流-栅极电压曲线、输入电压信号、以及输出电流信号的图形;

11.图4b-1是显示第二装置状态的负和正阈值电压曲线的图形,且图4b-2显示包括针对图3的表格中所列出的且与该第二装置状态相关的正信号传输模式的漏极电流-栅极电压曲线、输入电压信号、以及输出电流信号的图形;

12.图4c-1是显示第三装置状态的负和正阈值电压曲线的图形,且图4c-2显示包括针对图3的表格中所列出的且与该第三装置状态相关的信号阻挡模式的漏极电流-栅极电压曲线、输入电压信号、以及输出电流信号的图形;

13.图4d-1是显示第四装置状态的负和正阈值电压曲线的图形,且图4d-2显示包括针对图3的表格中所列出的且与该第四装置状态相关的负信号传输模式的漏极电流-栅极电压曲线、输入电压信号、以及输出电流信号的图形;

14.图4e-1是显示第五装置状态的负和正阈值电压曲线的图形,且图4e-2显示包括针对图3的表格中所列出的且与该第五装置状态相关的替代传输模式的漏极电流-栅极电压曲线、输入电压信号、以及输出电流信号的图形;

15.图5是显示用于形成该可重新配置的cmos装置的方法实施例的流程图;以及

16.图6是显示用于重新配置该可重新配置的cmos装置的方法实施例的流程图。

具体实施方式

17.如上所述,倍频器是无线通信系统(其中需要稳定的高频振荡)的基本组件。当前最新的倍频器包括滤波及放大电路。遗憾的是,此类滤波放大电路消耗大量的芯片面积及功率。

18.鉴于上述,本文中揭示具有多种不同操作模式(包括但不限于倍频模式)的可重新配置的互补金属氧化物半导体(cmos)装置的实施例。该装置可包括n型场效应晶体管(nfet)及p型场效应晶体管(pfet),它们是阈值电压可编程的,并联连接,并具有电性连接的栅极。利用此配置,可同时编程该nfet及pfet的阈值电压,并可依据在编程期间在该nfet

及pfet中达到的阈值电压的特定组合来设置该装置的操作模式。例如,若nfet具有低正阈值电压且pfet具有低负阈值电压,则该装置可操作于倍频模式。此外,根据需要,可同时重新编程(例如,在现场)该nfet及pfet的阈值电压,以切换该装置的操作模式。这样的装置可较小(也就是,可消耗最小量的芯片面积),并可以最小的功耗达到倍频及其它功能。本文中还揭示用于形成该装置的方法的实施例以及用于重新配置该装置的方法的实施例(也就是,用于同时编程该nfet及pfet,以设置或切换操作模式)。

19.图1是显示可重新配置的互补金属氧化物半导体(cmos)装置100的实施例的示意图。图2a-2c是显示装置100的示例实施例的顶视图布局及两个剖视图(如下面更详细讨论)。

20.请一并参照图1及2a-2c,可重新配置的cmos装置100可包括一对互补场效应晶体管(fet),尤其n型fet 110(nfet)及p型fet 120(pfet)。nfet 110与pfet 120可并联电性连接,并可具有电性连接的栅极。

21.出于示例说明的目的,装置100的nfet 110及pfet 120在下面说明并在附图中显示为位于块体半导体衬底(例如,块体硅衬底)上的平面fet。不过,应当理解,该些附图并非意图限制。作为替代,该nfet及该pfet可为非平面fet及/或位于绝缘体上半导体(例如,绝缘体上硅(silicon-on-insulator;soi))衬底上。

22.所揭示的装置100的各实施例可包括nfet 110。nfet 110可具有第一本体区(b1)(例如,p-本体区)(例如,由浅沟槽隔离(shallow trench isolation;sti)区205定义),以及在该第一本体区(b1)中,横向位于第一源极区(s1)(例如,n+源极区)与第一漏极区(d1)(例如,n+漏极区)之间的第一沟道区(c1)(例如,p-沟道区)。可选地,nfet 110还可具有,在该第一本体区(b1)中,(例如通过sti区205)与该第一源极区(s1)及该第一漏极区(d1)电性隔离的第一本体接触区(bc1)(例如,p+区)。该第一本体接触区(bc1)可促进在装置编程期间接触该第一本体区(b1),如下面更详细讨论。nfet 110还可具有邻近该第一沟道区(c1)的第一栅极(g1)。

23.所揭示的装置100的各实施例还可包括pfet 120。pfet 120可具有第二本体区(b2)(例如,n-本体区)(例如,由sti区205定义),以及在该第二本体区(b2)中,横向位于第二源极区(s2)(例如,p+源极区)与第二漏极区(d2)(例如,p+漏极区)之间的第二沟道区(c2)(例如,n-沟道区)。可选地,pfet 120还可具有,在该第二本体区(b2)中,(例如,通过sti区205)与该第二源极区(s2)及该第二漏极区(d2)电性隔离的第二本体接触区(bc2)(例如,n+区)。该第二本体接触区(bc2)可促进在装置编程期间接触该第二本体区(b2),如下面更详细讨论。pfet 120还可具有邻近该第二沟道区(c2)的第二栅极(g2)。

24.nfet 110与pfet 120可并联电性连接。也就是说,nfet 110的第一漏极区(d1)可与pfet 120的第二源极区(s2)电性连接(例如,通过局部互连或通过接触与后端工艺线路的组合)。而且,nfet 110的第一源极区(s1)可与pfet 120的第二漏极区(d2)电性连接(例如,通过局部互连或通过接触与后端工艺线路的组合)。此外,nfet 110及pfet 120的栅极(也就是,第一栅极(g1)与第二栅极(g2))也可电性连接。

25.具体地说,nfet 110及pfet 120可为阈值电压可编程fet。也就是说,nfet 110可为阈值电压可编程nfet,且pfet 120可为阈值电压可编程pfet。本领域的技术人员将意识到,阈值电压可编程fet是指可响应施加于该fet的栅极及源极/漏极区以及/或者该fet的

本体区的特定的一组电压条件而编程(也就是,选择性改变、调节等)该fet的阈值电压。也就是说,施加于该栅极及该源极/漏极区以及/或者该本体区的不同组电压条件可分别使该fet呈现不同的阈值电压。具体地说,各阈值电压可编程nfet将具有两个或更多的不同可编程正阈值电压,而阈值电压可编程pfet将具有两个或更多的不同可编程负阈值电压。可被包含于装置100中的示例电压可编程fet包括但不限于铁电场效应晶体管(fefet)、浮栅场效应晶体管(floating gate field effect transistor;fgfet),以及电荷捕获场效应晶体管(charge-trap field effect transistor;ctfet)。本领域的技术人员还将意识到,不同可编程阈值电压的数目可依据阈值电压可编程fet的类型(例如,fefet、fgfet、ctfet等)而变化。本领域的技术人员还将意识到,为编程目的而施加于阈值电压可编程fet的栅极及源极/漏极区以及/或者本体区的不同组电压条件将依据阈值电压可编程fet的类型(例如,fefet、fgfet、ctfet等)以及该fet的导电类型(例如,n型或p型)而变化(如下面关于用于重新配置装置100的方法实施例更详细讨论)。

26.出于示例说明的目的,装置100在下面更详细地说明并在图2a-2c中显示为包括n型fefet 110及p型fefet 120。也就是说,图2a是显示可用于此类装置100的示例布局的顶视图,且图2b及2c分别是n型fefet 110及p型fefet 120的剖视图,它们并联连接且具有如图2a的布局中所示的电性连接的栅极。

27.应当理解,nfet 110及pfet 120的第一与第二栅极(g1/g2)的配置将分别依赖于它们是什么类型的阈值电压可编程fet。例如,在图2a-2c中所示的示例实施例中(其中,nfet 110及pfet 120都为fefet),各栅极结构g1、g2可为多层栅极结构,至少包括:邻近沟道区的铁电层147(例如,氧化铪层或某种其它合适的铁电层);以及位于铁电层147上的金属栅极层148。可选地,各栅极结构g1、g2可包括堆叠于沟道区与铁电层147之间的较薄栅极绝缘体层146(例如,二氧化硅层或其它合适的绝缘体层)(如图所示)。可选地,各栅极结构g1、g2还可包括额外的金属栅极层,从而铁电层147被夹置于两个金属栅极层(未显示)之间。

28.在nfet 110与pfet 120是不同类型的阈值电压可编程fet(例如,fgfet或ctfet)的替代实施例中(未显示),栅极结构将不同。例如,fgfet的栅极结构可为多层栅极结构,包括:邻近沟道区的栅极介电层;邻近该栅极介电层的浮栅层(例如,多晶硅层);以及邻近该浮栅层的控制栅极层(例如,金属栅极层)。ctfet的栅极结构可为多层栅极结构,包括:邻近沟道区的栅极介电层;邻近该栅极介电层的电荷捕获层(例如,氮化硅层);以及邻近该电荷捕获层的控制栅极层(例如,金属栅极层)。

29.在任何情况下,在装置100内,nfet 110及pfet 120可分别具有分立的第一与第二栅极g1与g2,它们(例如,通过局部互连或通过接触与后端工艺线路的组合)电性连接。或者,如图2a-2c中所示,装置100可包括单个栅极结构145(在本文中称为针对该nfet及该pfet的共用栅极结构)。此单个栅极结构145(包括上述各栅极层)可横贯nfet 110的第一沟道区(c1)及pfet 120的第二沟道区(c2),以使nfet 110的第一栅极(g1)与pfet 120的第二栅极(g2)只是同一栅极结构的不同部分。

30.请一并参照图1及图2a-2c,所揭示的装置100的各实施例还可包括输入节点140、输出节点132、接地节点131、第一编程节点151(在本文中也称为nfet编程节点),以及第二编程节点152(在本文中也称为pfet编程节点)。输入节点140可位于电性连接(例如,若适用

的话,在单个栅极结构145上)的第一栅极(g1)与第二栅极(g2)之间的接合处。输出节点132可位于nfet 110的第一漏极区(d1)与pfet 120的第二源极区(s2)之间的接合处。接地节点(也就是,与地的连接)可位于nfet 110的第一源极区(s1)与pfet 120的第二漏极区(d2)之间的接合处。nfet编程节点151可位于nfet 110的第一本体(b1)(例如,经由bc1),且pfet编程节点152可位于该pfet的第二本体(b2)(例如,经由bc2)。

31.在装置100中,如上所述,可通过向输入节点140(也就是,向nfet 110及pfet 120的栅极(g1)与(g2))、向nfet编程节点151(也就是,向nfet 110的第一本体(b1))、以及向pfet编程节点152(也就是,向pfet 120的第二本体(b2))施加特定的一组电压条件来同时编程nfet 110及pfet 120的阈值电压。作为所述施加该特定组电压条件的结果,装置100将经编程(例如,配置、设置等)而操作于多种不同操作模式中的一种。也就是说,作为所述施加该特定组电压条件的结果,nfet 110及pfet 120将经编程而共同具有多个可能阈值电压组合中的一个特定阈值电压组合。依据此特定阈值电压组合,装置100将操作于多种可能操作模式(例如,倍频操作模式、正信号传输模式、信号阻挡模式、负信号传输模式等)中的一种特定操作模式。利用此配置,nfet 110及pfet 120的阈值电压可选择性地通过施加不同的一组电压条件来重新编程(例如,在现场),以在该两个fet中达到一个不同的特定阈值电压组合,并因此将该装置切换至该多种可能操作模式中的不同的一种操作模式。在任何情况下,当装置100操作于该多种不同操作模式中的特定一种时,装置100呈现多条不同的漏极电流-栅极电压曲线中的特定一条。也就是说,在各种不同的操作模式中,该装置呈现不同的漏极电流-栅极电压曲线。因此,装置100可针对不同的功能重新配置。

32.例如,nfet 110可为可编程的,以具有低正阈值电压(低正vt)或高于该低正阈值电压的高正阈值电压(高正vt)。pfet 120可为可编程的,以具有低负阈值电压(低负vt)或高于该低负阈值电压的高负阈值电压(高负vt)。应当理解,当电压量的绝对值较高时,一个负阈值电压高于另一个负阈值电压;当电压量的绝对值较低时,一个负阈值电压低于另一个负阈值电压。若nfet 110及pfet 120分别具有两个可编程阈值电压(如上所述),则可采用这两个fet的阈值电压的同时编程来重新配置装置100,以使其处于四种不同状态中的选定一种,从而使其操作于四种不同操作模式中的选定一种。这四种不同的装置状态可包括:第一状态,其中,nfet 110具有该低正阈值电压且pfet 120具有该低负阈值电压(例如,用于倍频模式);第二状态,其中,nfet 110具有该低正阈值电压且pfet 120具有该高负阈值电压(例如,用于正信号传输模式);第三状态,其中,nfet 110具有该高正阈值电压且pfet 120具有该高负阈值电压(例如,用于信号阻挡模式);以及第四状态,其中,nfet 110具有该高正阈值电压且pfet120具有该低负阈值电压(例如,用于负信号传输模式)。

33.应当理解,若nfet 110及pfet 120具有两个以上的可编程阈值电压,则可将装置100重新配置为用于四种以上不同操作模式的四种以上不同状态中的任意一种。例如,nfet 110还可具有超低正阈值电压且pfet 120可具有超低负阈值电压。在此情况下,装置100的额外状态可包括:第五状态,其中,nfet 110具有该超低正阈值电压且pfet120具有该超低负阈值电压(例如,用于替代信号传输模式);第六状态,其中,nfet 110具有该超低正阈值电压且pfet 120具有低负阈值电压;依此类推。

34.图3是显示可用以重新配置装置100的示例组电压条件的表格,该装置包括n型fefet 110及p型fefet 120,它们并联电性连接且具有电性连接的栅极。具体地说,此表格

显示可被施加于输入节点140(也就是,栅极(g1/g2))、nfet编程节点151(也就是,n型fefet110的第一本体(b1))、以及pfet编程节点152(也就是,p型fefet(120)的第二本体(b2))以达到上述装置状态及操作模式的示例电压条件。

35.例如,为重新配置装置100以使其处于用于倍频模式的第一装置状态,可将输入节点140放电至地,可向nfet编程节点151施加特定的负电压(例如,-4v),并可向pfet编程节点152施加对应的正电压(例如,+4v)。因此,该第一栅极(g1)的铁电层中的极化向量的方向将迫使电子进入该第一沟道区(c1)中,以确保n型fefet 110具有低正阈值电压。此外,该第二栅极(g2)的铁电层中的极化向量的方向将迫使空穴进入该第二沟道区(c2)中,以确保p型fefet 120具有低负阈值电压。图4a-1是显示该第一装置状态的负和正阈值电压曲线的图形,且图4a-2是包括针对图3的表格中所列出的且与该第三装置状态相关的倍频模式的漏极电流-栅极电压曲线、输入电压信号、以及输出电流信号的图形。如图4a-2中所示,此第一装置状态使漏极电流-栅极电压曲线的抛物线部分倍频两倍。此例具体说明所揭示的装置100如何在不需要大量芯片空间或功率的情况下实现倍频。因此,此类装置100可为用于需要稳定的高频振荡的无线通信系统中的最佳解决方案。

36.为重新配置装置100以使其处于用于正信号传输模式的第二装置状态,可将输入节点140放电至地,可向nfet编程节点151施加特定的负电压(例如,-4v),并可向pfet编程节点152施加相同的负电压(例如,-4v)。因此,该第一栅极(g1)的铁电层中的极化向量的方向将迫使电子进入该第一沟道区(c1)中,以确保n型fefet 110具有低正阈值电压。然而,该第二栅极(g2)的铁电层中的极化向量的方向将迫使空穴离开该第二沟道区(c2),以确保p型fefet 120具有高负阈值电压。图4b-1是显示该第二装置状态的负和正阈值电压曲线的图形,且图4b-2是包括针对图3的表格中所列出的且与该第三装置状态相关的正信号传输模式的漏极电流-栅极电压曲线、输入电压信号、以及输出电流信号的图形。如图所示,此第二装置状态有助于阻挡负信号部分且仅传输正信号部分。

37.为重新配置装置100以使其处于用于信号阻挡模式的第三装置状态,可将输入节点140放电至地,可向nfet编程节点151施加特定的正电压(例如,+4v),并可向pfet编程节点152施加对应的负电压(例如,-4v)。因此,该第一栅极(g1)的铁电层中的极化向量的方向将迫使电子离开该第一沟道区(c1),以确保n型fefet 110具有高正阈值电压。该第二栅极(g2)的铁电层中的极化向量的方向将迫使空穴离开该第二沟道区(c2),以确保p型fefet 120具有高负阈值电压。图4c-1是显示该第三装置状态的负正阈值电压曲线的图形,且图4c-2是包括针对图3的表格中所列出的且与该第三装置状态相关的信号阻挡模式的漏极电流-栅极电压曲线、输入电压信号、以及输出电流信号的图形。如图所示,该第三装置状态有助于阻挡正和负信号部分。

38.为重新配置装置100以使其处于负信号传输模式的第四装置状态,可将输入节点140放电至地,可向nfet编程节点151施加特定的正电压(例如,+4v),并可向pfet编程节点152施加相同的正电压(例如,+4v)。因此,该第一栅极(g1)的铁电层中的极化向量的方向将迫使电子离开该第一沟道区(c1),以确保n型fefet 110具有高正阈值电压。不过,该第二栅极(g2)的铁电层中的极化向量的方向将迫使空穴进入该第二沟道区(c2)中,以确保p型fefet 120具有低负阈值电压。图4d-1是显示该第四装置状态的负和正阈值电压曲线的图形,且图4d-2是包括针对图3的表格中所列出的且与该第四装置状态相关的负信号传输模

式的漏极电流-栅极电压曲线、输入电压信号、以及输出电流信号的图形。如图所示,该第四装置状态有助于阻挡正信号部分且仅传输负信号部分。

39.如上所述,n型fefet 110及p型fefet 120可具有两个以上可能的可编程阈值电压。例如,n型fefet还可具有超低正阈值电压且p型fefet还具有超低负阈值电压。在此情况下,为重新配置装置100以使其处于用于替代传输模式的第五装置状态,可将输入节点140放电至地,可向nfet编程节点151施加特定的高负电压(也就是,与用于该第一状态的负电压相比较高的负电压,例如,-5v),且可向pfet编程节点152施加对应的高正电压(例如,+5v)。因此,该第一栅极(g1)的铁电层中的极化向量的方向将迫使电子进入该第一沟道区(c1)中,以确保n型fefet 110具有超低正阈值电压。此外,该第二栅极(g2)的铁电层中的极化向量的方向将迫使空穴进入该第二沟道区(c2)中,以确保p型fefet 120具有超低负阈值电压。图4e-1是显示该第五装置状态的负和正阈值电压曲线的图形,且图4e-2是包括用于图3的表格中所列出的且与该第五装置状态相关的替代传输模式的漏极电流-栅极电压曲线、输入电压信号、以及输出电流信号的图形。如图所示,此第五状态支持沿该漏极电流-栅极电压曲线的线性部分的信号传输。此例具体说明可通过不同的编程/擦除电压访问该漏极电流-栅极电压曲线的不同部分。

40.应当理解,对于装置100包括不同类型的阈值电压可编程fet(例如,fgfet或ctfet,而不是fefet)的实施例,将采用不同组的电压条件来同时编程nfet 110及pfet 120,从而重新配置装置100。这是因为在fgfet及ctfet中实现阈值电压编程的机制不同于在fefet中实现阈值电压编程的机制。

41.请参照图5的流程图,本文中还揭示形成可重新配置的互补金属氧化物半导体(cmos)装置的方法的实施例。该方法可包括提供半导体衬底(参见工艺步骤502)。该半导体衬底可为块体半导体衬底(例如,块体硅衬底)。或者,该半导体衬底可为绝缘体上半导体(例如,绝缘体上硅(soi)衬底)。

42.该方法还可包括在该半导体衬底上形成可重新配置的互补金属氧化物半导体(cmos)装置(参见工艺步骤504)。具体地说,可利用传统的cmos处理技术在工艺步骤504形成可重新配置的cmos装置100,只不过在工艺步骤504所使用的特定前端工艺(front-end-of-the-line;feol)、中间工艺(middle-of-the-line;mol),以及后端工艺(back-end-of-the-line;beol)cmos处理步骤应经执行以形成例如图1及2a-2c中所示的且包括互补的一对场效应晶体管(fet)(也就是,n型fet 110(nfet)及p型fet 120(pfet))的新颖的可重新配置的cmos装置100,该对fet为阈值电压可编程fet,并联电性连接,并具有电性连接的栅极。

43.更具体地说,nfet 110可经形成以具有第一本体区(b1)(例如,p-本体区)(例如,由浅沟槽隔离(sti)区205定义),以及在该第一本体区(b1)中,横向位于第一源极区(s1)(例如,n+源极区)与第一漏极区(d1)(例如,n+漏极区)之间的第一沟道区(c1)(例如,p-沟道区)。可选地,nfet 110可经形成从而还具有,在该第一本体区(b1)中,(例如,通过sti区205)与该第一源极区(s1)及该第一漏极区(d1)电性隔离的第一本体接触区(bc1)(例如,p+区)。该第一本体接触区(bc1)可促进在装置编程期间接触该第一本体区(b1),如下面更详细讨论。可邻近该第一沟道区(c1)形成第一栅极(g1)。同时,pfet 120可经形成以具有第二本体区(b2)(例如,n-本体区),以及在该第二本体区(b2)中,横向位于第二源极区(s2)(例

如,p+源极区)与第二漏极区(d2)(例如,p+漏极区)之间的第二沟道区(c2)(例如,n-沟道区)。可选地,pfet 120还可经形成以具有,在该第二本体区(b2)中,(例如,通过sti区205)与该第二源极区(s2)及该第二漏极区(d2)电性隔离的第二本体接触区(bc2)(例如,n+区域)。该第二本体接触区(bc2)可促进在装置编程期间接触该第二本体区(b2),如下面更详细讨论。可邻近该第二沟道区(c2)形成第二栅极(g2)。

44.如图所示,nfet 110及pfet 120可形成为平面fet。或者,nfet110及pfet 120可形成为非平面fet(未显示)。

45.nfet 110及pfet 120还可经形成以使它们为阈值电压可编程fet。本领域的技术人员将意识到,nfet 110及pfet 120的第一及第二栅极(g1/g2)的配置将分别依赖于所形成的阈值电压可编程fet的类型。例如,fefet的栅极结构可经形成以至少包括:邻近沟道区的铁电层147(例如,氧化铪层或某种其它合适的铁电层);以及位于铁电层147上的金属栅极层148(例如,如图2b及2c中所示)。可选地,fefet的栅极结构可经形成从而还包括堆叠于沟道区与铁电层147之间的较薄栅极绝缘体层146(例如,二氧化硅层或其它合适的绝缘体层)(如图所示),以及/或者额外的金属栅极层,从而铁电层147被夹置于两个金属栅极层之间(未显示)。在形成不同类型的阈值电压可编程fet(例如,fgfet或ctfet)的替代实施例(未显示)中,栅极结构将不同。例如,fgfet的栅极结构可经形成以包括:邻近沟道区的栅极介电层;邻近该栅极介电层的浮栅层(例如,多晶硅层);以及邻近该浮栅层的控制栅极层(例如,金属栅极层)。ctfet的栅极结构可经形成以包括:邻近沟道区的栅极介电层;邻近该栅极介电层的电荷捕获层(例如,氮化硅层);以及邻近该电荷捕获层的控制栅极层(例如,金属栅极层)。

46.应当注意,该第一及第二栅极g1及g2可形成为分立的栅极,并随后电性连接(例如,通过局部互连或通过接触及后端工艺线路的组合)。或者,如图2a-2c中所示,单个栅极结构横跨nfet 110的第一沟道区(c1)与pfet 120的第二沟道区(c2),以使nfet 110的第一栅极(g1)与pfet 120的第二栅极(g2)只是同一栅极结构的不同部分。

47.最后,可形成局部互连及/或接触与后端工艺线路的组合,以并联电性连接nfet 110与pfet 120,且若必要,电性连接栅极。也就是说,nfet 110的第一漏极区(d1)可与pfet 120的第二源极区(s2)电性连接(例如,通过局部互连或通过接触与后端工艺线路的组合)。而且,nfet 110的第一源极区(s1)可与pfet 120的第二漏极区(d2)电性连接(例如,通过局部互连或通过接触与后端工艺线路的组合)。可形成额外的接触及后端工艺线路,以便于访问以下节点:位于该第一栅极(g1)与该第二栅极(g2)之间的接合处的输入节点140;位于nfet 110的第一漏极区(d1)与pfet 120的第二源极区(s2)之间的接合处的输出节点132;位于nfet 110的第一源极区(s1)与pfet120的第二漏极区(d2)之间的接合处的接地节点(也就是,与地连接);位于nfet 110的第一本体(b1)的nfet编程节点151;以及位于pfet 120的第二本体(b2)的pfet编程节点152。

48.请参照图6的流程图,本文中还揭示用于重新配置(在本文中也称为编程)如上面详细所述的可重新配置的互补金属氧化物半导体(cmos)装置100的方法的实施例。该方法可包括提供可重新配置的cmos装置100(参见工艺步骤602)。此可重新配置的cmos装置100可例如位于用于无线通信系统的集成电路(ic)芯片上或某种其它ic芯片上。该方法还可包括同时编程装置100的nfet 110及pfet 120的阈值电压,以重新配置装置100,尤其,用以初

始设置或随后将该装置切换至多种可能操作模式中的特定一种(参见工艺步骤604)。

49.更具体地说,如上所述并如图1及2a-2c中所示,装置100可包括位于电性连接(例如,在单个栅极结构145上,若适用的话)的该第一栅极(g1)与该第二栅极(g2)之间的接合处的输入节点140。装置100还可包括位于nfet 110的第一本体(b1)的nfet编程节点151以及位于pfet的第二本体(b2)的pfet编程节点152。在工艺步骤604,可通过向输入节点140(也就是,向nfet 110及pfet 120的栅极(g1)及(g2))、向nfet编程节点151(也就是,向nfet 110的第一本体(b1))、以及向pfet编程节点152(也就是,向pfet 120的第二本体(b2))施加特定的一组电压条件来同时编程nfet 110及pfet 120的阈值电压。作为所述施加该特定组电压条件的结果,装置100将经编程(例如,重新配置、设置等)以操作于多种不同操作模式中的选定一种。也就是说,作为所述施加该特定组电压条件的结果,nfet 110及pfet 120将经编程而共同具有多个可能阈值电压组合中的一个特定阈值电压组合。依据fet 110及120中的此特定阈值电压组合,装置100将操作于多种可能操作模式(例如,倍频操作模式、正信号传输模式、信号阻挡模式、负信号传输模式等)中的一种特定操作模式。

50.例如,nfet 110可为可编程的,以具有低正阈值电压(低正vt)或高正阈值电压(高正vt)。pfet 120可为可编程的,以具有低负阈值电压(低负vt)或高负阈值电压(高负vt)。在此情况下,可在工艺步骤604重新配置装置100,以使其具有四种不同装置状态中的选定一种,从而使其操作于四种不同操作模式中的选定一种。这四种不同的装置状态可包括:第一状态,其中,nfet 110具有该低正阈值电压且pfet 120具有该低负阈值电压(例如,用于倍频模式);第二状态,其中,nfet 110具有该低正阈值电压且pfet 120具有该高负阈值电压(例如,用于正信号传输模式);第三状态,其中,nfet 110具有该高正阈值电压且pfet 120具有该高负阈值电压(例如,用于信号阻挡模式);以及第四状态,其中,nfet 110具有该高正阈值电压且pfet120具有该低负阈值电压(例如,用于负信号传输模式)。

51.应当理解,若nfet 110及pfet 120具有两个以上的可编程阈值电压,则装置100可具有四种以上不同的装置状态,并因此具有四种以上不同的操作模式。例如,nfet 110还可具有超低正阈值电压且pfet 120可具有超低负阈值电压。在此情况下,额外装置状态可包括:第五状态,其中,nfet 110具有该超低正阈值电压且pfet 120具有该超低负阈值电压(例如,用于替代信号传输模式);第六状态,其中,nfet 110具有该超低正阈值电压且pfet 120具有低负阈值电压;依此类推。

52.图3是显示可用以重新配置装置100的示例组电压条件的表格,该装置包括n型fefet 110及p型fefet 120,它们并联电性连接并具有电性连接的栅极。具体地说,此表格显示可被施加于输入节点140(也就是,栅极(g1/g2))、nfet编程节点151(也就是,n型fefet110的第一本体(b1))、以及pfet编程节点152(也就是,p型fefet(120)的第二本体(b2))以达到上述装置状态及操作模式的示例电压条件。

53.例如,在工艺步骤604,为重新配置装置100以使其处于用于倍频模式的第一装置状态,可将输入节点140放电至地,可向nfet编程节点151施加特定的负电压(例如,-4v),并可向pfet编程节点152施加对应的正电压(例如,+4v)。因此,该第一栅极(g1)的铁电层中的极化向量的方向将迫使电子进入该第一沟道区(c1)中,以确保n型fefet 110具有低正阈值电压。此外,该第二栅极(g2)的铁电层中的极化向量的方向将迫使空穴进入该第二沟道区(c2)中,以确保p型fefet 120具有低负阈值电压。如图4a-1及4a-2所示,此第一装置状态使

漏极电流-栅极电压曲线的抛物线部分倍频两倍。此例具体说明所揭示的方法如何在不需要大量芯片空间或功率的情况下实现倍频。

54.在工艺步骤604,为重新配置装置100以使其处于用于正信号传输模式的第二装置状态,可将输入节点140放电至地,可向nfet编程节点151施加特定的负电压(例如,-4v),并可向pfet编程节点152施加相同的负电压(例如,-4v)。因此,该第一栅极(g1)的铁电层中的极化向量的方向将迫使电子进入该第一沟道区(c1)中,以确保n型fefet 110具有低正阈值电压。然而,该第二栅极(g2)的铁电层中的极化向量的方向将迫使空穴离开该第二沟道区(c2),以确保p型fefet 120具有高负阈值电压。如图4b-1及4b-2所示,此第二装置状态有助于阻挡负信号部分且仅传输正信号部分。

55.在工艺步骤604,为重新配置装置100以使其处于用于信号阻挡模式的第三装置状态,可将输入节点140放电至地,可向nfet编程节点151施加特定的正电压(例如,+4v),并可向pfet编程节点152施加对应的负电压(例如,-4v)。因此,该第一栅极(g1)的铁电层中的极化向量的方向将迫使电子离开该第一沟道区(c1),以确保n型fefet 110具有高正阈值电压。该第二栅极(g2)的铁电层中的极化向量的方向将迫使空穴离开该第二沟道区(c2),以确保p型fefet120具有高负阈值电压。如图4c-1及4c-2所示,该第三装置状态有助于阻挡正和负信号部分。

56.在工艺步骤604,为重新配置装置100以使其处于负信号传输模式的第四装置状态,可将输入节点140放电至地,可向nfet编程节点151施加特定的正电压(例如,+4v),并可向pfet编程节点152施加相同的正电压(例如,+4v)。因此,该第一栅极(g1)的铁电层中的极化向量的方向将迫使电子离开该第一沟道区(c1),以确保n型fefet 110具有高正阈值电压。不过,该第二栅极(g2)的铁电层中的极化向量的方向将迫使空穴进入该第二沟道区(c2)中,以确保p型fefet 120具有低负阈值电压。如图4d-1及4d-2所示,该第四装置状态有助于阻挡正信号部分且仅传输负信号部分。

57.如上所述,n型fefet 110及p型fefet 120可具有两个以上可能的可编程阈值电压。例如,n型fefet还可具有超低正阈值电压且p型fefet还具有超低负阈值电压。在此情况下,在工艺步骤604,为重新配置装置100以使其处于第五装置状态(例如,用于替代传输模式),可将输入节点140放电至地,可向nfet编程节点151施加特定的高负电压(也就是,与用于该第一状态的负电压相比较高的负电压,例如,-5v),且可向pfet编程节点152施加对应的高正电压(例如,+5v)。因此,该第一栅极(g1)的铁电层中的极化向量的方向将迫使电子进入该第一沟道区(c1)中,以确保n型fefet 110具有超低正阈值电压。此外,该第二栅极(g2)的铁电层中的极化向量的方向将迫使空穴进入该第二沟道区(c2)中,以确保p型fefet 120具有超低负阈值电压。如图4e-1及4e-2所示,此第五装置状态支持沿该漏极电流-栅极电压曲线的线性部分的信号传输。此例说明可通过不同的编程/擦除电压访问该漏极电流-栅极电压曲线的不同部分。

58.可选地,该方法还可包括通过施加不同的一组电压条件来同时重新编程nfet 110及pfet 120的阈值电压(例如,若必要,在现场的任何时间),以在该两个fet 110、120中达到一个不同的特定阈值电压组合,并因此将装置100切换至该多种可能操作模式中的不同的一种操作模式。

59.此外,应当理解,在上述方法及结构中,半导体材料是指导电属性可通过掺杂杂质

而改变的材料。示例半导体材料包括例如硅基半导体材料(例如,硅、硅锗、碳化锗硅、碳化硅等)以及iii-v族化合物半导体(也就是,通过将第iii族元素例如铝(al)、镓(ga)、铟(in)与第v族元素例如氮(n)、磷(p)、砷(as)、锑(sb)组合来获得的化合物)(例如,gan、inp、gaas或gap)。纯半导体材料,尤其不掺杂用于增加导电性的杂质的半导体材料(也就是,未掺杂半导体材料)在本领域中被称为本征半导体。掺杂有用于增加导电性的杂质的半导体材料(也就是,掺杂半导体材料)在本领域中被称为非本征半导体,并且会比由相同的基材制成的本征半导体更加导电。也就是说,非本征硅将比本征硅更导电;非本征硅锗将比本征硅锗更导电,依此类推。而且,应当理解,可使用不同的杂质(也就是,不同的掺杂物)来达到不同的导电类型(例如,p型导电性及n型导电性),且掺杂物可依据所使用的不同半导体材料而变化。例如,通常用第iii族掺杂物例如硼(b)或铟(in)掺杂硅基半导体材料(例如,硅、硅锗等),以达到p型导电性,通常用第v族掺杂物例如砷(as)、磷(p)或锑(sb)掺杂硅基半导体材料,以达到n型导电性。通常用镁(mg)掺杂氮化镓(gan)基半导体材料,以达到p型导电性,或用硅(si)或氧气掺杂,以达到n型导电性。本领域的技术人员还将意识到,不同的导电水平将依赖于给定半导体区中的掺杂物的相对浓度水平。

60.上述方法用于集成电路芯片的制造。制造者可以原始晶圆形式(例如,作为具有多个未封装芯片的单个晶圆)、作为裸芯片,或者以封装形式分配所得的集成电路芯片。在后一种情况中,该芯片设于单芯片封装件中(例如塑料承载件,其具有附着至母板或其它更高层次承载件的引脚)或者多芯片封装件中(例如陶瓷承载件,其具有表面互连或嵌埋互连或者两者都具有)。在任何情况下,接着将该芯片与其它芯片、分立电路元件和/或其它信号处理装置集成,作为(a)中间产品例如母板的部分,或者作为(b)最终产品的部分。该最终产品可为包括集成电路芯片的任意产品,涉及范围从玩具及其它低端应用直至具有显示器、键盘或其它输入装置以及中央处理器的先进电脑产品。

61.应当理解,本文中所使用的术语是出于说明所揭示的结构及方法的目的,并非意图限制。例如,除非上下文中另外明确指出,否则这里所使用的单数形式“一个”以及“该”也意图包括复数形式。另外,本文中所使用的术语“包括”表明所述特征、整数、步骤、操作、元件和/或组件的存在,但不排除存在或添加一个或多个其它特征、整数、步骤、操作、元件、组件,和/或其群组。而且,本文中所使用的术语例如“右”、“左”、“垂直”、“水平”、“顶部”、“底部”、“上方”、“下方”、“平行”、“垂直”等意图说明当它们以附图中取向并显示时的相对位置(除非另外指出),且术语如“碰触”、“直接接触”、“毗邻”、“直接相邻”、“紧邻”等意图表示至少一个元件物理接触另一个元件(没有其它元件隔开所述元件)。本文中所使用的术语“横向”说明当元件以附图中取向并显示时该些元件的相对位置,尤其表示一个元件位于另一个元件的侧边而不是另一个元件的上方或下方。例如,一个元件横向邻近另一个元件将在该另一个元件旁边,一个元件横向紧邻另一个元件将直接在该另一个元件旁边,以及一个元件横向围绕另一个元件将邻近并环绕该另一个元件的外侧壁。下面的权利要求中的所有手段功能用语或步骤功能用语元素的对应结构、材料、动作及等同意图包括执行该功能的任意结构、材料或动作结合具体请求保护的其它请求保护的元素。

62.对本发明的各种实施例所作的说明是出于示例说明的目的,而非意图详尽无遗或限于所揭示的实施例。许多修改及变更将对于本领域的普通技术人员显而易见,而不背离所述实施例的范围及精神。本文中所使用的术语经选择以最佳解释所述实施例的原理、实

际应用或在市场已知技术上的技术改进,或者使本领域的普通技术人员能够理解本文中所揭示的实施例。

63.因此,上面揭示具有多种不同操作模式(包括但不限于倍频模式)的可重新配置的互补金属氧化物半导体(cmos)装置的实施例。该装置可包括n型场效应晶体管(nfet)及p型场效应晶体管(pfet),它们是阈值电压可编程的,并联连接,并具有电性连接的栅极。利用此配置,可同时编程该nfet及pfet的阈值电压,并可依据在编程期间在该nfet及pfet中获得的阈值电压的特定组合来设置该装置的操作模式。例如,若nfet具有低正阈值电压且pfet具有低负阈值电压,则该装置可操作于倍频模式。此外,根据需要,可同时重新编程该nfet及pfet的阈值电压(例如,在现场),以切换该装置的操作模式。这样的装置可较小(也就是,可消耗最小量的芯片面积),并可以最小的功耗实现倍频及其它功能。上面还揭示用于形成该装置的方法的实施例以及用于重新配置该装置的方法的实施例(也就是,用于同时编程该nfet及pfet,以设置或切换操作模式)。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1