半导体封装结构的制作方法

1.本发明涉及半导体技术领域,更具体地,涉及一种半导体封装结构。

背景技术:

2.随着半导体封装技术的演进,各式各样的封装结构亦推陈出新,整体封装尺寸也越来越小,功能也越来越多。故通常需要一个能够控制各种元件的功率封装件(power package)。在某种程度上,基板型嵌入式封装(semiconductor embedded in substrate,sesub)是封装产业未来必定会走向元件的整合趋势。

3.现行sesub制程中,在形成微通孔(micro via)的喷砂制程中,发现会有由断开(open)造成电性断开的问题。如图1所示,这主要是由于管芯10上方的树脂材料20的厚度过厚,造成预设的喷砂制程不足以将开孔12打开至管芯10。然而造成管芯10上方的树脂材料20厚度过厚的主要原因是来自制程的误差(deviation)、以及树脂材料20本身的误差。

技术实现要素:

4.针对相关技术中的上述问题,本发明提出一种半导体封装结构,能够确保通孔能够与电子元件之间的电性连接。

5.根据本发明实施例的一个方面,提供了一种半导体封装结构,包括基板和内埋于基板中的第一电子元件,基板具有第一导电通孔,第一导电通孔与第一电子元件电连接,其中,第一导电通孔与第一电子元件物理地分隔开。

6.在一些实施例中,第一导电通孔的下表面与第一电子元件物理地分隔开。

7.在一些实施例中,基板包括覆盖第一电子元件的介电层,第一导电通孔与第一电子元件是由介电层分隔开。

8.在一些实施例中,第一电子元件的邻近第一导电通孔的表面上设置有导电柱,导电柱从第一电子元件延伸至第一导电通孔内。

9.在一些实施例中,第一导电通孔部分地暴露导电柱。

10.在一些实施例中,上述半导体封装结构还包括:第三电子元件,设置于基板上并与第一电子元件电连接;模塑料,覆盖在第三电子元件和基板上方。

11.在一些实施例中,基板还具有第二导电通孔,第一导电通孔与第二导电通孔的深度不相等。

12.在一些实施例中,第一导电通孔与第二导电通孔的上表面不等高。

13.在一些实施例中,第二导电通孔与第一电子元件物理接触和电连接。

14.在一些实施例中,上述半导体封装结构还包括:第二电子元件,内埋于基板内;第二导电通孔与第二电子元件物理接触和电连接。

15.本发明的上述技术方案,通过在第一电子元件上设置导电柱,可以补偿介电层压合的厚度误差。具体来说,由于导电柱的误差值小于介电层压合的误差值,故可达到补偿效果,当第一导电通孔的深度不足以达到第一电子元件时,仍可以确保第一导电通孔能够与

第一电子元件电连接。

附图说明

16.当结合附图进行阅读时,从以下详细描述可最佳理解本发明的各个方面。应当注意,根据工业中的标准实践,各个部件并非按比例绘制。事实上,为了清楚讨论,各个部件的尺寸可以任意增大或减小。

17.图1是现有半导体封装结构的开孔的示意图。

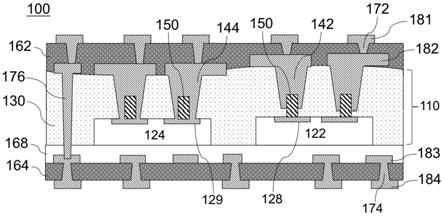

18.图2是根据本发明实施例的半导体封装结构的示意图。

19.图3是根据本发明另一实施例的半导体封装结构的示意图。

20.图4至图7是根据本发明实施例的形成半导体封装结构的方法的多个阶段的示意图。

具体实施例

21.下列公开提供了许多用于实现所提供主题的不同特征的不同实施例或实例。下面将描述元件和布置的特定实例以简化本发明。当然这些仅仅是实例并不旨在限定本发明。例如,在以下描述中,在第二部件上方或上形成第一部件可以包括第一部件和第二部件直接接触的实施例,也可以包括在第一部件和第二部件之间形成额外的部件使得第一部件和第二部件可以不直接接触的实施例。而且,本发明在各个实例中可重复参考数字和/或字母。这种重复仅是为了简明和清楚,其自身并不表示所论述的各个实施例和/或配置之间的关系。

22.图2是根据本发明实施例的半导体封装结构的示意图。在图2所示的封装结构100中,包括基板110和内埋于基板110中的第一电子元件122。基板110中具有第一导电通孔142,第一导电通孔142与第一电子元件122电连接。并且,第一导电通孔142与第一电子元件122物理地分隔开,即第一导电通孔142与第一电子元件122不直接接触。如图2所示,第一导电通孔142的下表面与第一电子元件122物理地分隔开。

23.基板110包括覆盖第一电子元件122的介电层130。在一些实施例中,介电层130的材料包括但不限于树脂材料、聚酰亚胺(pi)或聚丙烯(pp)。介电层130填充在第一导电通孔142的下表面与第一电子元件122之间,使得第一导电通孔142与第一电子元件122由介电层130分隔开。

24.第一电子元件122的邻近第一导电通孔142的上表面上设置有导电柱150。导电柱150可以设置在第一电子元件122的上表面处的焊盘128上。导电柱150从第一电子元件122的焊盘128延伸至第一导电通孔142内。导电柱150从第一电子元件122延伸至第一导电通孔142内,使得第一导电通孔142包覆导电柱150的上表面和上部分侧壁并暴露导电柱150的下部分侧壁,以通过导电柱150将第一电子元件122与第一导电通孔142电连接。

25.在一些实施例中,导电柱150的材料可以是铜。在一些实施例中,导电柱150的宽度可以在40μm至200μm的范围内,例如可以在50μm至60μm的范围内。在一些实施例中,导电柱150的高度可以在3μm至200μm的范围内,例如可以在10μm至15μm的范围内。

26.本发明的上述技术方案,通过在第一电子元件122上设置导电柱150,可以补偿介电层130压合的厚度误差。具体的,由于导电柱150的误差值小于介电层130压合的误差值,

故可以达到补偿效果,当第一导电通孔142的深度不足以达到第一电子元件122时,仍可以确保第一导电通孔142能够与第一电子元件122电连接。

27.继续参考图2所示,封装结构100还包括内埋于基板110内的第二电子元件124,介电层130也覆盖第二电子元件124。

28.基板110内还可以具有与第一导电通孔142的深度不相等的第二导电通孔。第二导电通孔也可以与第一导电通孔142不等高。在一些实施例中,与第一导电通孔142的深度不相等的第二导电通孔可以是与第一电子元件122物理接触和电连接的通孔。在又一些实施例中,第二导电通孔可以是与第二电子元件124物理接触和电连接的第二导电通孔144。介电层130上方覆盖有覆铜箔层压板(copper clad laminate,ccl)层162。第一电子元件122和第二电子元件124下方设置有另一ccl层164。第一电子元件122和第二电子元件124通过附接层168附接至下方的ccl层164。在一些实施例中,附接层168的材料可以与介电层130的材料相同或不同。

29.ccl层162上具有第一线路层181。介电层130上设置有第二线路层182。上方的ccl层162内具有互连第一线路层181和第二线路层182的通孔172。第一导电通孔142和第二导电通孔144分别将第一电子元件122和第二电子元件124与第二线路层182电连接。下方的ccl层164上方具有三线路层183,ccl层164下方具有四线路层184。基板110内具有穿过介电层130和附接层168而互连第二线路层182和第三线路层183的贯通孔176。下方的ccl层164内具有互连第三线路层183和第四线路层184的通孔174。

30.在一些实施例中,第一电子元件122和第二电子元件124上覆盖的介电层130的厚度可以是不同的,介电层130的上表面即为基板110的上表面,因此基板110的上表面是不平坦的。第一导电通孔142与第二导电通孔144的深度可以不相等的。第一导电通孔142与第二导电通孔144的下表面不等高。第一导电通孔142与第二导电通孔144的上表面不等高。在一些实施例中,该第二导电通孔144也可能设置于第一电子组件122上,故第一电子组件122可能具有深度不相等的第一导电通孔142与第二导电通孔144,其中第一导电通孔142与第二导电通孔144的下表面不等高。第一导电通孔142与第二导电通孔144的上表面不等高。

31.在一些实施例中,第一电子元件122上方的介电层130的厚度比第二电子元件124上方的介电层130厚,并且第一导电通孔142未延伸达到第一电子元件122而与第一电子元件122不直接接触。第二电子元件124上方的介电层130的厚度较薄,第二导电通孔144可以达到第二电子元件124而与第二电子元件124物理接触。

32.第二电子元件124的邻近第二导电通孔144的上表面上也设置有导电柱150。导电柱150可以设置在第二电子元件124的上表面处的焊盘129上。第二电子元件124上方的导电柱150从第二电子元件124的焊盘129延伸至第二导电通孔144内。第一导电通孔142包覆导电柱150的上表面和全部侧壁。

33.图3是根据本发明实施例的半导体封装结构的示意图。在图3所示的实施例中,基板110上方还设置有第三电子元件126。第三电子元件126与第一电子元件122电连接。第三电子元件126可以是主动元件,或者也可以是被动元件。第三电子元件126可以通过通孔172和第一导电通孔142与第一电子元件122电连接。模塑料(molding compound)190覆盖在第三电子元件126和基板110上方。在一些实施例中,模塑料190的材料可以具体为环氧树脂模塑料(epoxy molding compound)。图3示出了第三电子元件126位于基板110上方。在其他实

施例中,也可以将第三电子元件126设置在基板110下方并电连接至第一电子元件122。在其他实施例中,还可以在基板110上方或下方设置电连接至第二电子元件124的另外的电子元件。图2所示实施例的其他方面,可以与图2所示的实施例类似,此处不再重复描述。

34.本发明的实施例还提供了形成半导体封装结构的方法。图4至图7是根据本发明实施例的形成半导体封装结构的方法的多个阶段的示意图。

35.首先参考图4所示,提供载体302,并在载体302上形成ccl层164和位于ccl层164上的线路层183。通过附接层168将第一电子元件122和第二电子元件124附接至ccl层164。第一电子元件122和第二电子元件124的具有焊盘128、129的表面朝上。其中,第一电子元件122和第二电子元件124的焊盘128、129上均设置有突出的导电柱150。介电层130形成在附接层168上并包覆第一电子元件122、第二电子元件124及其上方的导电柱150。

36.如图4所示,介电层130的上表面是不平坦的。第一电子元件122和第二电子元件124上覆盖的介电层130的厚度可以不同。在所示的实施例中,第一电子元件122上方的介电层130的厚度比第二电子元件124上方的介电层130厚。

37.然后如图5所示,在介电层130中形成位于第一电子元件122上方的第一开孔148和位于第二电子元件124上方的第二开孔149。在一些实施例中,可以利用喷砂制程或激光镭射制程来形成第一开孔148和第二开孔149。由于第一电子元件122上方的介电层130的厚度比第二电子元件124上方的介电层130厚,所以当第二电子元件124上方的第二开孔149达到第二电子元件124时,第一电子元件122上方的第一开孔148未穿过介电层130而到达第一电子元件122。第一开孔148的底面与第二开孔149的底面不等高,第一开孔148的底面高于开孔149的底面。第二开孔149可以暴露第二电子元件124的部分焊盘129,并且第二开孔149暴露第二电子元件124上的导电柱150的全部侧壁。第一开孔148未暴露第一电子元件122的焊盘128,第一开孔148的底面与第一电子元件122的焊盘128之间具有介电层130。第一开孔148可以暴露第一电子元件122上的导电柱150的上表面和上部分侧壁。

38.如图6所示,分别在第一开孔148和第二开孔149内形成第一导电通孔142和第二导电通孔144。此外,还可以形成穿过介电层130和附接层168的贯通孔176。在介电层130的上表面上形成与第一导电通孔142、第二导电通孔144和贯通孔176连接的第二线路层182,再形成覆盖介电层130和第二线路层182的ccl层162。

39.所形成的第一导电通孔142包覆第一电子元件122上的导电柱150的上表面和侧壁的上部,因此可以通过导电柱150电连接第一电子元件122与第一导电通孔142。第二导电通孔144包覆第二电子元件124上的导电柱150的上表面和全部侧壁。

40.如图7所示,去除载体302,形成穿过ccl层162、164的通孔172、174。再在ccl层162的上表面处和ccl层164的下表面处分别形成线路层181、184,从而形成最终的封装结构。此外,在未示出的实施例中,在形成线路层181、184之后,还可以在ccl层162上形成与第一电子元件122电连接的第三电子元件以及覆盖第三电子元件的模塑料(如参考图3所描述的)。

41.本发明的上述方法,通过在第一电子元件122上设置导电柱150,可以补偿介电层130压合的厚度误差。当第一导电通孔142的深度不足以达到第一电子元件122时,仍可以确保第一导电通孔142能够与第一电子元件122电连接。使得操作窗口(working window)增大,良率也可以上升。另外,通过设置导电柱,可以减少喷砂制程的喷砂次数。即可以用较少的喷砂次数完成开孔,孔径会较小。如果后续制程要改用激光镭射制程来开孔,由于铜厚增

加,所以亦可达成激光镭射制程。

42.上述内容概括了几个实施例的特征使得本领域技术人员可更好地理解本公开的各个方面。本领域技术人员应该理解,可以很容易地使用本发明作为基础来设计或更改其他的处理和结构以用于达到与本发明所介绍实施例相同的目的和/或实现相同优点。本领域技术人员也应该意识到,这些等效结构并不背离本发明的精神和范围,并且在不背离本发明的精神和范围的情况下,可以进行多种变化、替换以及改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1