功率变换器,以及电感结构的制作方法

1.本发明涉及一种半导体技术,更具体地说,涉及一种功率变换器,以及一种电感结构。

背景技术:

2.大电流多路并联结构,已经成为给cpu,服务器等供电的电压调节模组(voltage regulator module,vrm)电路的主要结构。而使用的电感多为多个铁氧体电感并排使用。但是铁氧体电感的由于其磁芯饱和磁通密度较低,热导率低导致其无法实现体积更小的设计。且多路铁氧体电感并排使用时,当某一路负载突然发生变化时,其他各路对此感知很慢不容易实现各支路之间的均流。

技术实现要素:

3.有鉴于此,本发明提供了一种功率变换器以及一种电感结构,以解决上述问题。

4.根据本发明的第一方面,提供一种功率变换器,其特征在于,包括:一电感结构,包括,第一至第n路电感线圈,和一个耦合线圈;每一路所述电感线圈和相应的晶体管组成一功率级电路,以在所述功率级电路的输出端产生输出信号;所述耦合线圈和每一路所述电感线圈成负耦合关系。

5.优选地,所述耦合线圈和所述电感线圈之间的耦合关系强于任意两路所述电感线圈之间的耦合关系。

6.优选地,任意两路所述电感线圈之间成负耦合关系,并且,所述耦合线圈和所述电感线圈之间的耦合系数大于任意两路所述电感线圈之间的耦合系数。

7.优选地,每一所述功率级电路的输入端接收同一输入电压源,每一所述功率级电路的输出端产生一所述输出信号。

8.优选地,所述电感结构包括:第一磁芯,包括基板和位于基板上的至少两个磁芯柱;至少两个第一绕组,每个所述第一绕组绕制在一个所述磁芯柱,所述至少两个第一绕组中的任意两个绕组相互分离,以形成所述电感线圈;以及第二绕组,绕制在至少两个所述磁芯柱,并位于所述第一绕组上方,以形成所述耦合线圈。

9.根据本发明的第二方面,提供一种电感结构,包括:第一磁芯,包括基板和位于基板上的至少两个磁芯柱;至少两个第一绕组,每个所述第一绕组绕制一个所述磁芯柱,所述至少两个第一绕组中的任意两个绕组之间存在间隔;以及第二绕组,绕制在所述至少两个磁芯柱上。

10.优选地,所述第二绕组与所述至少两个第一绕组中的任意一个第一绕组之间的耦合系数大于相邻的两个第一绕组之间的耦合系数。

11.优选地,还包括第二磁芯,所述第二磁芯位于所述基板上,包覆所述至少两个第一绕组、所述第二绕组以及所述第一磁芯。

12.优选地,所述第一绕组的个数小于等于所述磁芯柱的个数。

13.优选地,所述第二磁芯的和所述第一磁芯为相同材料的磁粉芯。

14.优选地,所述第二磁芯的和所述第一磁芯为不同材料的磁粉芯。

15.优选地,所述第一磁芯的磁导率大于所述第二磁芯的磁导率。

16.优选地,所述磁芯柱的个数大于所述第一绕组的个数时,未被所述第一绕组绕制的所述磁芯柱与所述第二磁芯的材料相同。

17.优选地,所述磁芯柱并排排列。

18.优选地,所述磁芯柱多排排列。

19.优选地,所述第一绕组的出线位于所述基板的同一侧面。

20.优选地,所述第一绕组的出线位于所述基板不同的侧面。

21.优选地,所述第二绕组位于所述第一绕组的上方。

22.综上所述,本发明公开了一种功率变换器以及一种电感结构,通过间接耦合的方式是实现多路电感之间的负耦合,解决了大电流应用的瞬态响应,实现各路之间的均流。另外,选择磁粉芯材料作为磁芯,其热导率较高,增加了电感的散热能力,也减小了电感的体积。

附图说明

23.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

24.图1为本发明提供的功率变换器的电路结构图;

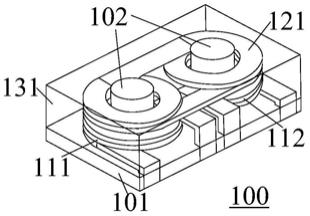

25.图2a为本发明提供的第一种电感结构示意图;

26.图2b为本发明提供的第一种电感结构的部分示意图;

27.图3为本发明提供的第二种电感结构的示意图;

28.图4为本发明提供的第二种电感结构的仿真波形;

29.图5为本发明提供的第三种电感结构的示意图。

具体实施方式

30.以下基于实施例对本发明进行描述,但是本发明并不仅仅限于这些实施例。在下文对本发明的细节描述中,详尽描述了一些特定的细节部分。对本领域技术人员来说没有这些细节部分的描述也可以完全理解本发明。为了避免混淆本发明的实质,公知的方法、过程、流程、元件和电路并没有详细叙述。

31.此外,本领域普通技术人员应当理解,在此提供的附图都是为了说明的目的,并且附图不一定是按比例绘制的。

32.同时,应当理解,在以下的描述中,“电路”是指由至少一个元件或子电路通过电气连接或电磁连接构成的导电回路。当称元件或电路“连接到”另一元件或称元件/电路“连接在”两个节点之间时,它可以是直接耦接或连接到另一元件或者可以存在中间元件,元件之间的连接可以是物理上的、逻辑上的、或者其结合。相反,当称元件“直接耦接到”或“直接连接到”另一元件时,意味着两者不存在中间元件。

33.除非上下文明确要求,否则整个说明书和权利要求书中的“包括”、“包含”等类似词语应当解释为包含的含义而不是排他或穷举的含义;也就是说,是“包括但不限于”的含义。

34.在本发明的描述中,需要理解的是,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性。此外,在本发明的描述中,除非另有说明,“多个”的含义是两个或两个以上。

35.图1为本发明提供的功率变换器的电路结构图。具体地,如图1所示,所述功率变换器包括一电感结构,所述电感结构包括第一至第n路电感线圈l1-ln和一个耦合线圈400。其中,每一路所述电感线圈和相应的晶体管组成一功率级电路,以在所述功率级电路的输出端产生输出信号vout,例如,第一路电感线圈l1和相应的晶体管q10和q11组成第一路功率级电路;第一路电感线圈l2和相应的晶体管q20和q21组成第二路功率级电路;以此类推,第n路电感线圈ln和相应的晶体管qn0和qn1组成第n路功率级电路。所述耦合线圈400和每一路所述电感线圈l1-ln成负耦合关系。

36.所述耦合线圈400和所述电感线圈之间的耦合关系强于任意两路所述电感线圈之间的耦合关系。具体地,任意两路所述电感线圈之间成负耦合关系,并且,所述耦合线圈和所述电感线圈之间的耦合系数大于任意两路所述电感线圈之间的耦合系数,即所述耦合线圈400与任一路的电感线圈之间的耦合系数大于任意两路所述电感线圈之间的耦合系数。

37.每一路所述功率级电路的输入端接收同一输入电压源vin,每一所述功率级电路的输出端产生一输出信号vout,当然,功率变换器也可应用于每一所述功率级电路的输出端产生相互独立的所述输出信号,在此不做限制。

38.本实施例所述电感结构包括:第一磁芯,包括基板和位于基板上的至少两个磁芯柱;至少两个第一绕组,每个所述第一绕组绕制在一个所述磁芯柱,所述至少两个第一绕组中的任意两个绕组相互分离,以形成所述电感线圈;以及第二绕组,绕制在至少两个所述磁芯柱,并位于所述第一绕组上方,以形成所述耦合线圈。

39.图2a为本发明提供的第一种电感结构的示意图,图2b为本发明提供的第一种电感结构的部分示意图,以更清楚的显示第一绕组上表面的结构。具体地,如图2a和2b所示,电感100包括第一磁芯,至少两个第一绕组(111和112)以及第二绕组121。所述第一磁芯包括基板101和至少两个磁芯柱102,每个所述第一绕组绕制一个所述磁芯柱,所述至少两个第一绕组中的相邻的两个第一绕组之间有间隔;所述第二绕组121绕制在所述至少两个磁芯柱上。其中,所述第一绕组的个数小于等于所述磁芯柱的个数。

40.所述电感还包括第二磁芯131,所述第二磁芯131位于所述基板101上,并包覆所述第一磁芯,所述第一绕组(111和112)以及所述第二绕组121。

41.在本实施例中,所述磁芯柱的个数等于所述第一绕组的个数,即一个所述第一绕组绕制一个所述磁芯柱。具体地,所述磁芯柱和所述第一绕组的个数都为2个。在其他实施例中,可以根据需要设置所述磁芯柱的个数和所述第一绕组的个数,只要所述第一绕组的个数小于等于所述磁芯柱的个数即可,在此不做限制。同时也可以根据需要设置所述第一绕组和所述第二绕组绕制所述磁芯柱的匝数,在此也不做限制。

42.所述第一磁芯和所述第二磁芯131可选择相同材料的磁粉芯,也可选择不同材料的磁粉芯,在本实施例中,优选所述第一磁芯的磁导率大于所述第二磁芯131的磁导率。由

于磁粉芯的磁导率很低,所以所述第二绕组与所述至少两个第一绕组的任一绕组的耦合系数大于所述第一绕组之间的耦合系数,所述第二绕组与所述至少两个第一绕组的任一第一绕组的耦合系数可通过它们的位置关系来调节。

43.所述第一磁芯和所述第一绕组以及所述第二绕组可一体成型,也可先形成第一磁芯,然后将所述第一绕组和所述第二绕组与所述第一磁芯再组装,在此并不做任何限制。

44.在本实施例中,所述第一绕组的出线延伸至所述基板101的同一侧面,当然,在其它实施例中,所述第一绕组的出线也可延伸至所述基板101相对的两个侧面。

45.以第一种电感的结构为例,假设两个第一绕组的自感分别为l1和l2,则l1=l2;第一个第一绕组与第二绕组之间的互感为m13和m31,第二个第一绕组与第二绕组之间的互感为m23和m32,则m13=m31=m23=m32;两个第一绕组之间的互感为m12和m21,则m12=m21。

46.设置l1=l2=l;m13=m31=m23=m32=m;m12=m21==ms,则有:

47.第一个第一绕组两端的电压

48.第二个第一绕组两端的电压第二个第一绕组两端的电压

49.其中,i1为流过第一个第一绕组的电流,i2为流过第二个第一绕组的电流,ic为流过第二绕组的电流。由上述的(1)(2)(3)三个公式可以将两路间接耦合的电感整理成普通的两路耦合电感的两端电压的关系形式(4)和(5):

50.假设

51.则有

[0052][0053]

由此公式(4)和(5)可以说明本技术提供的两路间接耦合的电感可实现两路电感之间的负耦合。

[0054]

图3为本发明提供的第二种电感结构的示意图。如图3所示,所述第二种电感结构与所述第一种电感结构的主要区别在于:第二种电感结构为四路输出电感,即第一绕组(211、212、213、214)和磁芯柱202的个数为4个。所述第一绕组和所述第二绕组221都是绕制一匝。其他结构基本相同,在此不在赘述。本实施例的磁芯柱可以并排排列成一排,也可以排成两排,其排列方式可由本领域技术人员根据需求设置,在此不做限制。

[0055]

根据第一种电感结构中上述公式的推导,也可进一步推导出多路间接耦合的电感可实现多路电感之间的负耦合。

[0056]

图4为本发明提供的第二种电感结构的仿真波形。如图4所示,四个曲线依次代表四路第一绕组的电流大小,可以看出,由于各路间接耦合在一起,单路的电流变化,会受到其他路电流的影响。每路绕组的等效感量是一样的,一路绕组的电流变化,其他路也会很快响应变化,更容易实现负载突然变化的时候,各路之间的均流。

[0057]

图5为本发明提供的第三种电感结构的示意图。如图5所示,所述第三种电感结构与所述第一种电感结构的主要区别在于所述第一绕组311的个数小于所述磁芯柱302的个数,即存在未被所述第一绕组311绕制的磁芯柱303。在本实施例中,未被所述第一绕组绕制的磁芯柱303为2个,且位于磁芯柱的两侧。当然,在其他实施例中,未被所述第一绕组绕制的磁芯柱303可以为任意一个,可以位于基板301的中间位置,也可以位于两侧的位置,即可以位于基板301上的任意位置,在此不做任何限制。本实施例的磁芯柱可以并排排列成一排,也可以排成两排,其排列方式可由本领域技术人员根据需求设置,在此不做限制。

[0058]

另外,未被所述第一绕组绕制的磁芯柱也可以与所述第二磁芯331选择相同的磁粉芯材料。

[0059]

本实施例的第二绕组在磁粉芯结构中形成了额外的电感,增加了第二绕组的感量,更便于调节电感中的电流纹波和各路绕组之间的耦合系数。

[0060]

以上所述仅为本发明的优选实施例,并不用于限制本发明,对于本领域技术人员而言,本发明可以有各种改动和变化。凡在本发明的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1