一种具有抗单粒子烧毁能力的功率器件

1.本发明涉及功率半导体器件领域,特别是涉及一种具有抗单粒子烧毁能力的功率器件。

背景技术:

2.功率mosfet器件是一种可以广泛使用在模拟电路与数字电路的场效晶体管,在航空、航天等领域的电子学系统中,用作备用电源的功率开关、dc-dc电压变换器、信号发射机等多个部位。而功率mosfet则指处于功率输出级的mosfet器件,通常工作电流大于1a。由于功率mosfet可以从工艺技术上有效地降低器件的特征导通电阻(ron),并且能处理较大的导通电流,因此,目前功率mosfet再低压mosfet产品市场中被广泛接受。

3.但是功率mosfet器件对单粒子效应却存在固有的薄弱性,单个高能粒子入射到功率mosfet器件内部会引发单粒子烧毁(single event burnout,seb)效应,一旦发生会导致器件永久失效,影响整个电子学系统的正常工作。并且单粒子烧毁(single event burnout,seb)是众所周知的突发故障机制,其是由于穿过功率mosfet的单个重离子而引发。单粒子烧毁的出现归因于器件固有的寄生晶体管,寄生晶体管由n+源区、p-体区和n-外延层组成。如果此寄生晶体管导通,则在施加的大漏极电压的影响下,会发生足够的载流子倍增,导致电流过大,从而引起器件的热破坏。

4.由于功率mosfet在太空中的广泛应用,研究seb的加固技术是很有价值的。因此有必要对传统mosfet进一步研究,改进结构,以提高器件的抗单粒子烧毁性能。

技术实现要素:

5.本发明的目的是提供一种具有抗单粒子烧毁能力的功率器件,以解决上述现有技术存在的问题,改善器件的抗单粒子烧毁效应,优化器件的整体性能。

6.为实现上述目的,本发明提供了如下方案:本发明提供一种具有抗单粒子烧毁能力的功率器件,包括衬底,在所述衬底下方设置有漏极,所述衬底上方设置有硅外延层,所述硅外延层上方设置有si

1-x

ge

x

源极层和绝缘栅层,所述si

1-x

ge

x

源极层和所述绝缘栅层左右相接,所述si

1-x

ge

x

源极层上方设置有金属源极。

7.可选地,所述硅外延层自下到上依次包括n型缓冲区、n型漂移区和p-si体区,所述n型缓冲区下方与所述衬底相接,所述p-si体区上方与所述si

1-x

ge

x

源极层相接。

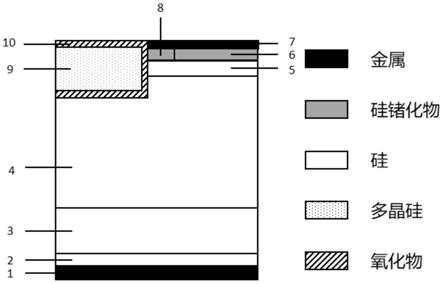

8.可选地,所述si

1-x

ge

x

源极层包括p

+

si

1-x

ge

x

源区和n

+

si

1-x

ge

x

源区,所述p

+

si

1-x

ge

x

源区右方与所述n

+

si

1-x

ge

x

源区相接。

9.可选地,所述p

+

si

1-x

ge

x

源区的掺杂浓度、源极扩散深度能够进行调整。

10.可选地,所述n

+

si

1-x

ge

x

源区的掺杂浓度、源极扩散深度能够进行调整。

11.可选地,所述绝缘栅层包括多晶硅栅极,所述多晶硅栅极的表面设置有栅氧化层。

12.可选地,所述衬底为硅层。

13.可选地,所述p

+

si

1-x

ge

x

源区的掺杂浓度的调整范围为1

×

10

17

cm-3-1

×

10

20

cm-3

,所

述p

+

si

1-x

ge

x

源区源极扩散深度的范围为0.1um-0.5um。

14.可选地,所述n

+

si

1-x

ge

x

源区的掺杂浓度的调整范围为1

×

10

17

cm-3-1

×

10

20

cm-3

,所述n

+

si

1-x

ge

x

源区源极扩散深度的范围为0.1um-0.5um。

15.本发明公开了以下技术效果:

16.本发明的具有抗单粒子烧毁能力的功率器件,硅和si

1-x

ge

x

这两种材料带隙之间的差异,造成了传导和价带不连续。导带和价带之间的带隙分布对这些异质器件的电荷输运有很大的影响。利用从n+si

1-x

ge

x

源到p-si体区域形成异质结能够降低电子发射器的注入效率,从而降低寄生bjt的电流增益,提高seb阈值电压。

附图说明

17.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

18.图1为本发明实施例中具有抗单粒子烧毁能力的功率器件结构示意图;

19.图2为现有技术中传统umosfet功率器件结构示意图;

20.图3为本发明实施例中具有抗单粒子烧毁能力的功率器件与传统umosfet器件输出特性曲线i

d-vd关系图;

21.图4为两器件漏极瞬态电流随时间变化关系图。

22.其中,具有抗单粒子烧毁能力的功率器件中:1为漏极、2为衬底、3为多层缓冲层、4为漂移区、5为p-si体区、6为p

+

si

1-x

ge

x

源区、7为源极、8为n

+

si

1-x

ge

x

源区、9为多晶硅栅极、10为栅氧化层;

23.传统umosfet功率器件中:10为漏极、20为衬底、30为多层缓冲层、40为漂移区、50为p-si体区、60为p+si源区、70为源极、80为n+si源区、90为多晶硅栅极、100为栅氧化层。

具体实施方式

24.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

25.为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

26.本发明提供一种具有抗单粒子烧毁能力的功率器件,如图1所示。该功率器件包括衬底2,衬底2为硅层,衬底硅层下方设置有漏极1,漏极1采用金属材质,在衬底的上方设置有硅外延层,硅外延层包括多层缓冲层3、漂移区4和p-si体区5,其中,多层缓冲层3为n型缓冲层,漂移区4为n型漂移区,多层缓冲层3、漂移区4和p-si体区5自下至上依次相接,多层缓冲层3位于衬底2上方。p-si体区5的上方设置有si

1-x

gex(x取0到1的任意值)源极层,si

1-x

ge

x

源极层包括p

+

si

1-x

ge

x

源区6和n

+

si

1-x

ge

x

源区8,si

1-x

ge

x

源极层上方设置有源极7,si

1-x

ge

x

源极层和源极7的左侧与绝缘栅层相接。绝缘栅层包括多晶硅栅极9,多晶硅栅极9与漂移区4、

p-si体区5、si

1-x

ge

x

源极层、源极7之间设置有栅氧化层10,即多晶硅栅极9被栅氧化层10半包覆。

27.本实施例中,si

1-x

gex源极层包括p

+

si

1-x

ge

x

源区6和n

+

si

1-x

ge

x

源区8,p

+

si

1-x

ge

x

源区6和n

+

si

1-x

ge

x

源区8左右相接并且处于同一水平层。p

+

si

1-x

ge

x

源区6和n

+

si

1-x

ge

x

源区8下方与p-si体区5相接,p

+

si

1-x

ge

x

源区6和n

+

si

1-x

ge

x

源区8上方设置有源极7。在本实施例中,p

+

si

1-x

ge

x

源区6的掺杂浓度1

×

10

17

cm-3

到1

×

10

20

cm-3

、源极扩散深度0.1um到0.5um,上述掺杂浓度和扩散深度能够进行同量级别的数值调整;n

+

si

1-x

ge

x

源区8的掺杂浓度1

×

10

17

cm-3

到1

×

10

20

cm-3

、源极扩散深度0.1um到0.5um,上述掺杂浓度和扩散深度能够进行调整。对本实施例中的具有抗单粒子烧毁能力的功率器件与传统umosfet器件在同一实验条件下进行仿真。传统umosfet器件结构如图2所示,自下至上包括:漏极10、衬底20、多层缓冲层30、漂移区40、p-si体区50、p

+

si源区60、源极70、n

+

si源区80、多晶硅栅极90、栅氧化层100。

28.根据图3所示仿真结果可以得出,本发明的具有抗单粒子烧毁能力的功率器件与传统umosfet器件输出特性曲线相差不大,能够确认在功率器件中加入si

1-x

ge

x

源极层,对其基础特性没有较大影响,能够保证功率器件的正常使用功能。

29.根据图4所示仿真结果可以得出,加固结构和对比结构的seb阈值电压分别为63v和59v。硬化结构中器件的seb性能略有改进。

30.由于在本发明所提出的结构中加入硅和si

1-x

ge

x

合金生长的进步使得使用带隙工程构建异质结器件(如使用这些材料的hbt异质结双极晶体管和hemt高电子迁移率晶体管)成为可能。两种材料带隙之间的差异会产生导带和价带的不连续性。导带和价带之间的带隙分布对这些异质器件中的电荷传输有很大影响。由于源体区异质结构的形成导致的导带不连续性有助于防止发射极的电子注入集电极,降低电子发射极的注入效率。由于p

+

栓塞区材料从si变为sige,加固结构中p

+

栓塞区的价带能量远低于p-体区,使得更多的空穴从p+栓塞区泄漏到地(source电极)。为了激活寄生晶体管,需要更大的漏极电压。

31.在本发明的描述中,需要理解的是,术语“纵向”、“横向”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

32.最后应说明的是:以上所述实施例,仅为本发明的具体实施方式,用以说明本发明的技术方案,而非对其限制,本发明的保护范围并不局限于此,尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,其依然可以对前述实施例所记载的技术方案进行修改或可轻易想到变化,或者对其中部分技术特征进行等同替换;而这些修改、变化或者替换,并不使相应技术方案的本质脱离本发明实施例技术方案的精神和范围。都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应所述以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1