一种扇出型封装器件及其制备方法与流程

1.本技术涉及芯片封装技术领域,特别是涉及一种扇出型封装器件及其制备方法。

背景技术:

2.随着mcm(multi chip module,多芯片组件)兴起,封装逐渐有了集成的概念,先进封装本质由对芯片保护、尺度放大和电气连接的基本需求转向芯片在封装内的集成实现模块、部件或者系统化的目的。

3.为优化芯片之间电气性能,对于封装内的芯片的集成度要求越来越高,不同于传统所有芯片需要通过基板实现芯片之间的电气连接,越来越多的解决方案基于通孔技术采用具有通孔的介质层或芯片本身硅通孔进行堆叠,仅有通过堆叠表面的方式将多重芯片同基板进行连接,此种方法能够较好实现同类芯片封装模块化的需求,但对于多重芯片之间非单一的互联难以整合成一个高集成度的封装体。

技术实现要素:

4.本技术主要解决的技术问题是提供一种扇出型封装器件及其制备方法,能够实现多重芯片的高集成度封装。

5.为解决上述技术问题,本技术采用的一个技术方案是:提供一种扇出型封装器件,包括:第一芯片,包括相背设置的第一功能面和第一非功能面,且所述第一功能面上设置有第一焊盘;第一再布线层,位于所述第一功能面一侧,且与所述第一焊盘电连接;同层设置的第二芯片和第三芯片,位于所述第一再布线层背离所述第一芯片一侧;其中,所述第二芯片包括相背设置的第二功能面和第二非功能面,所述第二功能面上设置有第二焊盘,所述第二非功能面朝向所述第一再布线层;在所述第一芯片至所述第一再布线层方向上,所述第三芯片内部设置有贯通的导电孔,所述导电孔的一端与所述第一再布线层电连接;第二再布线层,位于所述第二芯片和所述第三芯片背离所述第一芯片一侧,且所述第二再布线层与所述第二焊盘以及所述导电孔的另一端电连接。

6.其中,所述扇出型封装器件还包括:第一塑封层,至少覆盖所述第一芯片的侧面;第二塑封层,覆盖所述第二芯片和素数第三芯片的侧面,且所述第二再布线层位于所述第二塑封层背离所述第一芯片一侧。

7.其中,所述第一塑封层背离所述第一再布线层一侧表面与所述第一非功能面齐平;所述扇出型封装器件还包括:绝缘层,覆盖所述第一非功能面以及所述第一塑封层背离所述第一再布线层一侧表面。

8.其中,所述第三芯片与所述第一再布线层之间具有缝隙,所述封装器件还包括:焊料,位于所述缝隙内,且所述导电孔通过焊料与所述第一再布线层电连接;底填胶,覆盖所述焊料的外围且填充所述缝隙。

9.为解决上述技术问题,本技术采用的另一个技术方案是:提供一种扇出型封装器件的制备方法,包括:在第一芯片的第一功能面上形成第一再布线层,且所述第一再布线层

与所述第一功能面上的第一焊盘电连接;在所述第一再布线层背离所述第一芯片一侧设置第二芯片和第三芯片;其中,所述第二芯片的第二非功能面朝向所述第一再布线层;在所述第一芯片至所述第一再布线层方向上,所述第三芯片内部设置有贯通的导电孔,所述导电孔的一端与所述第一再布线层电连接;在所述第二芯片和所述第三芯片背离所述第一芯片一侧形成第二再布线层,且所述第二再布线层与所述第二芯片的第二功能面上的第二焊盘电连接、以及与所述导电孔的另一端电连接。

10.其中,所述在第一芯片的第一功能面上形成第一再布线层的步骤之前,包括:将所述第一芯片设置于载板上,且所述第一芯片的第一功能面朝向所述载板;在所述第一芯片的侧面以及第一非功能面形成第一塑封层;去除所述载板。

11.其中,所述在第一再布线层背离所述第一芯片一侧设置第二芯片和第三芯片的步骤,包括:利用粘性层将所述第二芯片的第二非功能面与所述第一再布线层固定;利用焊料来使所述第三芯片的导电孔的一端与所述第一再布线层电连接,并在焊料的外围形成底填胶。

12.其中,所述在所第二芯片和所述第三芯片背离所述第一芯片一侧形成第二再布线层的步骤之前,包括:在所述第一再布线层设置有所述第二芯片和所述第三芯片一侧形成第二塑封层,所述第二塑封层覆盖所述第二芯片的第二功能面以及所述第三芯片的导电孔的另一端;研磨所述第二塑封层背离所述第一芯片一侧,以使得所述第二焊盘以及所述第三芯片的导电孔的另一端从所述第二塑封层中露出。

13.其中,所述在所述第二芯片和所述第三芯片背离所述第一芯片一侧形成第二再布线层的步骤之后,包括:在所述第二再布线层背离所述第一芯片一侧形成焊球。

14.其中,在所述第二再布线层背离所述第一芯片一侧形成焊球的步骤之后,包括:从第一塑封层背离第一再布线层一侧对所述第一塑封层进行研磨,以使得所述第一塑封层与第一非功能面齐平;在齐平的所述第一非功能面和所述第一塑封层一侧设置绝缘层。

15.本技术的有益效果是:区别于现有技术的情况,本技术提出的扇出型封装器件及其制备方法通过在第一芯片功能面一侧设置第一再布线层,并于第一再布线层背离所述第一芯片一侧同层设置第二芯片和第三芯片,其中第三芯片内部设置有导电孔。第二芯片和第三芯片背离第一芯片一侧设置有第二再布线层。第一再布线层与第一芯片功能面上的焊盘以及第三芯片导电孔的一端电连接,第二在布线层与第二芯片功能面上的焊盘以及第三芯片导电孔的另一端电连接。本技术提出的扇出型封装器件中第一芯片和第三芯片之间可以通过第一再布线层实现信息传递、第二芯片和第三芯片之间可以通过第二再布线层实现信息传递、而第一芯片和第二芯片之间又可以通过第三芯片进行信息传递,即本技术可以将非单一性的多重芯片进行互联并整合成一个高集成度的封装体。

附图说明

16.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。其中:

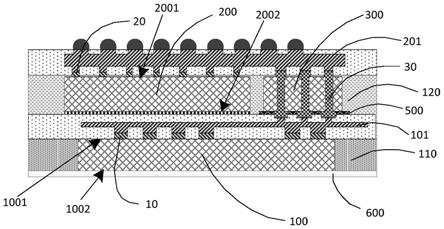

17.图1是本技术扇出型封装器件一实施方式的结构示意图;

18.图2是本技术扇出型封装器件的制备方法一实施方式的流程示意图;

19.图3是步骤s101之前对应一实施方式的流程示意图;

20.图4a是步骤s201对应的一实施方式的剖视结构示意图;

21.图4b是步骤s202对应的一实施方式的剖视结构示意图;

22.图4c是步骤s203对应的一实施方式的剖视结构示意图;

23.图5a为步骤s101对应的一实施方式的剖视结构示意图;

24.图6a为步骤s102对应的一实施方式的剖视结构示意图;

25.图7为步骤s103之前对应的一实施方式的流程示意图;

26.图8a为步骤s401对应的一实施方式的剖视结构示意图;

27.图8b为步骤s402对应的一实施方式的剖视结构示意图;

28.图8c为步骤s103对应的一实施方式的剖视结构示意图;

29.图8d为步骤s103对应的又一实施方式的剖视结构示意图。

具体实施方式

30.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性的劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

31.参阅图1,图1是本技术所提出的扇出型封装器件一实施方式的结构示意图,本技术所提供的扇出型封装器件包括:

32.第一芯片100,包括相背设置的第一功能面1001和第一非功能面1002,且第一功能面1001上设置有第一焊盘10;可选地,第一焊盘10可以从第一功能面1001上凸出;或者,第一焊盘10的表面也可与第一功能面1001齐平。

33.第一再布线层101,位于上述第一功能面1001一侧,且与上述第一焊盘10电连接。可选地,上述第一再布线层101包括第一介电层和图案化的第一金属层;其中,第一介电层对应第一焊盘10的位置设置有第一过孔;第一金属层位于第一介电层背离第一芯片100一侧,且填充该第一过孔。此外,上述第一再布线层101的层数可以为一层或多层,本技术对此不作限定。

34.同层设置的第二芯片200和第三芯片300,位于第一再布线层101背离第一芯片100一侧;其中,第二芯片200包括相背设置的第二功能面2001和第二非功能面2002,第二功能面2001上设置有第二焊盘20,第二非功能面2002朝向第一再布线层101;在第一芯片100至第一再布线层101方向上,第三芯片300内部设置有贯通的导电孔30,导电孔30的一端与第一再布线层101电连接。

35.第二再布线层201,位于第二芯片200和第三芯片300背离第一芯片100一侧,且第二再布线层201与第二焊盘20以及导电孔30的另一端电连接。可选地,上述第二再布线层201包括第二介电层和图案化的第二金属层;其中,第二介电层对应第二焊盘20和第三芯片300上导电孔30的位置设置有第二过孔;第二金属层位于第二介电层背离第一芯片100一侧,且填充该第二过孔。此外,上述第二再布线层201的层数可以为一层或多层,本技术对此不作限定。

36.在上述设计方式中,扇出型封装器件中第一芯片100和第三芯片300之间可以通过第一再布线层101实现信息传递、第二芯片200和第三芯片300之间可以通过第二再布线层201实现信息传递、而第一芯片100和第二芯片200之间又可以通过第三芯片300进行信息传递,即本技术可以将非单一性的多重芯片进行互联并整合成一个高集成度的封装体。

37.在一个实施方式中,请继续参阅图1,本技术所提供的扇出型封装器件还包括:第一塑封层110,至少覆盖第一芯片100的侧面。该第一塑封层110的材质可以为环氧树脂等,其可对第一芯片100起到一定的保护作用。可选地,在本实施例中,第一塑封层110可以仅覆盖第一芯片100的侧面,此时第一塑封层110背离第二芯片一侧表面可以与第一芯片齐平,以提高散热效果。在此基础上,本技术所提供的扇出型封装器件还可以包括:绝缘层600,覆盖第一非功能面1002以及第一塑封层110背离第一再布线层101一侧表面。该绝缘层600可以在保证散热效果的同时,提高对第一芯片100的保护。可选地,该绝缘层600的材质可以为二氧化硅或聚酰亚胺等。

38.在又一个实施方式中,请继续参阅图1,本技术所提供的扇出型封装器件还包括:第二塑封层120,覆盖第二芯片200和第三芯片300的侧面,且第二再布线层201位于第二塑封层120背离第一芯片100一侧。该第二塑封层120的材质可以为环氧树脂等。该第二塑封层120可以对第二芯片200和第三芯片300起到一定的保护和限位作用。

39.在又一个实施方式中,第三芯片300与第一再布线层101之间具有缝隙,本技术所提供的扇出型封装器件还包括:焊料,位于上述缝隙内,且导电孔30通过焊料与第一再布线层101电连接;底填胶500,覆盖焊料的外围且填充上述缝隙。该底填胶500可以对第三芯片300的位置起到一定的限位作用。

40.请参阅图2,图2是本技术提出的扇出型封装器件的制备方法一实施方式的流程示意图,该方法包括:

41.s101:在第一芯片的第一功能面上形成第一再布线层,且第一再布线层与第一功能面上的第一焊盘电连接。

42.请参阅图3,图3为图2中步骤s101之前对应一实施方式的流程示意图,步骤s101之前还包括:

43.s201:将第一芯片设置于载板上,且第一芯片的第一功能面朝向载板。

44.具体地,请参阅图4a,图4a是图3中步骤s201对应的一实施方式的剖视结构示意图,图4a仅仅是示意性的,为便于理解,图4a上只画出一个第一芯片100,第一芯片100上包含六个焊盘,而实际应用中,可将多个第一芯片100设置于载板50上,以封装成多个高集成度的芯片,并通过切割两个相邻高集成度芯片中间部分以获得单个高集成度芯片;每个第一芯片100也可以包括多个第一焊盘10以接收和/或传输信号。

45.在一应用方式中,步骤s201具体包括:将第一芯片100设置于载板50上,该第一芯片100包括相背设置的第一功能面1001和第一非功能面1002,在第一功能面1001上设置有多个第一焊盘10,且第一芯片100的第一功能面1001朝向载板50。

46.可选地,第一芯片100的第一功能面1001可以通过键合胶与载板50固定,第一焊盘10埋设于键合胶中,并将第一焊盘10与载板50之间隔开,使载板50不与第一焊盘10直接接触。载板50的材质具体可以为硅、玻璃、金属和有机复合材料等中的一种,载板50可以对第一芯片100的第一功能面1001一侧起到一定保护作用,使第一芯片100的第一功能面1001不

裸露在外。也可以通过在载板50上贴附双面胶,将至少一个第一芯片100黏贴到双面胶上,此时第一芯片100的第一功能面1001朝向载板50。

47.s202:在第一芯片的侧面以及第一非功能面形成第一塑封层。

48.具体地,请参阅图4b,图4b是图3中步骤s202对应的一实施方式的剖视结构示意图。在一应用方式中,步骤s202具体包括:在第一芯片100的侧面以及第一非功能面1002形成第一塑封层110,以保护第一芯片100的侧面以及第一非功能面1002。其中,第一塑封层110的材质可以为环氧树脂等,其可通过压合工艺形成。

49.s203:去除载板。

50.具体地,请参阅图4c,图4c是图3中步骤s203对应的一实施方式的剖视结构示意图。在一应用方式中,步骤s203具体包括:将第一芯片100的第一功能面1001与载板50分离,以露出第一芯片100的第一功能面1001以及第一功能面1001上的第一焊盘10,以便于实施步骤s101。

51.进一步,请参阅图5a,图5a为图2中步骤s101对应的一实施方式的剖视结构示意图。上述步骤s101具体包括:在第一芯片100的第一功能面1001上形成第一再布线层101,且第一再布线层101与第一功能面1001上的第一焊盘10电连接。其中,还可以在第一再布线层101表面形成第一掩膜层102,起到一定保护第一再布线层101的作用,第一掩膜层102的材料可以为光刻胶、氧化硅、氮化硅、无定形碳中至少一种。可选地,上述第一再布线层101包括第一介电层和图案化的第一金属层;其中,第一介电层对应第一焊盘10的位置设置有第一过孔;第一金属层位于第一介电层背离第一芯片100一侧,且填充该第一过孔。此外,上述第一再布线层101的层数可以为一层或多层,本技术对此不作限定。

52.s102:在第一再布线层背离第一芯片一侧设置第二芯片和第三芯片。

53.请参阅图6a,图6a为图2中步骤s102对应一实施方式的剖视结构示意图。在一应用方式中,步骤s102具体包括:利用粘性层130在第一再布线层101背离第一芯片100一侧同层设置第二芯片200和第三芯片300。具体地,第二芯片200包括相背设置的第二功能面2001和第二非功能面2002,可以在第二芯片200的第二非功能面2002上形成粘性层130,并利用粘性层130将第二芯片200的第二非功能面2002与第一再布线层101固定,对第二芯片200起到限位作用。

54.第三芯片300内部设置有多个贯通的导电孔30,导电孔内填充有焊料,焊料在导电孔30的两端形成凸出,利用焊料使第三芯片300的导电孔30的一端与第一再布线层101电连接,第三芯片300通过第一再布线层101可以实现与第一芯片100之间的信息交互。第三芯片300与第一再布线层101之间具有缝隙,在焊料周围形成底填胶500以覆盖焊料外围且填充缝隙。该底填胶500可以对第三芯片300的位置起到一定的限位作用。其中,利用焊料使第三芯片300的导电孔30的一端与第一再布线层101电连接之前包括利用干法蚀刻工艺去除第一再布线层101表面部分第一掩膜层102,以便于导电孔30通过焊料与第一再布线层101连接。可选地,第三芯片300不限于tsv(硅通孔)、tgv(玻璃通孔)、tmv(环氧树脂通孔)。

55.s103:在第二芯片和第三芯片背离第一芯片一侧形成第二再布线层,且第二再布线层与第二芯片的第二功能面上的第二焊盘电连接、以及与导电孔的另一端电连接。

56.具体地,请参阅图7,图7为图2中步骤s103之前对应的一实施方式的流程示意图,步骤s103之前还包括:

57.s401:在第一再布线层设置有第二芯片和第三芯片一侧形成第二塑封层。

58.请参阅图8a,图8a为图7中步骤s401对应的一实施方式的剖视结构示意图。在一应用方式中,步骤s401具体包括:在第一再布线层101设置有第二芯片200和第三芯片300一侧形成第二塑封层120,第二塑封层120覆盖第二芯片200的第二功能面2001以及第三芯片300的导电孔的另一端,可以对第二芯片200和第三芯片300起到一定的保护和限位作用。其中,第二塑封层120的材质可以为环氧树脂等,其可通过压合工艺形成。

59.s402:研磨第二塑封层背离第一芯片一侧,以使得第二焊盘以及第三芯片的导电孔的另一端从第二塑封层中露出。

60.请参阅图8b,图8b为图7中步骤s402对应的一实施方式的剖视结构示意图。在一应用方式中,步骤s402具体包括:对第二塑封层120背离第一芯片100一侧进行研磨,以露出第二芯片200的第二功能面2001上的第二焊盘20以及第三芯片300的导电孔30的另一端。

61.进一步地,请参阅图8c,图8c为图2中步骤s103对应一实施方式的剖视结构示意图。在一应用方式中,步骤s103具体包括:在第二芯片200和第三芯片300背离第一芯片100一侧形成第二再布线层201,且第二再布线层201与上述步骤s402中露出的第二芯片200的第二功能面2001上的第二焊盘20电连接、以及与第三芯片300的导电孔30的另一端电连接,第二芯片200与第三芯片300之间可以通过第二再布线层实现信息交互。其中,还可以在第二再布线层201表面形成第二掩膜层202,以保护第二再布线层201,第二掩膜层202的材料可以为光刻胶、氧化硅、氮化硅、无定形碳中至少一种。可选地,上述第二再布线层201包括第二介电层和图案化的第二金属层;其中,第二介电层对应第二焊盘20和第三芯片300上导电孔30的位置设置有第二过孔;第二金属层位于第二介电层背离第一芯片100一侧,且填充该第二过孔。此外,上述第二再布线层201的层数可以为一层或多层,本技术对此不作限定。

62.进一步地,请参阅图8d,图8d为图2中步骤s103对应的又一实施方式的剖视结构示意图。在一应用方式中,可以在第二再布线层201背离第一芯片100一侧形成焊球70,焊球70后续可与任一基板(图未示)电连接,进而实现芯片的信号与基板进行交互。

63.进一步的,请参阅图1,在第二再布线层201背离第一芯片100一侧形成焊球70后,从第一塑封层110背离第一再布线层101一侧对第一塑封层110进行研磨,以使得第一塑封层110与第一芯片100的第一非功能面1002齐平,并在齐平的第一非功能面1002和第一塑封层110一侧设置绝缘层600,该绝缘层600覆盖第一非功能面1002以及第一塑封层110背离第一再布线层101一侧表面。对第一塑封层110进行研磨可以减小芯片封装后的整体厚度并提高散热效果。其中,绝缘层600的材质具体可为二氧化硅或聚酰亚胺等,绝缘层600可以在保证散热效果的同时将第一芯片100的第一非功能面1002上的半导体材料与其他电器元件隔绝,以提高第一芯片100的稳定性和安全性。

64.可选地,也可以采用从第一塑封层110背离第一再布线层101一侧对第一塑封层110进行适当研磨,但不露出第一芯片100的第一非功能面1002,该方法减小了芯片封装后的整体厚度且不需要额外设置绝缘层,并由第一塑封层将第一芯片100的第一非功能面1002上的半导体材料与其他电器元件隔绝,以提高第一芯片100的稳定性和安全性。

65.本技术提出的扇出型封装器件制备方法通过在第一芯片100的第一功能面1001一侧设置第一再布线层101,并于第一再布线层101背离所述第一芯片100一侧同层设置第二芯片200和第三芯片300,其中第三芯片300内部设置有多个导电孔30。第二芯片200和第三

芯片300背离第一芯片100一侧设置有第二再布线层201。第一再布线层101与第一芯片100的第一功能面1001上的第一焊盘10以及第三芯片300的导电孔30的一端电连接,第二再布线层201与第二芯片200的第二功能面2001上的第二焊盘20以及第三芯片300的导电孔30的另一端电连接。即第一芯片100和第三芯片300之间可以通过第一再布线层101实现信息传递、第二芯片200和第三芯片300之间可以通过第二再布线层201实现信息传递、而第一芯片100和第二芯片200之间又可以通过第三芯片300进行信息传递,即通过本技术提出的扇出型器件制备方法可以将非单一性的多重芯片进行互联并整合成一个高集成度的封装体。

66.可选地,本技术提出的扇出型封装器件的制备方法不限于仅实现对第一芯片、第二芯片以及第三芯片的封装,根据实际情况,本技术中提到的第一芯片结构也可以由多个同层设置的第一芯片组成,由第一再布线层与所有第一芯片功能面上的焊盘电连接,以实现所有第一芯片之间的信息交互;第二芯片结构也可以由多个同层设置的第二芯片组成,由第二再布线层与所有第二芯片功能面上的焊盘电连接,以实现所有第二芯片之间的信息交互。

67.以上所述仅为本技术的实施方式,并非因此限制本技术的专利范围,凡是利用本技术说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本技术的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1