层叠电感器、及层叠电感器的安装结构的制作方法

1.本发明涉及层叠电感器、及层叠电感器的安装结构。

背景技术:

2.目前,作为层叠电感器,已知有日本特开平10-144526号公报中记载的电感器。该层叠电感器具备:通过将由绝缘体构成的多个层向层叠方向进行层叠而形成的素体、设置于素体的端面及侧面的端子电极、和设置于素体内且沿素体的长边方向延伸的直线状的导体部。导体部在长边方向的整个区域中具有一定的宽度。

技术实现要素:

3.在此,在上述那样的层叠电感器中,形成有端子电极从素体的端面绕入侧面的绕入部。在该情况下,在端子电极的绕入部和直线状的导体部之间产生杂散电容。由于这种杂散电容的影响,有时层叠电感器的自谐振频率(srf)降低。

4.本发明的目的在于,提供能够提高自谐振频率的层叠电感器、及层叠电感器的安装结构。

5.本发明提供一种层叠电感器,其具备:素体,其通过将由绝缘体构成的多个层向层叠方向层叠而形成;端子电极,其设置于素体的至少一个侧面;和直线状的导体部,其设置于素体内,沿第一方向延伸,在从与第一方向正交的第二方向观察时,导体部在与端子电极重叠的区域具有第一部分,并且在不与端子电极重叠的区域具有第二部分,从第二方向观察时的第一部分的宽度比第二部分的宽度小。

6.在本发明的层叠电感器中,在从第二方向观察时,直线状的导体部在与端子电极重叠的区域中具有第一部分。第一部分是容易在与侧面的端子电极之间产生杂散电容的部分。在此,从第二方向观察时的第一部分的宽度比不与端子电极重叠的区域的第二部分的宽度小。由此,能够降低第一部分和侧面的端子电极之间的杂散电容。如上,能够提高层叠电感器的自谐振频率。

7.也可以是,从与第一方向及第二方向正交的第三方向观察时的第一部分的宽度比第二部分的宽度小。在该情况下,能够相对增大从第三方向观察时的第二部分的宽度。由此,能够增大不与侧面的端子电极重叠的第二部分的截面面积,因此,能够降低导体部的直流电阻(rdc)。

8.也可以是,从第一方向观察,导体部具有向与第一方向及第二方向正交的第三方向扩展的形状,在素体形成有识别导体部的姿势的标记。在该情况下,通过在将层叠电感器安装于安装基板时确认标记,能够将向第三方向扩展的导体部的姿势设为期望的状态。

9.本发明提供一种层叠电感器的安装结构,其具备所述层叠电感器和隔着端子电极安装有层叠电感器的安装基板,层叠电感器以从第一方向观察,导体部从安装基板的安装面立起的方式安装。

10.在本发明的层叠电感器的安装结构中,以将导体部从安装基板的安装面立起的方

式安装了层叠电感器,因此,能够降低在导体部和安装基板之间产生的杂散电容。由此,能够提高层叠电感器的自谐振频率。

11.根据本发明,可以提供能够提高自谐振频率的层叠电感器、及层叠电感器的安装结构。

附图说明

12.图1是表示本发明第一实施方式的层叠电感器的立体图。

13.图2的(a)是沿着图1所示的iia-iia线的截面图,图2的(b)是沿着图1所示的iib-iib线的截面图。

14.图3的(a)是沿着图1所示的iiia-iiia线的截面图,图3的(b)是沿着图1所示的iiib-iiib线的截面图。

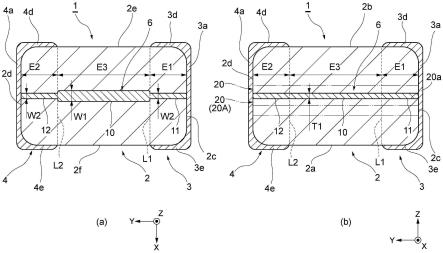

15.图4的(a)是表示第二实施方式的层叠电感器的与图2的(a)对应的截面图,图4的(b)是表示第二实施方式的层叠电感器的与图2的(b)对应的截面图。

16.图5的(a)表示第二实施方式的层叠电感器的与图3的(a)对应的截面图,图5的(b)是表示第二实施方式的层叠电感器的与图3的(b)对应的截面图。

17.图6的(a)表示将第二实施方式的层叠电感器安装于安装基板的安装结构的、与图3的(a)对应的截面图,图6的(b)表示将第二实施方式的层叠电感器安装于安装基板的安装结构的、与图3的(b)对应的截面图。

具体实施方式

18.[第一实施方式]

[0019]

参照图1~图3说明本发明第一实施方式的层叠电感器。图1是表示本发明的第一实施方式的层叠电感器1的立体图。图2的(a)是沿着图1所示的iia-iia线的截面图。图2的(b)是沿着图1所示的iib-iib线的截面图。图3的(a)是沿着图1所示的iiia-iiia线的截面图。图3的(b)是沿着图1所示的iiib-iiib线的截面图。

[0020]

如图1所示,层叠电感器1具备素体2和端子电极3、4。素体2是通过将由绝缘体构成的多个层向层叠方向层叠而形成的构件。素体2呈长方体形状。此外,在之后的说明中,有时相对于层叠电感器1设定xyz坐标进行说明。在此,将z轴方向设为层叠多个层的“层叠方向z”。另外,将与层叠方向z正交的方向中的、y轴方向设为素体2的“长边方向y”,将x轴方向设为素体2的“短边方向x”。将层叠方向z中的、上侧设为正侧,底侧设为负侧。将短边方向x及长边方向y的一侧设为正侧。此外,xyz坐标是相对于层叠电感器1设定的相对坐标。

[0021]

素体2具有层叠方向z上相对的侧面2a及侧面2b、长边方向y上相对的端面2c、2d、和短边方向x上相对的侧面2e、2f。侧面2a配置于层叠方向z的负侧,侧面2b配置于层叠方向z的正侧。端面2c配置于长边方向y的负侧,端面2d配置于长边方向y的正侧。侧面2e配置于短边方向x的负侧,侧面2f配置于短边方向x的正侧。此外,素体2的材料没有特别限定,也可以根据层叠电感器1的用途采用适当的材料,例如,也可以采用玻璃陶瓷等。虽然没有特别限定,素体2的长边方向y的尺寸被设定为0.3~1.6mm,短边方向x的尺寸被设定为0.3~1.6mm,层叠方向z的尺寸被设定为0.3~1mm。

[0022]

端子电极3、4是形成于素体2的端面2c、2d附近的电极。端子电极3、4在安装层叠电

感器1时与安装基板的端子接合。端子电极3以覆盖端面2c的整个面,并且覆盖侧面2a、2b、2e、2f的端面2c附近的区域的方式设置。端子电极3以从端面2c向侧面2a、2b、2e、2f绕入的方式形成。端子电极4以覆盖端面2d的整个面,并且覆盖侧面2a、2b、2e、2f的端面2d附近的区域的方式设置。端子电极4以从端面2d向侧面2a、2b、2e、2f绕入的方式形成。端子电极3、4以在长边方向y上相互分离的方式配置。由此,侧面2a、2b、2e、2f的长边方向y的中央附近的区域成为从端子电极3、4露出的状态。端子电极3、4的材料没有特别限定,也可以根据层叠电感器1的用途采用适当的材料,例如,也可以采用银、铜等。端子电极3、4也可以通过使素体2的端部浸渍于电极的膏体的浸渍法而形成。但是,端子电极3、4的形成方法没有特别限定,也可以通过在素体2的端部印刷电极的膏体等其它的方法形成。

[0023]

接着,参照图2及图3对素体2的内部结构进行说明。如图2及图3所示,层叠电感器1具备设置于素体2内的导体部6。如图2的(a)、(b)所示,导体部6为设置于素体2内,沿长边方向y延伸的直线状的导体图案。导体部6配置于素体2的内部中的、层叠方向z的中央位置,且短边方向x的中央位置。导体部6具有与xy平面平行地扩展,且沿y轴方向延伸那样的带状的形状。由此,从长边方向y观察,导体部6具有沿短边方向x扩展的形状(参照图3的(a)、(b))。

[0024]

导体部6的长边方向y的负侧的端部露出于素体2的端面2c。由此,导体部6与覆盖端面2c的端子电极3的主体部3a电连接。导体部6的长边方向y的正侧的端部露出于素体2的端面2d。由此,导体部6与覆盖端面2d的端子电极4的主体部4a电连接。此外,在本实施方式中,导体部6沿长边方向y延伸,因此,长边方向y相当于权利要求中的“第一方向”。另外,层叠方向z相当于权利要求中的“第二方向”。另外,短边方向x相当于权利要求中的“第三方向”。

[0025]

在此,素体2通过将多个层20沿层叠方向z层叠而形成(参照图2的(b))。该层20在烧结前作为一张片材体而构成,烧结后,以不能观察到层20间的边界部的方式进行一体化。在图2的(b)中,为了便于说明,将一部分层20以虚拟线表示。多个层20中,在一个层20a的一个主面20a形成有导体部6的导体图案。在另一个层20未形成导体图案。通过将这些多个层20层叠并使其烧结,在层叠方向z的中央位置形成有导体部6。

[0026]

接着,对基于与端子电极3、4的位置关系的导体部6的形状进行说明。如图2的(a)、(b)所示,在长边方向y上,素体2具有被端子电极3覆盖的区域e1、被端子电极4覆盖的区域e2、和均未被任一端子电极3、4覆盖的区域e3。如图2的(b)所示,区域e1成为层叠方向z上由覆盖侧面2a、2b的端子电极3的绕入部3b、3c夹持的区域。区域e2成为层叠方向z上由覆盖侧面2a、2b的端子电极4的绕入部4b、4c夹持的区域。区域e3成为侧面2a、2b从端子电极3的绕入部3b、3c及端子电极4的绕入部4b、4c露出的区域。如图2的(a)所示,区域e1成为短边方向x上由覆盖侧面2e、2f的端子电极3的绕入部3d、3e夹持的区域。区域e2成为短边方向x上由覆盖侧面2e、2f的端子电极4的绕入部4d、4e夹持的区域。区域e3成为侧面2e、2f从端子电极3的绕入部3d、3e及端子电极4的绕入部4d、4e露出的区域。此外,在本实施方式中,绕入部3b、3c、3d、3e的绕入量相同,因此,区域e1和区域e3的边界l1根据绕入部3b、3c、3d、3e的长边方向y的正侧的端部的位置进行定义。但是,在绕入部3b、3c、3d、3e的绕入量互不相同的情况下,根据绕入量最大的绕入部的端部定义边界l1。区域e2和区域e3的边界l2也一样。

[0027]

在从层叠方向z观察时,导体部6在区域e1、2中与端子电极3、4重叠,在区域e3中不与端子电极3、4重叠。与之相对,在从层叠方向z观察时,导体部6在区域e1、e2中与端子电极

3、4重叠的区域e1、e2中具有第一部分11、12,并且在不与端子电极3、4重叠的区域e3中具有第二部分10。在本实施方式中,第一部分11和第二部分10的边界与区域e1和区域e3的边界l1一致。另外,第一部分12和第二部分10的边界与区域e2和区域e3的边界l2一致。但是,第一部分11、12的一部分也可以到达至区域e3,第二部分10也可以到达至区域e1、e2。

[0028]

如图2的(a)所示,从层叠方向z观察时的第一部分11、12的宽度比第二部分10的宽度小。如图2的(a)及图3的(a)所示,将第二部分10的宽度的尺寸设为“尺寸w1”。另外,如图2的(a)及图3的(b)所示,将第一部分11、12的宽度的尺寸设为“尺寸w2”。在该情况下,“尺寸w1》尺寸w2”的关系成立。此外,虽然没有特别限定,但第二部分10的尺寸w1也可以设定为60~150μm。与之相对,第一部分11、12的尺寸w2也可以设定为尺寸w1的50~90%。此外,在本实施方式中,从短边方向x观察时的第一部分11、12及第二部分10的宽度(即厚度)以“尺寸t1”成为恒定。虽然没有特别限定,但尺寸t1设定为5~40μm。

[0029]

此外,如图3所示,从长边方向y观察,导体部6具有沿短边方向x扩展的形状,尺寸w1、w2比尺寸t1大。这样,在安装时,导体部6的姿势根据将侧面2a、2b、2e、2f的哪个侧面安装于安装基板而进行变化。因此,如图1所示,在素体2形成有识别导体部6的姿势的标记30。在本实施方式中,在侧面2b形成有标记30。但是,将标记30形成于层叠电感器1的哪个位置及设为哪种形状没有特别限定。

[0030]

接着,对本实施方式的层叠电感器1的作用

·

效果进行说明。

[0031]

在本实施方式的层叠电感器1中,在从层叠方向z观察时,直线状的导体部6在与端子电极3、4重叠的区域e1、e2具有第一部分11、12。第一部分11是容易在与侧面2a、2b的端子电极3的绕入部3b、3c之间产生杂散电容的部分。第一部分12是容易在与侧面2a、2b的端子电极4的绕入部4b、4c之间产生杂散电容的部。在此,从层叠方向z观察时的第一部分11、12的宽度比不与端子电极3、4重叠的区域e3的第二部分10的宽度小。由此,能够降低第一部分11、12和侧面的端子电极3、4之间的杂散电容。如上,能够提高层叠电感器1的自谐振频率。

[0032]

此外,导体部6的第一部分11、12及第二部分10的结构相对于现有的导体部(长边方向y的整个区域中宽度一定的导体图案),可以通过使相当于第一部分11、12的部位的宽度变细来实现,也可以通过使相当于第二部分10的部位的宽度变粗来实现,也可以通过该双方实现。在使相当于第一部分11、12的部位的宽度变细的情况下,与现有的导体部相比,能够降低与端子电极3、4之间的杂散电容。在使相当于第二部分10的部位的宽度变粗的情况下,能够降低导体部6的直流电阻。在现有的导体部中要得到同等的直流电阻的情况下,由于要增大导体部整体的宽度,因此,结果,与端子电极3、4的杂散电容增加。在使相当于第二部分10的部位的宽度变粗的情况下,能够一边抑制这种杂散电容的增加,一边降低直流电阻。即,相对于得到的直流电阻,能够使层叠电感器1的自谐振频率比现有的自谐振频率相对提高。

[0033]

从长边方向y观察,导体部6具有沿与长边方向y及层叠方向z正交的短边方向x扩展的形状,也可以在素体2形成有识别导体部6的姿势的标记30。在该情况下,在将层叠电感器1安装于安装基板时,通过确认标记30,能够将向短边方向x扩展的导体部6的姿势设为期望的状态。

[0034]

[第二实施方式]

[0035]

接着,参照图4及图5对第二实施方式的层叠电感器1进行说明。图4的(a)是表示第

二实施方式的层叠电感器1的与图2的(a)对应的截面图。图4的(b)是表示第二实施方式的层叠电感器1的与图2的(b)对应的截面图。图5的(a)是表示第二实施方式的层叠电感器1的与图3的(a)对应的截面图。图5的(b)是表示第二实施方式的层叠电感器1的与图3的(b)对应的截面图。

[0036]

在第二实施方式的层叠电感器1中,如图4的(b)所示,从短边方向x观察时的第一部分11、12的宽度(即厚度)比第二部分10的宽度(即厚度)小。如图4的(b)及图5的(b)所示,从短边方向x观察时的第一部分11、12的宽度的尺寸设定成与第一实施方式相同的“尺寸t1”。与之相对,如图4的(b)及图5的(a)所示,将从短边方向x观察时的第二部分10的宽度的尺寸设为“尺寸t2”。在该情况下,“尺寸t2》尺寸t1”的关系成立。此外,虽然没有特别限定,但第二部分10的t2也可以设定成尺寸t1的50~90%。第二实施方式的其它部分与第一实施方式一样。

[0037]

上述那样的尺寸关系可通过相较于第一实施方式,增大第二部分10的导体图案的厚度而实现。例如,在对层20a的烧结前的片材体印刷导体膏时,也可以仅对与第二部分10对应的部位进行多次印刷。由此,如图4的(b)所示,能够使第二部分10的厚度向层叠方向z的正侧增加。另外,在层20a的主面20a中的、与第二部分10对应的部位设置槽,向该槽填充导电膏,由此,能够以槽的深度的量来增厚第二部分10。由此,如图4的(b)所示,能够使第二部分10的厚度向层叠方向z的负侧增加。此外,如何增加第二部分10的厚度的方法没有特别限定。第二部分10的厚度也可以仅向层叠方向z的正侧及负侧的任一方增加。

[0038]

在第二实施方式的层叠电感器1中,能够相对地增大从短边方向x观察时的第二部分10的宽度。由此,能够增大不与侧面的端子电极重叠的第二部分的截面面积,因此,能够降低导体部的直流电阻(rdc)。

[0039]

在将各实施方式的层叠电感器1安装于安装基板的情况下,即使在短边方向x(即导体部6扩展的方向)和安装基板的安装面平行的状态下安装,也能够得到充分的效果。但是,通过采用图6所示那样的安装结构,能够进一步降低层叠电感器1的自谐振频率。图6的(a)是表示将第二实施方式的层叠电感器1安装于安装基板150的安装结构100的、与图3的(a)对应的截面图,图6的(b)是表示将第二实施方式的层叠电感器1安装于安装基板150的安装结构100的、与图3的(b)对应的截面图。

[0040]

具体而言,如图6所示,层叠电感器1的安装结构100具备上述的层叠电感器1和经由端子电极3、4安装层叠电感器1的安装基板150。层叠电感器1以从长边方向y观察,导体部6从安装基板150的安装面150a立起的方式安装。

[0041]

在层叠电感器1的安装结构100中,以导体部6从安装基板150的安装面150a立起的方式安装层叠电感器1,因此,能够降低在导体部6和安装基板150之间产生的杂散电容。由此,能够提高层叠电感器1的自谐振频率。

[0042]

此外,在以成为这种位置关系的方式安装层叠电感器1的情况下,通过参照标记30(参照图1),掌握素体2的内部的导体部6的姿势是有效的。

[0043]

本发明不限定于上述的实施方式。

[0044]

例如,素体2的形状及端子电极3、4的形状也可以适当变更。随之,第一部分11、12和第二部分10的形状及比率也适当变更。

[0045]

在上述的实施方式中,端子电极3、4具有主体部3a、4a和4个绕入部。但是,端子电

极3、4只要设置于4个侧面2a、2b、2a、2f中的至少一个侧面即可,也可以省略与其它的侧面及端面对应的部分。此外,在将端子电极3、4仅设置于侧面的情况下,只要经由通孔导体等连接导体部6和端子电极3、4即可。

[0046]

符号说明

[0047]1……

层叠电感器,2

……

素体,2a、2b、2a、2f

……

侧面,3、4

……

端子电极,6

……

导体部,10

……

第二部分,11、12

……

第一部分,30

……

标记,100

……

安装结构,150

……

安装基板。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1