一种耗尽型SiC异质结晶体管外延结构及其制备方法与流程

一种耗尽型sic异质结晶体管外延结构及其制备方法

技术领域

1.本发明属于半导体技术领域,涉及一种耗尽型sic异质结晶体管外延结构及其制备方法。

背景技术:

2.以sic为代表的第三代宽带隙半导体材料具有宽带隙、高临界击穿电场、高热导率、高载流子饱和漂移等特点,特别适合制作高温、高压、高频、大功率、抗辐照等半导体器件。

3.在sic多型体中,3c-sic、4h-sic、6h-sic等晶型应用最广泛,3c-sic禁带宽度为2.3ev,4h-sic的禁带宽度高达3.2ev,禁带宽度差达0.9ev,由于禁带宽度相差大,3c-sic与4h-sic形成的异质结器件具有很大的潜力。

4.然而,在3c-sic/4h-sic异质结结构应用于场效应晶体管器件时,在关态情况下,器件源端接地,栅极加载负压,漏端加载正电压时,器件体材料漏电路径主要是先垂直通过4h-sic外延层,然后水平通过4h-sic衬底与4h-sic外延缓冲层界面。因此,传统生长3c-sic/4h-sic异质结结构都基于半绝缘衬底,然而半绝缘sic衬底价格昂贵,因此使用价格相对较低的高掺杂导电性sic衬底是未来发展方向。

5.然而目前高掺杂导电性sic衬底都存在小面生长,衬底浓度不均匀性很大,如图3所示。小面即生长界面平行(0001)面的部分,在小面上无法进行台阶流生长,而且(0001)面也是最容易进行氮掺杂的晶面,因此会在衬底上呈现较深的颜色。衬底上颜色的深浅,主要是氮含量决定,颜色越深,氮含量越多,电阻率越低。因此,小面上生长的外延层制成的3c-sic/4h-sic异质结器件,漏电较正常晶面要大很多。因此,亟需提高4h-sic外延层的的抗压能力。

技术实现要素:

6.为解决上述技术问题,本发明提供了一种耗尽型sic异质结晶体管外延结构及其制备方法,该外延结构具有高电子迁移率,且可降低漏电通道,避免衬底小面生长区域漏电流较大而导致器件失效。

7.本发明采取的技术方案如下:

8.一种耗尽型sic异质结高晶体管外延结构,所述耗尽型sic异质结晶体管外延结构由下至上依次包括:sic衬底层、n型高掺杂4h-sic缓冲层、n型低掺杂4h-sic缓冲层、掺v高阻4h-sic缓冲层、掺v高阻4h-sic漂移层、4h-sic沟道层、3c-sic势垒层。

9.所述衬底层为正轴n型sic衬底层。

10.所述n型高掺杂4h-sic缓冲层的厚度为0.5~1μm,n的掺杂浓度为5

×

10

17

cm-3

~2

×

10

18

cm-3

。

11.所述n型低掺杂4h-sic缓冲层的厚度为1~2μm,n的掺杂浓度为8

×

10

15

cm-3

~2

×

10

16

cm-3

。

12.所述掺v高阻4h-sic缓冲层的厚度为5~10μm;v的掺杂浓度为1

×

10

15

cm-3

~5

×

10

15

cm-3

。

13.所述掺v高阻4h-sic漂移层的厚度为5~10μm;v的掺杂浓度为1

×

10

16

cm-3

~5

×

10

16

cm-3

。

14.所述4h-sic沟道层的厚度为1~2μm;所述3c-sic势垒层的厚度为5~10μm。

15.本发明还提供了所述的耗尽型sic异质结晶体管外延结构的制备方法,包括以下步骤:

16.(1)原位刻蚀sic衬底,得到sic衬底层;

17.(2)在sic衬底层上生长n型高掺杂4h-sic缓冲层;

18.(3)在n型高掺杂4h-sic缓冲层上生长n型低掺杂4h-sic缓冲层;

19.(4)在n型低掺杂4h-sic缓冲层上生长掺v高阻4h-sic缓冲层;

20.(5)在掺v高阻4h-sic缓冲层上生长掺v高阻4h-sic漂移层;

21.(6)在掺v高阻4h-sic外延层上生长4h-sic沟道层;

22.(7)在4h-sic沟道层上生长3c-sic势垒层。

23.所述掺v高阻4h-sic缓冲层的生长方法为:分别以160~240slm、80~500sccm、80~500sccm和5~20sccm的流量通入载气h2、含氯的硅源气体、碳源和vcl4,于1700~1750℃温度和50~200mbar压力下进行生长。

24.所述掺v高阻4h-sic漂移层的生长方法为:分别以160~240slm、80~500sccm、80~500sccm和30~60sccm的流量通入载气h2、含氯的硅源气体、碳源和vcl4,于1700~1750℃温度和50~200mbar压力下进行生长。

25.本发明还提供了一种含所述耗尽型sic异质结晶体管外延结构的器件,该器件中在所述耗尽型sic异质结高电子迁移率晶体管外延结构的3c-sic势垒层之上设置源极、肖特基接触栅极、漏极,sin隔离层;所述源极、漏极分别处于肖特基接触栅极的两边;所述源极与肖特基接触栅极之间设置sin隔离层;所述肖特基接触栅极与漏极之间设置sin隔离层。

26.所述器件在关态情况下,器件源端接地,栅极加载负压,漏端加载正电压时,器件体材料漏电路径主要是先依次垂直通过3c-sic势垒层、4h-sic沟道层、掺v高阻4h-sic漂移层、掺v高阻4h-sic缓冲层、n型低掺杂4h-sic缓冲层、n型高掺杂4h-sic缓冲层,然后水平通过n型sic衬底与n型高掺杂4h-sic缓冲层的界面,掺v高阻4h-sic缓冲层、掺v高阻4h-sic外延层的存在可降低漏电通道,避免衬底小面生长区域漏电流较大而导致器件失效。

27.本发明提供的耗尽型sic异质结晶体管外延结构中,在4h-sic缓冲层、4h-sic漂移层中均进行v掺杂,作为高阻缓冲层及高阻外延层,以降低漏电通道,避免衬底小面生长区域漏电流较大而导致器件失效。

28.与现有技术相比,本发明具有以下有益效果:

29.1.本发明在耗尽型sic异质结晶体管外延结构中采用3c/4h-sic异质结结构,3c/4h-sic异质结是由同种元素材料但是不同晶型构成的异质结,这种新型的异质结结构可以很容易地避免传统algan/gan形成的异质结结构难以解决的界面态问题,界面态主要是由晶格失配引起的,就大多数同种材料的不同晶型而言,立方晶型的(111)面跟六方晶型的(0001)面晶格失配是可以忽略的,因此,本发明提供的耗尽型sic异质结晶体管外延结构具

有高电子迁移率;

30.2.本发明在耗尽型sic异质结晶体管外延结构中,选取正轴n型sic碳面衬底作为sic衬底层,其较半绝缘衬底价格便宜;并在正轴n型sic碳面衬底上设置n型高掺杂4h-sic缓冲层以缓冲衬底与漂移层因浓度差产生的失配应力;在n型高掺杂4h-sic缓冲层上设置n型低掺杂4h-sic缓冲层,sic掺n晶格收缩,掺v晶格膨胀,n型低掺杂4h-sic缓冲层的存在可缓冲与其上设置的掺v高阻层的晶格失配;而在掺v高阻4h-sic缓冲层之上设置掺v高阻4h-sic漂移层可阻断反向击穿,作为耐压层;其上设置的4h-sic沟道层作为本征sic层,可降低界面粗糙度散射及缺陷散射的影响;然后在4h-sic沟道层上设置3c-sic势垒层以形成4h-sic/3c-sic异质结结构。

附图说明

31.图1为耗尽型sic异质结晶体管外延结构的结构图;

32.图2为耗尽型sic异质结晶体管外延结构应用于场效应晶体管器件时的漏电通道示意图;

33.图3为高掺杂导电性sic衬底小面生长的示意图;

34.图中1-sic衬底层、2-n型高掺杂4h-sic缓冲层、3-n型低掺杂4h-sic缓冲层、4-掺v高阻4h-sic缓冲层、5-掺v高阻4h-sic漂移层、6-4h-sic沟道层、7-3c-sic势垒层、8-源极、9-漏极、10-肖特基接触栅极、11-sin隔离层。

具体实施方式

35.一种耗尽型sic异质结高电子迁移率晶体管外延结构,所述耗尽型sic异质结高电子迁移率晶体管外延结构由下至上依次包括:sic衬底层、n型高掺杂4h-sic缓冲层、n型低掺杂4h-sic缓冲层、掺v高阻4h-sic缓冲层、掺v高阻4h-sic漂移层、4h-sic沟道层、3c-sic势垒层。

36.所述耗尽型sic异质结高电子迁移率晶体管外延结构的制备方法,包括以下步骤:

37.1)sic衬底原位刻蚀;选取正轴n型sic碳面衬底,以160~240slm的流量通入h2和30~100sccm的流量通入hcl,于50-200mbar压力和1450-1500℃温度下刻蚀10~30min;

38.2)n型高掺杂4h-sic缓冲层生长:停止通入hcl,分别以160~240slm、80~500sccm、80~500sccm和40~100sccm的流量通入载气h2、含氯的硅源气体、碳源和n2,于1580~1700℃温度和50~200mbar压力,生长0.5~1μm厚的n型高掺杂4h-sic缓冲层,掺杂浓度5

×

10

17

cm-3

~2

×

10

18

cm-3

;所述含氯的硅源气体为sicl4、sihcl3、sih2c12或sih3cl;

39.3)n型低掺杂4h-sic缓冲层的生长:分别以160~240slm、80~500sccm、80~500sccm和5~10sccm的流量通入载气h2、含氯的硅源气体、碳源和n2,于1580~1650℃温度和50~200mbar压力,生长1~2μm厚的n型低掺杂4h-sic缓冲层,掺杂浓度8

×

10

15

cm-3

~2

×

10

16

cm-3

;所述含氯的硅源气体为sicl4、sihcl3、sih2c12或sih3cl;

40.4)掺v高阻4h-sic缓冲层的生长:关闭n2,分别以160~240slm、80~500sccm、80~500sccm和5~20sccm的流量通入载气h2、含氯的硅源气体、碳源和vcl4,于1700~1750℃温度和50~200mbar压力,生长5~10μm厚的掺杂半绝缘型4h-sic高阻层,掺杂浓度1

×

10

15

cm-3

~5

×

10

15

cm-3

;

41.5)掺v高阻4h-sic漂移层的生长:关闭n2,分别以160~240slm、80~500sccm、80~500sccm和30~60sccm的流量通入载气h2、含氯的硅源气体、碳源和vcl4,于1700~1750℃温度和50~200mbar压力,生长5~10μm厚的掺杂半绝缘型4h-sic高阻层,掺杂浓度1

×

10

16

cm-3

~5

×

10

16

cm-3

;

42.6)4h-sic沟道层的生长:关闭vcl4,分别以160~240slm、80~500sccm和80~500sccm的流量通入载气h2、含氯的硅源气体和碳源,于1580~1650℃温度和50~200mbar压力,生长1~2μm厚的4h-sic沟道层;

43.7)3c-sic势垒层生长:分别以160~240slm、100~500sccm、100~500sccm和15~50sccm的流量通入h2、硅源、碳源和n2,于1400~1500℃温度和200~500mbar压力下,生长5~10μm厚的3c-sic外延层;

44.8)在h2保护下降温至室温;

45.上述各步骤中,含氯的硅源气体为sicl4、sihcl3、sih2c12或sih3cl。

46.下面结合实施例及说明书附图对本发明进行详细说明。

47.实施例1

48.一种耗尽型sic异质结高电子迁移率晶体管外延结构,所述耗尽型sic异质结高电子迁移率晶体管外延结构由下至上依次包括:sic衬底层、n型高掺杂4h-sic缓冲层、n型低掺杂4h-sic缓冲层、掺v高阻4h-sic缓冲层、掺v高阻4h-sic漂移层、4h-sic沟道层、3c-sic势垒层。

49.所述耗尽型sic异质结高电子迁移率晶体管外延结构的制备方法,包括以下步骤:

50.1)sic衬底原位刻蚀;选取正轴n型sic碳面衬底,以196slm的流量通入h2和40sccm的流量通入hcl,于100mbar压力和1500℃温度下刻蚀10min;

51.2)n型高掺杂4h-sic缓冲层生长:停止通入hcl,分别以196slm、340sccm、380sccm和40sccm的流量通入载气h2、含氯的硅源气体、碳源和n2,于1600℃温度和100mbar压力,生长1μm厚的n型高掺杂4h-sic缓冲层,掺杂浓度1

×

10

18

cm-3

;

52.3)n型低掺杂4h-sic缓冲层的生长:分别以196slm、340sccm、380sccm和5sccm的流量通入载气h2、含氯的硅源气体、碳源和n2,于1600℃温度和100mbar压力,生长1μm厚的n型低掺杂4h-sic缓冲层,掺杂浓度8

×

10

15

cm-3

cm-3

;

53.4)掺v高阻4h-sic缓冲层的生长:关闭n2,分别以196slm、200sccm、220sccm和5sccm的流量通入载气h2、含氯的硅源气体、碳源和vcl4,于1750℃温度和80mbar压力,生长5μm厚的掺杂半绝缘型4h-sic高阻层,掺杂浓度1

×

10

15

cm-3

;

54.5)掺v高阻4h-sic外延层的生长:关闭n2,分别以196slm、200sccm、220sccm和60sccm的流量通入载气h2、含氯的硅源气体、碳源和vcl4,于1750℃温度和80mbar压力,生长10μm厚的掺杂半绝缘型4h-sic高阻层,掺杂浓度5

×

10

16

cm-3

;

55.6)4h-sic沟道层的生长:关闭vcl4,分别以196slm、200sccm和220sccm的流量通入载气h2、含氯的硅源气体和碳源,于1650℃温度和80mbar压力,生长1μm厚的4h-sic沟道层;

56.7)3c-sic势垒层生长:分别以196slm、200sccm、220sccm和23sccm的流量通入h2、硅源、碳源和n2,于1400℃温度和300mbar压力下,生长10μm厚的3c-sic势垒层;

57.8)在h2保护下降温至室温。

58.上述各步骤中,含氯的硅源气体为sicl4、sihcl3、sih2c12或sih3cl。

59.实施例2

60.一种场效应晶体管器件,其是在实施例1中的耗尽型sic异质结高电子迁移率晶体管外延结构的3c-sic势垒层之上设置源极、肖特基接触栅极、漏极,sin隔离层得到;所述源极、漏极分别处于肖特基接触栅极的两边;所述源极与肖特基接触栅极之间设置sin隔离层;所述肖特基接触栅极与漏极之间设置sin隔离层。

61.对比例1

62.一种sic异质结晶体管外延结构,所述sic异质结晶体管外延结构由下至上依次包括半绝缘4h-sic衬底、4h-sic沟道层、n型3c-sic势垒层。

63.所述sic异质结晶体管外延结构的制备方法,包括以下步骤:

64.1)半绝缘4h-sic衬底原位刻蚀;选取正轴n型sic碳面衬底,以196的流量通入h2和40sccm的流量通入hcl,于100mbar压力和1500℃温度下刻蚀10min;

65.2)4h-sic沟道层的生长:分别以196slm、340scc和380sccm的流量通入载气h2、含氯的硅源气体和碳源,于1600℃温度和100mbar压力,生长5μm厚的n型4h-sic沟道层;

66.3)n型3c-sic势垒层生长:分别以196slm、200sccm、220sccm和23sccm的流量通入h2、硅源、碳源和n2,于1400℃温度和300mbar压力下,生长10μm厚的3c-sic势垒层;

67.4)在h2保护下降温至室温。

68.实施例1及对比例1中的晶体管外延结构的性能如表1所示。

69.表1

70.外延来源迁移率面电子密度方阻实施例12237.829.20

×

10

12

325.42对比例12066.417.73

×

10

12

357.12

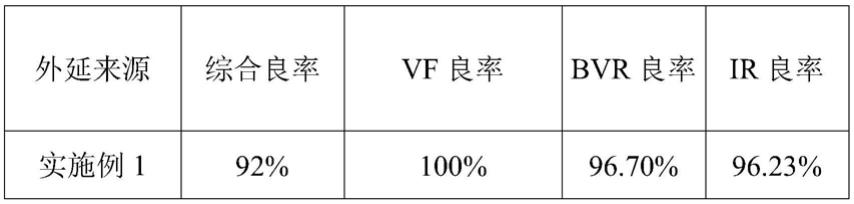

71.实施例1及对比例1中的晶体管外延结构的良率如表2所示。

72.表2

[0073][0074][0075]

上述参照实施例对一种耗尽型sic异质结晶体管外延结构及其制备方法进行的详细描述,是说明性的而不是限定性的,可按照所限定范围列举出若干个实施例,因此在不脱离本发明总体构思下的变化和修改,应属本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1