红光微型发光二极管芯片及其制备方法与流程

1.本公开涉及光电子制造技术领域,特别涉及一种红光微型发光二极管芯片及其制备方法。

背景技术:

2.微型发光二极管(micro light emitting diode,micro led)是指边长在10μm至100μm的超小发光二极管,红光微型发光二极管则是发红光的二极管。微型发光二极管的体积小,可以更密集的设置排列而大幅度提高分辨率,并且具有自发光特性,具有高亮度、高对比度、高反应性及省电的特点。

3.相关技术中,红光微型发光二极管芯片通常包括基板、外延结构、第一电极、第二电极、钝化层、第一焊点块和第二焊点块。其中,外延结构层叠在基板上,第一电极和第二电极均设置外延结构上远离基板的一侧,钝化层位于在在外延结构上,且覆盖两个电极。第一焊点块和第二焊点块位于钝化层上,且通过钝化层上的过孔分别与两个电极相连。

4.两个焊点块通常采用激光焊接的方式在钝化层的表面制作形成,然而,由于激光焊接时会存在温度急剧上升和下降的情况,这样会在芯片内产生应力,容易导致芯片中的外延结构出现裂痕,造成芯片失效的问题。

技术实现要素:

5.本公开实施例提供了一种红光微型发光二极管芯片及其制备方法,能有效缓解因焊接产生的应力,而导致芯片出现裂缝失效的问题。所述技术方案如下:

6.一方面,本公开实施例提供了一种红光微型发光二极管芯片,所述红光微型发光二极管芯片包括:基板、外延结构、第一钝化层、金属增强层、第一电极和第二电极;所述外延结构包括依次层叠于所述基板上的第一半导体层、多量子阱层和第二半导体层,所述第二半导体层的表面具有露出所述第一半导体层的凹槽,所述第一电极位于所述第一半导体层的表面,且位于所述凹槽的底面,所述第二电极位于所述第二半导体层的表面;所述第一钝化层至少覆盖所述第一半导体层、所述第一电极、所述凹槽、所述第二半导体层、所述第二电极的表面,所述金属增强层位于所述第一钝化层上,所述金属增强层在所述基板上的正投影位于所述第一钝化层在所述基板上的正投影内。

7.可选地,所述金属增强层包括依次层叠于所述第一钝化层的表面的第一ti层、第一ni层、pt层、第二ni层和第二ti层,所述pt层的厚度不小于所述金属增强层的总厚度的二分之一。

8.可选地,所述第一ti层的厚度为400埃至600埃,所述第一ni层的厚度为800埃至1200埃,所述pt层的厚度为4900埃至5100埃,所述第二ni层的厚度为800埃至1200埃,所述第二ti层的厚度为400埃至600埃。

9.可选地,所述凹槽的底面具有凸起结构,所述凸起结构与所述凹槽靠近所述第二电极的侧壁相连。

10.可选地,所述凸起结构包括多个阶梯块,多个所述阶梯块沿远离所述凹槽的侧壁的方向依次排列,在远离所述凹槽的侧壁的方向上,所述阶梯块在所述凹槽的侧壁上的正投影的面积逐渐减小。

11.可选地,所述凸起结构有多个,多个所述凸起结构在平行于所述基板的方向上间隔排布。

12.可选地,所述凸起结构远离所述凹槽的底面为阶梯面,所述阶梯面分别与所述凹槽的表面、所述凹槽的侧壁相连。

13.可选地,所述红光微型发光二极管芯片还包括第二钝化层,所述第二钝化层位于所述金属增强层上,所述第二钝化层在所述基板上的正投影与所述第一钝化层在所述基板上的正投影重合。

14.可选地,所述红光微型发光二极管芯片还包括:第一焊点块和第二焊点块,所述第一焊点块和所述第二焊点块均位于所述第二钝化层的表面;所述第一焊点块通过第一过孔与所述第一电极相连,所述第二焊点块通过第二过孔与所述第二电极相连,所述第一焊点块、所述第二焊点块均与所述金属增强层绝缘。

15.另一方面,本公开实施例还提供了一种红光微型发光二极管芯片的制备方法,所述制备方法包括:提供一基板;在所述基板上形成外延结构,所述外延结构包括依次层叠于所述基板上的第一半导体层、多量子阱层和第二半导体层,所述第二半导体层的表面具有露出所述第一半导体层的凹槽;在所述外延结构的表面形成第一电极和第二电极,所述第一电极位于所述第一半导体层的表面,且位于所述凹槽的底面,所述第二电极位于所述第二半导体层的表面;在所述外延结构上形成第一钝化层和金属增强层,所述第一钝化层至少覆盖所述第一半导体层、所述第一电极、所述凹槽、所述第二半导体层、所述第二电极的表面,所述金属增强层位于所述第一钝化层上,所述金属增强层在所述基板上的正投影位于所述第一钝化层在所述基板上的正投影内。

16.本公开实施例提供的技术方案带来的有益效果至少包括:

17.本公开实施例提供的红光微型发光二极管中,在基板上设有外延结构,外延结构中第二半导体层上具有露出第一半导体层的凹槽,第一电极设置在凹槽内与第一半导体层相连,第二电极设置在第二半导体层上,外延结构上覆盖有一层第一钝化层,第一钝化层至少覆盖第一半导体层、第一电极、凹槽、第二半导体层和第二电极的表面,并且,在第一钝化层外还覆盖有金属增强层,金属增强层在基板上的正投影位于第一钝化层在基板上的正投影内,这样避免金属增强层与两个电极相连,而导致两个电极短路。由于金属增强层是设置在外延结构的表面上的,即通过金属增强层能有效加固下方的外延结构的强度,这样在激光焊接导致温度剧烈变化在芯片内产生应力时,该金属增强层能抵御应力,有效防止芯片中的外延结构出现裂痕失效。

附图说明

18.为了更清楚地说明本公开实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

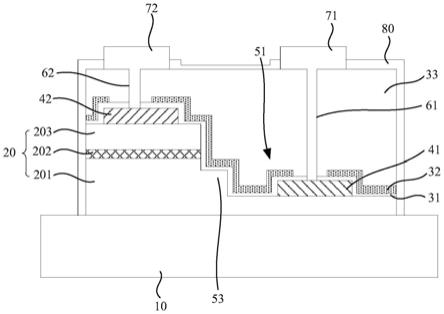

19.图1是本公开实施例提供的一种微型发光二极管芯片的结构示意图;

20.图2是本公开实施例提供的一种金属增强层的结构示意图;

21.图3是本公开实施例提供的一种外延结构的部分结构示意图;

22.图4是本公开实施例提供的一种过渡台阶的俯视图;

23.图5是本公开实施例提供的另一种外延结构的截面图;

24.图6是本公开实施例提供的另一种外延结构的部分结构示意图;

25.图7是本公开实施例提供的一种微型发光二极管芯片的俯视图;

26.图8是本公开实施例提供的一种红光微型发光二极管芯片的制备方法的流程图;

27.图9是本公开实施例提供的一种红光微型发光二极管芯片的制备过程示意图;

28.图10是本公开实施例提供的一种红光微型发光二极管芯片的制备过程示意图。

29.图中各标记说明如下:

30.10、基板;

31.20、外延结构;201、第一半导体层;202、多量子阱层;203、第二半导体层;

32.31、第一钝化层;32、金属增强层;321、第一ti层;322、第一ni层;323、pt层;324、第二ni层;325、第二ti层;33、第二钝化层;

33.41、第一电极;42、第二电极;

34.51、凹槽;53、凸起结构;530、台阶块;531、阶梯块;532、阶梯面;

35.61、第一过孔;62、第二过孔;

36.71、第一焊点块;72、第二焊点块;

37.80、保护层。

具体实施方式

38.为使本公开的目的、技术方案和优点更加清楚,下面将结合附图对本公开实施方式作进一步地详细描述。

39.图1是本公开实施例提供的一种微型发光二极管芯片的结构示意图。如图1所示,该红光微型发光二极管芯片包括:基板10、外延结构20、第一钝化层31、金属增强层32、第一电极41和第二电极42。

40.如图1所示,外延结构20包括依次层叠于基板10上的第一半导体层201、多量子阱层202和第二半导体层203,第二半导体层203的表面具有露出第一半导体层201的凹槽51,第一电极41位于第一半导体层201的表面,且位于凹槽51的底面,第二电极42位于第二半导体层203的表面。

41.如图1所示,第一钝化层31至少覆盖第一半导体层201、第一电极41、凹槽51、第二半导体层203、第二电极42的表面,金属增强层32位于第一钝化层31上,金属增强层32在基板10上的正投影位于第一钝化层31在基板10上的正投影内。

42.本公开实施例提供的红光微型发光二极管中,在基板10上设有外延结构20,外延结构20中第二半导体层203上具有露出第一半导体层201的凹槽51,第一电极41设置在凹槽51内与第一半导体层201相连,第二电极42设置在第二半导体层203上,外延结构20上覆盖有一层第一钝化层31,第一钝化层31至少覆盖第一半导体层201、第一电极41、凹槽51、第二半导体层203和第二电极42的表面,并且,在第一钝化层31外还覆盖有金属增强层32,金属

增强层32在基板10上的正投影位于第一钝化层31在基板10上的正投影内,这样避免金属增强层32与两个电极相连,而导致两个电极短路。由于金属增强层32是设置在外延结构20的表面上的,即通过金属增强层32能有效加固下方的外延结构20的强度,这样在激光焊接导致温度剧烈变化在芯片内产生应力时,该金属增强层32能抵御应力,有效防止芯片中的外延结构20出现裂痕失效。

43.图2是本公开实施例提供的一种金属增强层32的结构示意图。如图2所示,金属增强层32包括依次层叠于第一钝化层31的表面的第一ti层321、第一ni层322、pt层323、第二ni层324和第二ti层325,pt层323的厚度不小于金属增强层32的总厚度的二分之一。

44.其中,第一ti层321用于提高第一钝化层31和金属增强层32之间的粘附性;第一ni层322用于改善第一ti层321和pt层323之间的粘附性,且还可以增加金属增强层32的韧性;pt层323用于增强金属增强层32的强度,即主要通过pt层323抵御应力;第二ni层324用于改善第二ti层325和pt层323之间的粘附性,且还可以增加金属增强层32的韧性;第二ti层325用于提高第二钝化层33和金属增强层32之间的粘附性。

45.上述实现方式中,pt层323的厚度不小于金属增强层32的总厚度的二分之一,即pt层323至少占金属增强层32的总厚度的一半。由于pt层323是用于抵御应力的,因此保证pt层323厚度足够大,以保证金属增强层32抵御应力的效果。

46.示例性地,第一ti层321的厚度为400埃至600埃。作为示例,第一ti层321的厚度为500埃。

47.示例性地,第一ni层322的厚度为800埃至1200埃。作为示例,第一ni层322的厚度为1000埃。

48.示例性地,pt层323的厚度为4900埃至5100埃。作为示例,pt层323的厚度为5000埃。

49.示例性地,第二ni层324的厚度为800埃至1200埃。作为示例,第二ni层324的厚度为1000埃。

50.作为示例,第二ti层325的厚度为400埃至600埃。作为示例,第二ti层325的厚度为500埃。

51.可选地,如图1所示,凹槽51的底面具有凸起结构53,凸起结构53与凹槽51靠近第二电极42的侧壁相连。

52.上述实现方式中,在凹槽51的底面形成凸起结构53。这样能让外延结构20上连接第二半导体的表面和凹槽51的底面的垂直平面,形成阶梯式的曲折面,能延长应力的传递路径,以释放垂直平面所在位置的应力,有效避免外延结构20的表面出现裂纹的情况。

53.图3是本公开实施例提供的一种外延结构20的部分结构示意图。图4是本公开实施例提供的一种凸起结构53的俯视图。如图3、4所示,凸起结构53包括多个阶梯块531,多个阶梯块531沿远离凹槽51的侧壁的方向依次排列,在远离凹槽51的侧壁的方向上,阶梯块531在凹槽51的侧壁上的正投影的面积逐渐减小。

54.上述实现方式中,凸起结构53包括依次排列的多个阶梯块531,且依次排列的各阶梯块531的面积逐渐减小。这样累叠多个阶梯块531得到的凸起结构53就能形成阶梯式的结构,即凸起结构53在平行于基板10方向上的截面为阶梯式的截面,能延长应力的传递路径,以释放垂直平面所在位置的应力,避免外延结构20的表面出现裂纹的情况。

55.示例性地,如图4所示,凸起结构53包括三个阶梯块531,三个阶梯块531沿远离凹槽51的侧壁的方向依次排列,且每个阶梯块531均位于前一个阶梯块531的中部。这样就使凸起结构53构成对称式的阶梯结构,形成阶梯式的截面,进一步延长应力的传递路径,以释放垂直平面所在位置的应力,避免外延结构20的表面出现裂纹的情况。

56.可选地,如图3所示,凸起结构53有多个,多个凸起结构53在平行于基板10的方向上间隔排布。

57.通过设置多个间隔排布的凸起结构53,使凸起结构53在平行于基板10方向上的截面为间断式排列的块状截面,相较于长条状且未分隔的凸起,能这样能延长应力的传递路径,以释放垂直平面所在位置的应力,避免外延结构20的表面出现裂纹的情况。

58.作为示例,本公开实施例中,如图3所示,凸起结构53包括在平行于基板10的方向上间隔排布的两个凸起结构53。

59.图5是本公开实施例提供的另一种外延结构20的截面图。如图5所示,凸起结构53远离凹槽51的底面为阶梯面532,阶梯面532分别与凹槽51的表面、凹槽51的侧壁相连。

60.通过将凸起结构53远离凹槽51的底面设置为阶梯面532,让外延结构20上连接第二半导体的表面和凹槽51的底面的垂直平面,能形成更加密集的阶梯式曲折面,这样能延长应力的传递路径,以释放垂直平面所在位置的应力,有效避免外延结构20的表面出现裂纹的情况。

61.作为一种示例,如图3所示,凸起结构53包括多个台阶块530,每一个台阶块530的结构均可以是如图3示意的包括多个阶梯块531的凸起结构。这样可以让凸起结构53无论是在垂直于基板10的方向上,还是在平行于基板10的方向上,都能形成阶梯式的曲折面,以延长应力的传递路径,便于释放应力。

62.作为一种示例,图6是本公开实施例提供的另一种外延结构的部分结构示意图。如图6所示,凸起结构53包括多个台阶块530,每一个台阶块530可以是矩形块状,即多个台阶块530组合形成呈阶梯状的凸起结构53。该结构更加简单,便于加工制备。

63.可选地,如图1所示,红光微型发光二极管芯片还包括第二钝化层33,第二钝化层33位于金属增强层32上,第二钝化层33在基板10上的正投影与第一钝化层31在基板10上的正投影重合。这样通过第一钝化层31和第二钝化层33一起包覆金属增强层32,以避免金属增强层32裸露,与电极连接而发生短路的问题。

64.示例性地,第二钝化层33可以是dbr(distributed bragg reflection,分布式布拉格反射镜)层,dbr层包括多个周期性交替层叠的sio2层和tio2层。且dbr层的周期数可以在20至50之间。例如,dbr层的周期数为36。

65.其中,dbr层中sio2层的厚度可以是800埃至1200埃,tio2层的厚度可以是500埃至900埃。

66.dbr层除了具有钝化作用外,还用于将从多量子阱层202射向第二钝化层33的光反射至基板10,提高出光效果。

67.可选地,如图1所示,红光微型发光二极管芯片还包括:第一焊点块71和第二焊点块72,第一焊点块71和第二焊点块72均位于第二钝化层33的表面。

68.如图1所示,第二钝化层33的表面具有露出第一电极41的第一过孔61,第二钝化层33的表面具有露出第二电极42的第二过孔62,第一焊点块71通过第一过孔61与第一电极41

相连,第二焊点块72通过第二过孔62与第二电极42相连,第一焊点块71、第二焊点块72均与金属增强层32绝缘。

69.通过在第二钝化层33的表面设置与第一电极41连接的第一焊点块71,便于第一电极41的通电连接;在第二钝化层33的表面设置与第二电极42连接的第二焊点块72,便于第二电极42的通电连接。

70.图7是本公开实施例提供的一种微型发光二极管芯片的俯视图。如图7所示,第一焊点块71和第二焊点块72均为矩形块,增大面积,便于导电。且在第二钝化层33的表面上,第一焊点块71和第二焊点块72间隔分布。

71.可选地,基板10为蓝宝石基板10。蓝宝石基板10透光率比较高,即基板10为透明基板10。且蓝宝石材料比较坚硬,化学特性比较稳定,使红光发光二极管具有良好的发光效果和稳定性。

72.本公开实施例中,第一半导体层201和第二半导体层203中的一个为p型层,第一半导体层201和第二半导体层203中的另一个为n型层。

73.作为一种示例,第一半导体层201为n型层,第一电极41为n型电极。第二半导体层203为p型层,第二电极42为p型电极。

74.可选地,第一半导体层201为的n型algainp层。n型algainp层的厚度可为0.5μm至3μm。

75.可选地,多量子阱层202包括交替生长的algainp量子阱层和algainp量子垒层。其中,多量子阱层202可以包括交替层叠的3至8个周期的algainp量子阱层和algainp量子垒层,algainp量子阱层和algainp量子垒层中的al含量不同。

76.作为示例,本公开实施例中,多量子阱层202包括交替层叠的5个周期的algainp量子阱层和algainp量子垒层。

77.可选地,多量子阱层202的厚度可以为150nm至200nm。

78.可选地,第二半导体层203为p型alinp层。p型alinp层的厚度可为0.5μm至3μm。

79.图8是本公开实施例提供的一种红光微型发光二极管芯片的制备方法的流程图。该方法用于制备图1所示的红光微型发光二极管芯片。如图8所示,该制备方法包括:

80.s11:提供一基板10。

81.s12:在基板10上形成外延结构20。

82.其中,外延结构20包括依次层叠于基板10上的第一半导体层201、多量子阱层202和第二半导体层203,第二半导体层203的表面具有露出第一半导体层201的凹槽51。

83.s13:在外延结构20的表面形成第一电极41和第二电极42。

84.其中,在外延结构20的表面形成第一电极41和第二电极42。

85.s14:在外延结构20上形成第一钝化层31和金属增强层32。

86.其中,第一钝化层31至少覆盖第一半导体层201、第一电极41、凹槽51、第二半导体层203、第二电极42的表面,金属增强层32位于第一钝化层31上,金属增强层32在基板10上的正投影位于第一钝化层31在基板10上的正投影内。

87.本公开实施例提供的红光微型发光二极管中,在基板10上设有外延结构20,外延结构20中第二半导体层203上具有露出第一半导体层201的凹槽51,第一电极41设置在凹槽51内与第一半导体层201相连,第二电极42设置在第二半导体层203上,外延结构20上覆盖

有一层第一钝化层31,第一钝化层31至少覆盖第一半导体层201、第一电极41、凹槽51、第二半导体层203和第二电极42的表面,并且,在第一钝化层31外还覆盖有金属增强层32,金属增强层32在基板10上的正投影位于第一钝化层31在基板10上的正投影内,这样避免金属增强层32与两个电极相连,而导致两个电极短路。由于金属增强层32是设置在外延结构20的表面上的,即通过金属增强层32能有效加固下方的外延结构20的强度,这样在激光焊接导致温度剧烈变化在芯片内产生应力时,该金属增强层32能抵御应力,有效防止芯片中的外延结构20出现裂痕失效。

88.可选地,基板10为蓝宝石基板10。蓝宝石基板10透光率比较高,即基板10为透明基板10。且蓝宝石材料比较坚硬,化学特性比较稳定,使红光微型发光二极管芯片具有良好的发光效果和稳定性。

89.如图9所示,在步骤s12中生长的外延结构20包括:第一半导体层201、多量子阱层202和第二半导体层203。第一半导体层201、多量子阱层202和第二半导体层203依次层叠在基板10上,第二半导体层203的表面具有露出第一半导体层201的凹槽51。

90.生长外延结构20的过程可以包括:在gaas衬底上依次生长腐蚀截止层、第一半导体、alinp载流子限制层、多量子阱层202、第二半导体层203和窗口层。

91.在gaas衬底上生长完成外延结构20后,将外延结构20键合到基板10上,键合温度为300℃,并去除gaas衬底。

92.如图9所示,键合完成后,在第二半导体层203的表面刻蚀露出第一半导体层201的凹槽51,即完成步骤s12中在基板10上形成外延结构20的过程。

93.具体可以包括:采用干法刻蚀的方式将第二半导体层203的部分区域刻除,并刻蚀至露出第一半导体层201。刻蚀深度为1μm至2μm,例如,刻蚀1.5μm。

94.示例性地,第一半导体层201为n型algainp层。n型algainp层的厚度可为0.5μm至3μm。

95.示例性地,多量子阱层202包括交替生长的algainp量子阱层和algainp量子垒层。其中,多量子阱层202可以包括交替层叠的3至8个周期的algainp量子阱层和algainp量子垒层,algainp量子阱层和algainp量子垒层中的al含量不同。

96.作为示例,本公开实施例中,多量子阱层202包括交替层叠的5个周期的algainp量子阱层和algainp量子垒层。

97.可选地,多量子阱层202的厚度可以为150nm至200nm。

98.可选地,第二半导体层203为p型alinp层。p型alinp层的厚度可为0.5μm至3μm。

99.其中,第二半导体层203为p型alinp层。p型alinp层的厚度可为0.5μm至3μm。

100.示例性地,窗口层可以是gap层,gap层的厚度为2μm至5μm。作为示例,gap层为3μm。

101.在步骤s13形成两个电极前可以包括:采用干法刻蚀的方式在第二半导体层203的表面刻蚀过渡台阶槽,以在过渡台阶槽的表面和凹槽51的表面之间形成凸起结构53。

102.其中,过渡台阶槽从第二半导体层203的表面向第一半导体层201延伸,过渡台阶槽与基板10之间的间距大于凹槽51与基板10之间的间距。

103.在步骤s13中,如图10所示,形成第一电极41和第二电极42可以包括:采用负胶剥离的方式分别加工第一电极41和第二电极42。

104.如图10所示,第二电极42位于在第二半导体层203的表面,第一电极41位于凹槽51

的表面。

105.其中,第一电极41采用金锗为基层材料蒸镀,金锗合金蒸发时要保证蒸发的功率,避免蒸发时间超过5秒钟,以防止合金成分的偏离,并进行退火。第二电极42采用金铍为基层材料蒸镀。

106.如图10所示,步骤s14中,在外延结构20上形成第一钝化层31可以包括:在第一半导体层201、第一电极41、第二半导体层203、第二电极42和凹槽51的表面制作第一钝化层31,并在第一钝化层31上需要引出电流的地方开设露出第一电极41的第一过孔61,以及露出第二电极42的第二过孔62。

107.其中,第一钝化层31的厚度可以是2000埃至5000埃。例如,第一钝化层31的厚度为3000埃。

108.接着,在第一钝化层31上形成金属增强层32,并且,第一过孔61和第二过孔62位置不设置金属增强层32。

109.在步骤s14之后,如图1所示,还可以包括制作的第二钝化层33。

110.其中,第二钝化层33可以是dbr层,dbr层包括多个周期性交替层叠的sio2层和tio2层。且dbr层的周期数可以在20至50之间。例如,dbr层的周期数为36。

111.其中,dbr层中sio2层的厚度可以是800埃至1200埃,tio2层的厚度可以是500埃至900埃。

112.制作第二钝化层33后还可以包括:在第二钝化层33上形成第一过孔61和第二过孔62,并在第二钝化层33的表面采用光刻的方式形成第一焊点块71,使得第一焊点块71通过第一过孔61与第一半导体层201连接;然后,在第二钝化层33的表面采用光刻的方式形成第二焊点块72,使得第二焊点块72通过第二过孔62与第二半导体层203连接。

113.其中,两焊点块均可以包括依次层叠的cr层、al层、ti层、ni层和au层。

114.示例性地,cr层的厚度为100埃、al层的厚度为3000埃、ti层的厚度为500埃、ni层的厚度为2000埃、au层的厚度为90000埃。

115.如图1所示,形成第一焊点块71和第二焊点块72后,可以在第二钝化层33的表面制作保护层80,且保护层80从第二钝化层33的表面延伸至基板10。

116.示例性地,本公开实施例中,保护层80可以是氧化硅层,氧化硅层的厚度为2000埃。

117.需要说明的是,在第二钝化层33的表面生长保护层80后,可以采用光刻技术在保护层80表面刻蚀出露出焊点块的通孔,以便于通电连接。

118.最后,减薄蓝宝石基板10,减薄后的最终厚度为80μm,然后,对蓝宝石进行隐形切割划裂,隐形切割划裂可以较好的减少亮度的损失。然后,测试得到微型发光二极管芯片。

119.以上所述仅为本公开的可选实施例,并不用以限制本公开,凡在本公开的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本公开的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1