一种多模块综合实现天线阵列参数快速切换的方法与流程

1.本发明属于微波暗室仿真天线阵列控制领域,更具体的说涉及一种多模块综合实现天线阵列参数快速切换的方法。

背景技术:

2.微波暗室目前是制导系统研制体系中的重要组成部分,其以半实物仿真的方式构建了考评制导系统性能指标的体系,可以高效、灵活、重复的对制导系统的性能指标进行测试和评估,解决了外场实际测试的费用高昂、试验条件难以满足等问题。

3.射频仿真机与仿真实验控制台根据被测导引头所需测试的性能指标构建虚拟的仿真电磁环境,通过一系列公式计算得到相关控制参数,然后途经校准系统下发给转台控制机,操纵转台来控制被测导引头的指向。同时,控制参数途经角度控制机、目标及环境模拟器等下发给馈电系统,由馈电系统控制天线阵列生成虚拟目标的电磁特性。天线阵列的基本单元是三元组天线,操作人员可以根据“幅度重心公式”通过控制电磁信号的幅度、相位以及切换天线开关等操作,实现基于三元组天线的等效辐射中心。多组三元组天线构成整个天线阵列,最终实现虚拟目标的等效电磁辐射特性的生成,供导引头接收、测试使用。

4.如图1所示传统的天线阵列控制参数需要途经多个中间设备才传到馈电系统,设备之间常用网络接口进行数据通信,并且在馈电系统上,使用“逐个天线扫描”的方式完成所有天线的参数设置。可以看出,传统的天线参数设置方式在数据传输途径上较远,传输路径延时很大;在最末级的参数设置上,用“逐个扫描”的方式把所有天线参数轮置一遍的时间也很长,这样,将一组天线参数完全切换至另一组新的天线参数的时间就很长,也就是说,虚拟目标从一个状态变到另一个状态的时间也就很长。在早期仿真精度要求不高时,传统方式的切换时间可以满足要求,但随着制导系统的技术发展,仿真精度开始逐步提高要求,需要天线参数切换的时间间隔越来越小,传统的方式在切换时间上无法满足要求,因此仿真系统迫切需要在天线参数快速设置方面进行提升。

技术实现要素:

5.本发明针对在微波暗室仿真体系中日益增长的天线阵列参数快速切换的需求,提出了一种多模块综合实现的天线阵列参数快速切换的方法,采用多个高速通信模块以及大规模高速译码-设置模块,综合后可以将仿真实验控制台计算出的天线参数快速传输并采用并行方式一次性的设置到阵列中的所有天线,可以跟随系统高速切换天线状态也即虚拟目标电磁状态。

6.为了实现上述目的,本发明采用以下技术方案实现的:

7.所述的装置包括仿真实验控制台、pcie接收模块、光纤发送模块、大规模译码及并行设置模块、天线阵列;

8.所述多的仿真实验控制台通过pcie3.0总线与pcie接收模块连接,pcie接收模块通过与光纤发送模块连接;仿真实验控制台将角度控制机及目标环境模拟器整合在一起,

由仿真实验控制台完成全部的实时天线参数计算,并将天线参数数据送入pcie接收模块,pcie接收模块在将数据分发给不同的光纤发送模块;

9.光纤发送模块通过光纤与大规模译码及并行设置模块连接,每个光纤模块接收本组所有天线的参数,然后送至后级的大规模译码及并行设置模块;

10.大规模译码及并行设置模块分别与对应的天线组连接,大规模译码及并行设置模块经过串并转换,将串行光纤数据转换成并行参数,然后进行大规模译码,快速得到各个天线的并行控制参数,最后同时将所有控制参数并行设置给天线阵列。

11.优选地,所述的pcie接收模块、光纤发送模块设置于同一片fpga内,并靠近仿真控制台安装,大规模译码及并行设置模块靠近天线阵列前安装。

12.优选地,所述的天线阵列中的每一个天线分组都对应有一个光纤发送模块和大规模译码及并行设置模块。

13.优选地,所述的每个大规模译码及并行设置模块译出本组4套三元组天线,即共计12个天线的控制参数。

14.所述的天线阵列参数快速切换的方法采用以下步骤实现的:

15.步骤一:pcie高速通信模块接受仿真实验控制台的天线控制参数;

16.步骤二:多路光纤高速通信模块降步骤一种的天线控制参数并行发送给大规模译码及并行设置输出模块;

17.步骤三:大规模译码及并行设置输出模块将天线控制参数传输给相应的天线组。

18.优选地,所述的步骤一:pcie高速通信模块接受仿真实验控制台的天线控制参数,采用以下详细方法实现的:所述的pcie高速通信模块紧贴仿真实验控制台高算力计算机安装,pcie高速通信模块采用pcie3.0总线与多路光纤高速通信模块连接,pcie3.0

×

8接口模块直接使用fpga内嵌的具备完整标准pcie3.0协议的硬核,高速数据接收后,根据数据内嵌的天线组标识字分发给各个天线组参数,完成天线组参数数据转发。

19.优选地,所述的步骤二:多路光纤高速通信模块降步骤一种的天线控制参数并行发送给大规模译码及并行设置输出模块,是采用以下技术方案实现的:后级的光纤发送模块设计在pcie3.0

×

8接口模块同一片fpga中,内部采用fpga内嵌的紧凑数据线连接两个模块,使两个模块之间在fpga内仍保持高速通信,光纤发送模块直接使用fpga内嵌的高速串口通信硬核,支撑单通道光纤高速发送

20.优选地,所述的步骤三:大规模译码及并行设置输出模块将天线控制参数传输给相应的天线组是采用以下技术方案实现的:所述的大规模译码及并行设置输出模块放置在天线阵列前,接收光纤发来的串行数据,然后经过译码后得到各个天线的控制参数;大规模译码及并行设置输出模块内部包含所有天线分组参数的光纤接收模块,每个光纤模块接收本组所有天线的参数,然后送至后级的译码模块;每个译码模块译出本组4套三元组天线,即共计12个天线的控制参数。

21.优选地,所述的控制参数为每个天线的控制参数包括移相器控制码、数控衰减器控制码、天线开关控制码。

22.本发明有益效果:

23.经过综合使用pcie高速接收模块、高速光纤转发模块、大规模译码及并行设置模块后,以将仿真实验控制台计算出的天线参数快速传输并采用并行方式一次性的设置到阵

列中的所有天线,可以跟随系统高速切换天线状态也即虚拟目标电磁状态;天线阵列参数从计算输出到实际设置进天线阵列的时间相比于传统方法大大缩小,解决了微波暗室仿真体系中的天线阵列参数切换速度不足的问题。

附图说明

24.图1为微波暗室主要构成框图;

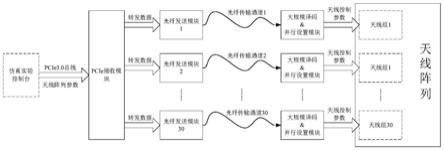

25.图2为本发明各模块组成框图;

26.图3为pcie高速接收模块框图;

27.图4为光纤发送模块框图;

28.图5为大规模译码及并行设置模块框图。

具体实施方式

29.下面将结合本发明实施例和附图,对本发明实施例中的技术方案进行清楚、完整地描述。

30.所述的装置包括仿真实验控制台、pcie接收模块、光纤发送模块、大规模译码及并行设置模块、天线阵列;

31.所述多的仿真实验控制台通过pcie3.0总线与pcie接收模块连接,pcie接收模块通过与光纤发送模块连接;仿真实验控制台将角度控制机及目标环境模拟器整合在一起,由仿真实验控制台完成全部的实时天线参数计算,并将天线参数数据送入pcie接收模块,pcie接收模块在将数据分发给不同的光纤发送模块;

32.光纤发送模块通过光纤与大规模译码及并行设置模块连接,每个光纤模块接收本组所有天线的参数,然后送至后级的大规模译码及并行设置模块;

33.大规模译码及并行设置模块分别与对应的天线组连接,大规模译码及并行设置模块经过串并转换,将串行光纤数据转换成并行参数,然后进行大规模译码,快速得到各个天线的并行控制参数,最后同时将所有控制参数并行设置给天线阵列。

34.所述的pcie接收模块、光纤发送模块设置于同一片fpga内,并靠近仿真控制台安装,大规模译码及并行设置模块靠近天线阵列前安装。所述的天线阵列中的每一个天线分组都对应有一个光纤发送模块和大规模译码及并行设置模块。所述的每个大规模译码及并行设置模块译出本组4套三元组天线,即共计12个天线的控制参数。

35.如图2所示,首级高速通信模块选用pcie高速接口协议,取代传统方法使用的网络接口协议。pcie高速接口协议是一种高速串行计算机扩展总线标准,由英特尔在2001年提出,旨在替代旧有的总线标准。pcie总线采用差分对传输方式,具有一个rx接收对和tx发送对,全双工工作模式,传输速度极高。本发明选用第三代pcie3.0,单对传输速率可达2gb/s。pcie总线可以进行多通道传输,本发明选用8通道传输,pcie3.0

×

8的传输速率可达16gb/s,具有颠覆性的速度。

36.为了保证pcie高速性能,pcie高速通信模块在物理位置上紧贴仿真实验控制台高算力计算机,这样就与天线阵列相隔较远,在此之间需要使用较长的通信线缆把控制参数传递到天线阵列。本发明使用高速光纤通信模块进行参数传输,取代传统方法使用的网络线缆。高速光纤通信模块具有传输容量大、传输损耗小、铺设方便等优点,串行传输速率可

达12gb/s。从pcie高速通信模块接收的参数转发给高速光纤通信模块,经过串行转换后高速输出。

37.最后一级是大规模译码及并行设置模块,接收光纤馈入的天线参数。首先此模块经过串并转换,将串行光纤数据转换成并行参数,然后进行大规模译码,快速得到各个天线的并行控制参数,最后同时将所有控制参数并行设置给天线阵列,取代传统的逐个天线参数设置的操作,使天线参数末端设置的时间大大缩小。

38.实施例1

39.所述的天线阵列参数快速切换的方法采用以下步骤实现的:

40.步骤一:pcie高速通信模块接受仿真实验控制台的天线控制参数;

41.本发明所用的pcie高速接收模块、高速光纤转发模块、大规模译码及并行设置模块均基于高性能fpga实现。高性能fpga具有基于28nm逻辑工艺生产制造,其接口速率理论上可以达到1ghz@ddr,实际工程上可以稳定工作在800mhz@ddr,完全可以对接所需要使用的pcie和光纤高速接口。fpga由于采用28nm逻辑工艺,使得其内部时钟网络可以工作在最高800mhz的时钟速率,即使附加上组合逻辑引入的延时,也可以很方便的实现超高速通信数据速率;fpga还具有丰富的可编程逻辑资源,在大规模译码及并行逻辑控制上完全满足使用要求。

42.如图3所示,pcie3.0

×

8接口模块直接使用fpga内嵌的具备完整标准pcie3.0协议的硬核。高速数据接收后,根据数据内嵌的天线组标识字分发给各个天线组参数,完成天线组参数数据转发。

43.步骤二:多路光纤高速通信模块降步骤一种的天线控制参数并行发送给大规模译码及并行设置输出模块;如图4所示,为了不浪费pcie3.0

×

8接口模块的高速性能,本发明将后级的光纤发送模块设计在pcie3.0

×

8接口模块同一片fpga中,内部采用fpga内嵌的紧凑数据线连接两个模块,使两个模块之间在fpga内仍保持高速通信。光纤发送模块直接使用fpga内嵌的高速串口通信硬核,支撑单通道光纤高速发送。

44.步骤三:大规模译码及并行设置输出模块将天线控制参数传输给相应的天线组。

45.如图5所示,大规模译码及并行设置模块的物理位置放置在天线阵列前,接收光纤发来的串行数据,然后经过译码后得到各个天线的控制参数,

46.模块内部包含所有天线分组参数的光纤接收模块,每个光纤模块接收本组所有天线的参数,然后送至后级的译码模块。每个译码模块译出本组4套三元组天线,即共计12个天线的控制参数,每个天线参数包括移相器控制码、数控衰减器控制码、天线开关控制码等。天线分组间是并行的“接收-译码”架构,输出的各个天线参数相关控制码字也是并行输出至天线阵列。最终整个模块译出所有天线的参数控制码,形成一个庞大的并行输出控制信号,完成对天线阵列里的所有天线同时设置的操作。

47.应当理解的是,本发明的上述具体实施方式仅仅用于示例性说明或解释本发明的原理,而不构成对本发明的限制。因此,在不偏离本发明的精神和范围的情况下所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。此外,本发明所附权利要求旨在涵盖落入所附权利要求范围和边界、或者这种范围和边界的等同形式内的全部变化和修改例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1