终端结构及其制造方法、半导体器件与流程

1.本发明涉及半导体技术领域,特别涉及一种终端结构及其制造方法、半导体器件。

背景技术:

2.在半导体器件的终端技术中,横向变掺杂(variation of lateral doping,vld)终端技术,因终端效率比较高,被广泛应用。一般终端会采用在尾部增加截止环的方式阻止耗尽区耗尽。

3.参阅图1,半导体器件的终端结构形成于n型的衬底11中的终端区a1,n型的衬底11还包含终端区a1所围绕的元胞区(未图示),元胞区和终端区a1之间的过渡区a2中形成有栅极结构14,终端区a1的外围是划片道(未图示);终端区a1中形成有p型的vld分压环12,vld分压环12从过渡区a2向终端区a1的远离元胞区的一端方向延伸,终端区a1的远离元胞区的一端形成有p型的截止环13,以阻止n型的衬底11与p型的vld分压环12形成的耗尽区15耗尽。但是,由于截止环13是与元胞区的体区(未图示)一起离子注入形成,导致截止环13的结深比vld分压环12的最靠近截止环13的部分的深度浅很多(例如截止环13的结深仅3μm左右),截止环13只能阻挡衬底11表面耗尽,无法阻挡衬底11内部耗尽区15的移动,进而导致耗尽区15会从截止环13(如图1所示)的下方穿过而耗尽到划片道,从而导致形成漏电通道;而若要避免形成漏电通道,则需要增大vld分压环12与截止环13的间距,从而增大耗尽区15与截止环13的间距而避免形成漏电通道,但会导致终端区a1的宽度增大,从而导致成本增大。

4.因此,如何在避免耗尽区耗尽到划片道而形成漏电通道的同时,还能减小终端区的宽度是目前亟需解决的问题。

技术实现要素:

5.本发明的目的在于提供一种的终端结构及其制造方法、半导体器件,在避免耗尽区耗尽到划片道而形成漏电通道的同时,还能减小终端区的宽度。

6.为实现上述目的,本发明提供了一种终端结构,位于一衬底的终端区,所述衬底还包括元胞区,所述终端区围绕所述元胞区;所述终端结构包括:

7.vld分压环,形成于所述终端区的靠近所述元胞区的一端且向远离所述元胞区的另一端方向延伸,所述vld分压环包括多个连接的掺杂环;

8.沟槽截止环,形成于所述终端区的远离所述元胞区的所述另一端,所述沟槽截止环与所述vld分压环之间间隔所述衬底,所述沟槽截止环的深度大于或等于最靠近所述沟槽截止环的掺杂环的深度。

9.可选地,所述终端结构还包括掺杂截止环,所述掺杂截止环位于所述沟槽截止环底面和侧面的衬底中,以使得所述掺杂截止环包围所述沟槽截止环,所述掺杂截止环与所述vld分压环之间间隔所述衬底。

10.可选地,所述元胞区形成有栅极结构,所述栅极结构与所述沟槽截止环的深度相

同。

11.可选地,所述终端结构还包括:

12.漂移区,形成于所述衬底中,所述漂移区包围所述vld分压环、所述沟槽截止环和所述掺杂截止环。

13.可选地,所述沟槽截止环的材质为掺杂的多晶硅,且所述沟槽截止环的掺杂浓度大于所述漂移区的掺杂浓度。

14.可选地,所述掺杂截止环的掺杂浓度大于所述漂移区的掺杂浓度。

15.可选地,所述vld分压环具有第一导电类型,所述沟槽截止环、所述掺杂截止环和所述漂移区具有第二导电类型。

16.本发明还提供了一种终端结构的制造方法,所述终端结构位于一衬底的终端区,所述衬底还包括元胞区,所述终端区围绕所述元胞区;所述终端结构的制造方法包括:

17.形成vld分压环于所述终端区的靠近所述元胞区的一端,且所述vld分压环向所述终端区的远离所述元胞区的另一端方向延伸,所述vld分压环包括多个连接的掺杂环;

18.形成沟槽截止环于所述终端区的远离所述元胞区的所述另一端,所述沟槽截止环与所述vld分压环之间间隔所述衬底,所述沟槽截止环的深度大于或等于最靠近所述沟槽截止环的掺杂环的深度。

19.可选地,所述终端结构的制造方法还包括:

20.形成掺杂截止环于所述沟槽截止环底面和侧面的衬底中,以使得所述掺杂截止环包围所述沟槽截止环,所述掺杂截止环与所述vld分压环之间间隔所述衬底。

21.可选地,形成所述沟槽截止环和所述掺杂截止环的步骤包括:

22.形成第一沟槽于所述终端区的远离所述元胞区的所述另一端的衬底中;

23.填充含有掺杂离子的多晶硅层于所述第一沟槽中;

24.执行退火工艺,以使得所述多晶硅层形成为所述沟槽截止环,以及使得所述掺杂离子扩散至所述沟槽截止环底面和侧面的衬底中形成为所述掺杂截止环。

25.可选地,在形成所述第一沟槽于所述终端区的远离所述元胞区的所述另一端的衬底中的同时,还形成第二沟槽于所述元胞区的衬底中;在所述第二沟槽中形成栅极结构。

26.可选地,在形成所述vld分压环于所述终端区的靠近所述元胞区的一端之前,所述终端结构的制造方法还包括:

27.形成漂移区于所述衬底中,所述漂移区包围所述vld分压环、所述沟槽截止环和所述掺杂截止环。

28.可选地,所述沟槽截止环的掺杂浓度大于所述漂移区的掺杂浓度。

29.可选地,所述掺杂截止环的掺杂浓度大于所述漂移区的掺杂浓度。

30.可选地,所述vld分压环具有第一导电类型,所述沟槽截止环、所述掺杂截止环和所述漂移区具有第二导电类型。

31.本发明还提供了一种半导体器件,包括位于一衬底中的元胞区和围绕所述元胞区的终端区,所述终端区形成有所述的终端结构。

32.与现有技术相比,本发明的技术方案具有以下有益效果:

33.1、本发明的终端结构,由于包括形成于终端区的靠近元胞区的一端且向远离所述元胞区的另一端方向延伸的vld分压环,所述vld分压环包括多个连接的掺杂环;以及包括

形成于所述终端区的远离所述元胞区的所述另一端的沟槽截止环,所述沟槽截止环与所述vld分压环之间间隔所述衬底,所述沟槽截止环通过沟槽填充的方式形成,所述沟槽截止环的深度大于或等于最靠近所述沟槽截止环的掺杂环的深度,使得能够避免耗尽区穿过沟槽截止环而耗尽到划片道,从而避免导致形成漏电通道;并且,能够减小耗尽区与所述沟槽截止环之间的距离,从而减小所述终端区的宽度,节省成本。

34.2、本发明的终端结构的制造方法,通过形成vld分压环于终端区的靠近元胞区的一端,且所述vld分压环向所述终端区的远离所述元胞区的另一端方向延伸,所述vld分压环包括多个连接的掺杂环;以及通过沟槽填充的方式形成沟槽截止环于所述终端区的远离所述元胞区的所述另一端,所述沟槽截止环与所述vld分压环之间间隔所述衬底,所述沟槽截止环的深度大于或等于最靠近所述沟槽截止环的掺杂环的深度,使得能够避免耗尽区穿过沟槽截止环而耗尽到划片道,从而避免导致形成漏电通道;并且,能够减小耗尽区与所述沟槽截止环之间的距离,从而减小所述终端区的宽度,节省成本。

35.3、本发明的半导体器件,由于包括位于一衬底中的元胞区和围绕所述元胞区的终端区,所述终端区形成有所述的终端结构,使得在避免所述半导体器件中形成漏电通道的同时,还能减小半导体器件的尺寸。

附图说明

36.图1是现有的终端结构的示意图;

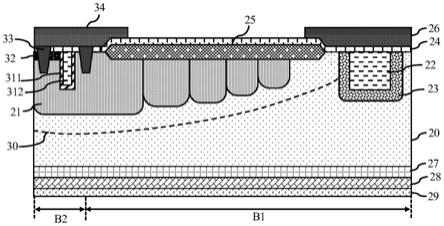

37.图2是本发明一实施例的终端结构的示意图;

38.图3是本发明一实施例的终端结构的制造方法的流程图;

39.图4a~图4h是图3所示的终端结构的制造方法中的器件示意图。

40.其中,附图1~图4h的附图标记说明如下:

41.11-衬底;12-vld分压环;13-截止环;14-栅极结构;15-耗尽区;

42.20-漂移区;21-vld分压环;22-沟槽截止环;221-第一沟槽;222-多晶硅层;23-掺杂截止环;24-绝缘介质层;25-氧化层;26-截止环金属;27-缓冲层;28-集电区;29-集电极金属;30-耗尽区;311-栅氧层;312-栅极层;313-第二沟槽;32-源极区;33-导电插塞;34-发射极金属。

具体实施方式

43.为使本发明的目的、优点和特征更加清楚,以下对本发明提出的终端结构及其制造方法、半导体器件作进一步详细说明。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

44.本发明一实施例提供一种终端结构,所述终端结构位于一衬底的终端区,所述衬底还包括元胞区,所述终端区围绕所述元胞区,所述终端区和所述元胞区之间为过渡区,所述终端区的外围环绕有划片道;所述终端结构包括:vld分压环,形成于所述终端区的靠近所述元胞区的一端且向远离所述元胞区的另一端方向延伸,所述vld分压环包括多个连接的掺杂环;沟槽截止环,形成于所述终端区的远离所述元胞区的所述另一端,所述沟槽截止环与所述vld分压环之间间隔所述衬底,所述沟槽截止环的深度大于或等于最靠近所述沟槽截止环的掺杂环的深度。

45.下面参阅图2更为详细的介绍本实施例的终端结构,图2是终端结构的纵向剖面示意图。

46.所述衬底的材质可以为本领域技术人员所熟知的任意合适的材料,例如单晶硅、锗化硅、碳化硅等。

47.所述vld(variation of lateral doping,横向变掺杂)分压环21形成于所述终端区b1的靠近所述元胞区(未图示)的一端,且所述vld分压环21向所述终端区b1的远离所述元胞区的另一端方向延伸,所述vld分压环21围绕所述元胞区;所述vld分压环21包括多个连接的掺杂环(在图2所示的实施例中,掺杂环的数量为5)。

48.所述终端区b1和所述元胞区之间为过渡区b2,所述vld分压环21的最靠近所述元胞区的掺杂环还可以从所述终端区b1延伸进入所述过渡区b2。

49.从所述终端区b1的靠近所述元胞区的一端至远离所述元胞区的另一端,多个连接的所述掺杂环的深度逐个减小、宽度逐个减小以及掺杂浓度逐个减小;或者,最靠近所述元胞区的掺杂环的深度最深、宽度最大以及掺杂浓度最大,其他各个掺杂环的深度、宽度以及掺杂浓度均相同且均对应小于最靠近所述元胞区的掺杂环的深度、宽度以及掺杂浓度。

50.所述衬底上可以形成氧化层25,部分厚度的所述氧化层25可以位于所述衬底中;所述氧化层25从最靠近所述元胞区的掺杂环的顶部向远离所述元胞区的方向延伸,以使得所述氧化层25覆盖最靠近所述元胞区的掺杂环的部分顶部以及其他所有掺杂环的顶部。

51.所述沟槽截止环22形成于所述终端区b1的远离所述元胞区的所述另一端,所述沟槽截止环22环绕所述vld分压环21;所述沟槽截止环22与所述vld分压环21之间间隔所述衬底,所述沟槽截止环22的深度大于或等于最靠近所述沟槽截止环22的掺杂环的深度。

52.所述沟槽截止环22的材质为掺杂的多晶硅,即通过沟槽填充掺杂的多晶硅的方式形成所述沟槽截止环22。

53.所述终端结构还可包括掺杂截止环23,所述掺杂截止环23位于所述沟槽截止环22底面和侧面的衬底中,以使得所述掺杂截止环23包围所述沟槽截止环22,所述掺杂截止环23与所述vld分压环21之间间隔所述衬底。由于所述沟槽截止环22的深度大于或等于最靠近所述沟槽截止环22的掺杂环的深度,那么,所述掺杂截止环23的深度大于最靠近所述沟槽截止环22的掺杂环的深度。

54.另外,所述过渡区b2以及所述元胞区的衬底中还形成有栅极结构,所述栅极结构的深度可以与所述沟槽截止环22的深度相同,且最靠近所述元胞区的掺杂环可以包围所述过渡区b2中的栅极结构。所述栅极结构包括栅氧层311和栅极层312,所述栅极层312的材质为多晶硅。

55.所述沟槽截止环22的宽度大于所述栅极结构的宽度,例如所述沟槽截止环22的宽度为4μm~5μm,所述栅极结构的宽度为0.7μm~0.9μm。

56.所述终端结构还包括漂移区20,所述漂移区20形成于所述衬底中,所述漂移区20包围所述vld分压环21、所述沟槽截止环22和所述掺杂截止环23。

57.其中,所述沟槽截止环22的掺杂浓度大于所述漂移区20的掺杂浓度。若所述终端结构还包括所述掺杂截止环23,则优选所述掺杂截止环23的掺杂浓度也大于所述漂移区20的掺杂浓度。

58.所述终端结构还可包括:绝缘介质层24,覆盖于所述衬底的顶面。所述绝缘介质层

24从所述终端区b1上延伸至所述过渡区b2上;所述绝缘介质层24将所述vld分压环21、所述氧化层25、所述沟槽截止环22、所述掺杂截止环23和所述栅极结构掩埋在内;截止环金属26,形成于所述沟槽截止环22上方的绝缘介质层24上,所述截止环金属26与所述沟槽截止环22之间绝缘。

59.另外,所述过渡区b2和所述元胞区的衬底顶部还形成有源极区32;所述过渡区b2以及过渡区b2与终端区b1的交界处形成有多个导电插塞33,所述导电插塞33贯穿所述绝缘介质层24进入所述衬底中,所述过渡区b2的绝缘介质层24上形成有与所述导电插塞33电连接的发射极金属34,所述发射极金属34通过导电插塞33与所述源极区32和最靠近所述元胞区的掺杂环电连接。

60.所述终端结构还可包括:

61.缓冲层27,形成于所述漂移区20底面的衬底中;

62.集电区28,形成于所述缓冲层27底面的衬底中;

63.集电极金属29,形成于所述衬底的底面。

64.其中,所述vld分压环21和所述集电区28具有第一导电类型,所述衬底、所述沟槽截止环22、所述掺杂截止环23、所述漂移区20、所述源极区32和所述缓冲层27具有第二导电类型。所述第一导电类型为p型,所述第二导电类型为n型;或者,所述第一导电类型为n型,所述第二导电类型为p型。在工作状态下,具有第一导电类型的所述vld分压环21与具有第二导电类型的所述漂移区20形成耗尽区30。

65.综上所述,本发明提供的终端结构中,由于包括形成于所述终端区b1的远离所述元胞区的所述另一端的沟槽截止环22,所述沟槽截止环22通过沟槽填充的方式形成,所述沟槽截止环22的深度大于或等于所述vld分压环21中最靠近所述沟槽截止环22的掺杂环的深度,使得与图1所示的离子注入形成的深度很浅的截止环13相比,本发明的耗尽区30在耗尽到划片道之前能够与沟槽截止环22接触,使得耗尽区30被沟槽截止环22截止,避免耗尽区30穿过沟槽截止环22而耗尽到划片道,从而避免导致形成漏电通道;并且,能够减小耗尽区30与所述沟槽截止环22之间的距离,从而减小所述终端区b1的宽度,节省成本。

66.其中,当耗尽区30在耗尽到与沟槽截止环22接触时,由于所述沟槽截止环22的掺杂浓度大于所述漂移区20的掺杂浓度,使得导电类型为n型的区域的掺杂浓度增大,进而使得耗尽区30的宽度变小,耗尽区30很快耗尽,即耗尽区30被沟槽截止环22截止,避免了耗尽区30耗尽到划片道。

67.进一步地,若所述终端结构还包括所述掺杂截止环23,由于所述掺杂截止环23的深度大于最靠近所述沟槽截止环22的掺杂环的深度,且所述掺杂截止环23的掺杂浓度大于所述漂移区20的掺杂浓度,使得耗尽区30在耗尽到划片道之前能够与所述掺杂截止环23和所述沟槽截止环22接触,导电类型为n型的区域的掺杂浓度增大,进而使得所述沟槽截止环22和所述掺杂截止环23能够共同对所述耗尽区30的耗尽进行截止,从而使得截止效果进一步提高。

68.本发明一实施例提供一种终端结构的制造方法,所述终端结构位于一衬底的终端区,所述衬底还包括元胞区,所述终端区围绕所述元胞区,所述终端区和所述元胞区之间为过渡区,所述终端区的外围环绕有划片道;参阅图3,图3是本发明一实施例的终端结构的制造方法的流程图,所述终端结构的制造方法包括:

69.步骤s1,形成vld分压环于所述终端区的靠近所述元胞区的一端,且所述vld分压环向所述终端区的远离所述元胞区的另一端方向延伸,所述vld分压环包括多个连接的掺杂环;

70.步骤s2,形成沟槽截止环于所述终端区的远离所述元胞区的所述另一端,所述沟槽截止环与所述vld分压环之间间隔所述衬底,所述沟槽截止环的深度大于或等于最靠近所述沟槽截止环的掺杂环的深度。

71.下面参阅图4a~图4h更为详细的介绍本实施例提供的终端结构的制造方法,图4a~图4h也是终端结构的纵向剖面示意图。

72.按照步骤s1,参阅图4a,形成vld(variation of lateral doping,横向变掺杂)分压环21于所述终端区b1的靠近所述元胞区(未图示)的一端,且所述vld分压环21向所述终端区b1的远离所述元胞区的另一端方向延伸,所述vld分压环21围绕所述元胞区;所述vld分压环21包括多个连接的掺杂环(在图4a所示的实施例中,掺杂环的数量为5)。

73.所述终端区b1和所述元胞区之间为过渡区b2,所述vld分压环21的最靠近所述元胞区的掺杂环还可以从所述终端区b1延伸进入所述过渡区b2。

74.从所述终端区b1的靠近所述元胞区的一端至远离所述元胞区的另一端,多个连接的所述掺杂环的深度逐个减小、宽度逐个减小以及掺杂浓度逐个减小;或者,最靠近所述元胞区的掺杂环的深度最深、宽度最大以及掺杂浓度最大,其他各个掺杂环的深度、宽度以及掺杂浓度均相同且均对应小于最靠近所述元胞区的掺杂环的深度、宽度以及掺杂浓度。

75.以最靠近所述元胞区的掺杂环的深度最深、宽度最大以及掺杂浓度最大为例,形成所述vld分压环21的步骤可以包括:首先,形成第一图形化的光刻胶层(未图示)于所述衬底上,所述第一图形化的光刻胶层具有多个用于形成掺杂环的离子注入窗口,各个离子注入窗口的宽度相同,执行第一次离子注入,以在离子注入窗口暴露出的衬底中形成多个离子注入区,各个离子注入区之间有间隙;然后,形成氧化层25于所述衬底上,部分厚度的所述氧化层25可以位于所述衬底中,所述氧化层25从最远离所述元胞区的离子注入区上向所述元胞区的方向延伸,以使得所述氧化层25覆盖最靠近所述元胞区的离子注入区之外的其他离子注入区,所述氧化层25未覆盖最靠近所述元胞区的离子注入区;然后,以所述氧化层25为掩模,向最靠近所述元胞区的离子注入区进行第二次离子注入,使得最靠近所述元胞区的离子注入区的掺杂浓度大于其他离子注入区的掺杂浓度;然后,执行退火工艺,以使得各个离子注入区中的离子进行扩散后使得相邻的离子注入区之间相互重叠连接,进而对应形成各个连接在一起的掺杂环,且各个掺杂环的深度对应大于各个离子注入区的深度。其中,由于最靠近所述元胞区的离子注入区还进行了第二次的离子注入,使得最靠近所述元胞区的掺杂环与其他掺杂环相比深度更深、宽度更大以及掺杂浓度更大。

76.按照步骤s2,形成沟槽截止环22于所述终端区b1的远离所述元胞区的所述另一端,所述沟槽截止环22环绕所述vld分压环21;所述沟槽截止环22与所述vld分压环21之间间隔所述衬底,所述沟槽截止环22的深度大于或等于最靠近所述沟槽截止环22的掺杂环的深度。

77.形成所述沟槽截止环22的步骤包括:首先,参阅图4b,形成第一沟槽221于所述终端区b1的远离所述元胞区的所述另一端的衬底中;然后,参阅图4d,填充含有掺杂离子的多晶硅层222于所述第一沟槽221中,所述多晶硅层222覆盖所述衬底、所述氧化层25和所述

vld分压环21;然后,参阅图4e,去除高于所述衬底顶面的多晶硅层222,使得所述第一沟槽221中的多晶硅层222形成为所述沟槽截止环22。

78.所述终端结构的制造方法还可包括:形成掺杂截止环23于所述沟槽截止环22底面和侧面的衬底中,以使得所述掺杂截止环23包围所述沟槽截止环22,所述掺杂截止环23与所述vld分压环21之间间隔所述衬底。由于所述沟槽截止环22的深度大于或等于最靠近所述沟槽截止环22的掺杂环的深度,那么,所述掺杂截止环23的深度大于最靠近所述沟槽截止环22的掺杂环的深度。

79.若所述终端结构还包括所述掺杂截止环23,则形成所述沟槽截止环22和所述掺杂截止环23的步骤可以包括:首先,参阅图4b,形成第一沟槽221于所述终端区b1的远离所述元胞区的所述另一端的衬底中;然后,参阅图4d,填充多晶硅层222于所述第一沟槽221中,所述多晶硅层222覆盖所述衬底、所述氧化层25和所述vld分压环21,且所述多晶硅层222含有掺杂离子;然后,参阅图4e,去除高于所述衬底顶面的多晶硅层222,仅保留所述第一沟槽221中的多晶硅层222;然后,参阅图4f,执行退火工艺,以使得所述第一沟槽221中的多晶硅层222形成为所述沟槽截止环22,以及使得所述掺杂离子扩散至所述沟槽截止环22底面和侧面的衬底中形成为所述掺杂截止环23,所述掺杂截止环23包围所述沟槽截止环22,所述掺杂截止环23与所述vld分压环21之间间隔所述衬底。其中,退火工艺的温度可以为1100℃~1200℃,时间可以为90min~110min;需要说明的是,退火工艺的温度和时间不仅限于上述的范围,可根据所述掺杂截止环23的深度和宽度需求进行调整。

80.另外,参阅图4b,在形成所述第一沟槽221于所述终端区b1的远离所述元胞区的所述另一端的衬底中的同时,还可形成第二沟槽313于所述过渡区b2以及所述元胞区的衬底中,所述第一沟槽221与所述第二沟槽313的深度相同,且最靠近所述元胞区的掺杂环可以包围所述过渡区b2中的第二沟槽313;参阅图4c,在填充所述多晶硅层222于所述第一沟槽221中之前,可以先形成栅氧层311于所述第二沟槽313的内壁上;参阅图4d和图4e,在填充所述多晶硅层222于所述第一沟槽221中的同时,所述多晶硅层222还填充于所述第二沟槽313中,以使得在去除高于所述衬底顶面的多晶硅层222之后,所述第二沟槽313中的多晶硅层222作为栅极层312,进而在所述第二沟槽313中形成栅极结构,所述栅极结构包括所述栅氧层311和所述栅极层312。其中,由于同时形成所述第一沟槽221和所述第二沟槽313,且同时填充多晶硅层222于所述第一沟槽221和所述第二沟槽313中,使得能够简化工艺步骤。

81.其中,所述第一沟槽221的宽度(即所述沟槽截止环22的宽度)大于所述第二沟槽313的宽度,例如所述第一沟槽221的宽度为4μm~5μm,所述第二沟槽313的宽度为0.7μm~0.9μm。

82.另外,在形成所述vld分压环21于所述终端区b1的靠近所述元胞区的一端之前,所述终端结构的制造方法还包括:参阅图4a,形成漂移区20于所述衬底中,所述漂移区20包围所述vld分压环21、所述沟槽截止环22和所述掺杂截止环23。

83.其中,所述沟槽截止环22的掺杂浓度大于所述漂移区20的掺杂浓度。若所述终端结构还包括所述掺杂截止环23,则优选所述掺杂截止环23的掺杂浓度也大于所述漂移区20的掺杂浓度。

84.并且,所述终端结构的制造方法还包括:参阅图4g,形成绝缘介质层24覆盖于所述衬底的顶面。所述绝缘介质层24从所述终端区b1上延伸至所述过渡区b2上;所述绝缘介质

层24将所述vld分压环21、所述氧化层25、所述沟槽截止环22、所述掺杂截止环23和所述栅极结构掩埋在内。

85.另外,参阅图4f,在形成所述掺杂截止环23之后且在形成所述绝缘介质层24之前,可以形成源极区32于所述过渡区b2和所述元胞区中;参阅图4g,在形成所述绝缘介质层24之后,可以形成接触孔(未图示)于所述过渡区b2以及过渡区b2与终端区b1的交界处,并向接触孔中填充金属且金属覆盖在所述绝缘介质层24上,通过对金属进行刻蚀后在所述过渡区b2的绝缘介质层24上形成发射极金属34以及在所述沟槽截止环22上方的绝缘介质层24上形成截止环金属26,所述接触孔中形成导电插塞33,所述发射极金属34通过导电插塞33与所述源极区32和最靠近所述元胞区的掺杂环电连接,所述截止环金属26与所述沟槽截止环22之间绝缘。

86.并且,参阅图4h,在形成所述发射极金属34和所述截止环金属26之后,所述终端结构的制造方法还包括:

87.形成缓冲层27于所述漂移区20底面的衬底中;

88.形成集电区28于所述缓冲层27底面的衬底中;

89.形成集电极金属29于所述衬底的底面。

90.其中,所述vld分压环21和所述集电区28具有第一导电类型,所述衬底、所述沟槽截止环22、所述掺杂截止环23、所述漂移区20、所述源极区32和所述缓冲层27具有第二导电类型。所述第一导电类型为p型,所述第二导电类型为n型;或者,所述第一导电类型为n型,所述第二导电类型为p型。参阅图4h,在工作状态下,具有第一导电类型的所述vld分压环21与具有第二导电类型的所述漂移区20形成耗尽区30。

91.综上所述,本发明提供的终端结构的制造方法中,由于通过沟槽填充的方式形成沟槽截止环22于所述终端区b1的远离所述元胞区的所述另一端,所述沟槽截止环22的深度大于或等于所述vld分压环21中最靠近所述沟槽截止环22的掺杂环的深度,使得与图1所示的离子注入形成的深度很浅的截止环13相比,本发明的耗尽区30在耗尽到划片道之前能够与沟槽截止环22接触,使得耗尽区30被沟槽截止环22截止,避免耗尽区30穿过沟槽截止环22而耗尽到划片道,从而避免导致形成漏电通道;并且,能够减小耗尽区30与所述沟槽截止环22之间的距离,从而减小所述终端区b1的宽度,节省成本。

92.其中,当耗尽区30在耗尽到与沟槽截止环22接触时,由于所述沟槽截止环22的掺杂浓度大于所述漂移区20的掺杂浓度,使得导电类型为n型的区域的掺杂浓度增大,进而使得耗尽区30的宽度变小,耗尽区30很快耗尽,即耗尽区30被沟槽截止环22截止,避免了耗尽区30耗尽到划片道。

93.进一步地,若所述终端结构还包括所述掺杂截止环23,由于所述掺杂截止环23的深度大于最靠近所述沟槽截止环22的掺杂环的深度,且所述掺杂截止环23的掺杂浓度大于所述漂移区20的掺杂浓度,使得耗尽区30在耗尽到划片道之前能够与所述掺杂截止环23和所述沟槽截止环22接触,导电类型为n型的区域的掺杂浓度增大,进而使得所述沟槽截止环22和所述掺杂截止环23能够共同对所述耗尽区30的耗尽进行截止,从而使得截止效果进一步提高。

94.本发明一实施例提供一种半导体器件,包括位于一衬底中的元胞区和围绕所述元胞区的终端区,所述终端区的外围环绕有划片道;所述终端区形成有所述的终端结构。

95.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1