一种易于焊接的倒装LED芯片的制作方法

一种易于焊接的倒装led芯片

技术领域

1.本实用新型涉及发光二极管技术领域,尤其涉及一种易于焊接的倒装led芯片。

背景技术:

2.倒装led芯片凭借其具有良好的散热性能、电流分布均匀、高可靠性、高光效等突出特点,被广泛地应用于车用照明、家用照明、背光显示等领域。

3.倒装led芯片在封装应用时普遍使用ausn共晶焊接技术,无需打线固晶,大大降低了封装时间与成本;但是其对共晶焊接工艺要求较高,对装封装基板的选择、平整度、制作工艺的要求也很高。

4.现有倒装led芯片使用ausn共晶焊接技术焊接在封装基板上,会产生较高的空洞率(不良率),空洞率是指芯片焊盘电极金属与封装基板之间的焊接粘附效果,通过x

‑

ray扫描焊接粘附区域,若全部显示黑色,则焊接粘附效果好,空洞率小,良率高;若焊接粘附区域的局部区域表现为白色,则对应产生空洞情况,白色的区域越多,空洞率越高,良率越低;其中,空洞率等于白色区域与焊接粘附总区域的比例。

5.倒装led芯片的制备的过程中,外延层刻蚀、绝缘层刻蚀形成的孔洞,虽然在后续的工艺中会被其他结构,如电极、焊盘等结构所填平,但这些孔洞在倒装led芯片封装时会造成倒装led表面与封装基板之间粘附异常、产生大量空洞、焊接不良,引起光电参数异常、芯片剥离等现象。

技术实现要素:

6.本实用新型所要解决的技术问题在于,提供一种易于焊接的倒装led芯片,空洞率低,良率高。

7.为了解决上述技术问题,本实用新型提供了一种易于焊接的倒装led芯片,包括衬底、设于衬底上的发光结构、设于发光结构上第一电极、设于发光结构和第一电极上的钝化层、以及设于钝化层上第二电极,所述钝化层设有至少一个电极孔洞,所述电极孔洞内填充有导电物质,所述导电物质与钝化层的表面齐平,所述导电物质将第一电极和第二电极形成导电连接,所述导电物质的硬度≥80hbs。

8.作为上述方案的改进,所述导电物质选自镍、铬、钛、钨中的一种。

9.作为上述方案的改进,所述电极孔洞的侧壁与钝化层的表面具有预设的夹角θ1,所述夹角θ1为35~65

°

。

10.相应地,本实用新型还提供了一种易于焊接的倒装led芯片,包括衬底、设于衬底上的发光结构、设于发光结构上第一电极、设于发光结构和第一电极上的钝化层、以及设于钝化层上第二电极,所述钝化层设有至少两个电极孔洞,所述电极孔洞刻蚀至第一电极的表面,所述第二电极填充在所述电极孔洞内并与第一电极形成导电连接,所述第二电极设有至少两个填充孔洞,所述填充孔洞对应设置在电极孔洞的上方,所述填充孔洞内填充有导电物质,所述导电物质与第二电极的表面齐平,所述导电物质的硬度≥80hbs。

11.作为上述方案的改进,所述导电物质选自镍、铬、钛、钨中的一种。

12.作为上述方案的改进,所述填充孔洞的侧壁与第二电极的表面具有预设的夹角θ2,所述夹角θ2为35~65

°

。

13.相应地,本实用新型还提供了一种易于焊接的倒装led芯片,包括衬底、设于衬底上的发光结构、设于发光结构上第一电极、设于发光结构和第一电极上的钝化层、以及设于钝化层上第二电极,所述钝化层设有至少一个电极孔洞,所述第二电极设有至少一个填充孔洞,所述填充孔洞对应设置在电极孔洞的上方,所述电极孔洞和填充孔洞内均填充有导电物质,填充在电极孔洞内的导电物质与钝化层的表面齐平,并将第一电极和第二电极形成导电连接,填充在填充孔洞内的导电物质与第二电极的表面齐平,其中,所述导电物质的硬度≥80hbs。

14.作为上述方案的改进,所述导电物质选自镍、铬、钛、钨中的一种。

15.作为上述方案的改进,所述电极孔洞的侧壁与钝化层的表面具有预设的夹角θ1,所述夹角θ1为35~65

°

;

16.所述填充孔洞的侧壁与第二电极的表面具有预设的夹角θ2,所述夹角θ2为35~65

°

。

17.作为上述方案的改进,填充在电极孔洞和填充孔洞内的导电物质的厚度均为0.6~1.2μm。

18.实施本实用新型,具有如下有益效果:

19.本实用新型提供的一种易于焊接的倒装led芯片,在所述钝化层的电极孔洞内填充硬度≥80hbs导电物质,不仅将钝化层填平,还将第一电极和第二电极形成导电连接,更重要的是对第一电极和第二电极起到良好的支撑作用,解决了钝化层与第一电极和第二电极的金属硬度不同的问题,减少封装焊接时第二电极与封装基板之间的空洞率,提高芯片的焊接性能。

20.本实用新型将电极孔洞的侧壁与钝化层的表面设有预设的夹角θ1,并将夹角θ1的范围设为35~65

°

,这样可以避免导电物质与钝化层之间产生裂缝,进一步减少第二电极与封装基板之间的空洞率,提高芯片的焊接性能。

21.本实用新型提供的一种易于焊接的倒装led芯片,在第二电极上形成与电极孔洞位置对应的填充孔洞,并在填充可用的填充硬度≥80hbs导电物质,不仅将第二电极填平,还将第二电极和封装基板形成导电连接,更重要的是对第二电极起到良好的支撑作用,避免了第二电极在挤压时与封装基板产生缝隙,进而减少封装焊接时第二电极与封装基板之间的空洞率,提高芯片的焊接性能。

22.本实用新型将填充孔洞的侧壁与第二电极的设有预设的夹角θ2,并将夹角θ2的范围设为35~65

°

,这样可以避免导电物质与第二电极之间产生裂缝,进一步减少第二电极与封装基板之间的空洞率,提高芯片的焊接性能。

23.本实用新型提供的一种易于焊接的倒装led芯片,在所述钝化层的电极孔洞内填充硬度≥80hbs导电物质,并在第二电极上形成与电极孔洞位置对应的填充孔洞,并在填充可用的填充硬度≥80hbs导电物质,不仅将钝化层和第二电极填平,还将第一电极和第二电极形成导电连接,将第二电极和封装基板形成导电连接,更重要的是对第一电极和第二电极起到良好的支撑作用,解决了钝化层与第一电极和第二电极的金属硬度不同的问题,减

少封装焊接时第二电极与封装基板之间的空洞率,提高芯片的焊接性能。

附图说明

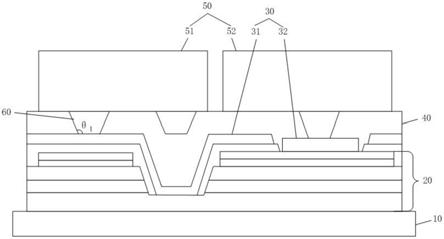

24.图1是本实用新型优选方案1的倒装led芯片的结构示意图;

25.图2是本实用新型所有方案的发光结构的结构示意图;

26.图3是本实用新型所有方案的第一电极形成在发光结构后的示意图;

27.图4是本实用新型所有方案的钝化层形成电极孔洞后的示意图;

28.图5是本实用新型所有方案的第二电极的结构示意图;

29.图6是本实用新型优选方案2的倒装led芯片的结构示意图;

30.图7是本实用新型优选方案2的第二电极形成填充孔洞后的示意图;

31.图8是本实用新型优选方案3的倒装led芯片的结构示意图;

32.图9是本实用新型优选方案3的第二电极形成填充孔洞后的示意图。

具体实施方式

33.为使本实用新型的目的、技术方案和优点更加清楚,下面将结合附图对本实用新型作进一步地详细描述。

34.参见图1,作为本实用新型的优选方案1,本实用新型提供的一种易于焊接的倒装led芯片,包括衬底10、设于衬底10上的发光结构20、设于发光结构20上第一电极30、设于发光结构20和第一电极30上的钝化层40、以及设于钝化层40上的第二电极50,所述钝化层40设有至少一个电极孔洞,所述电极孔洞内填充有导电物质60,所述导电物质60与钝化层40的表面齐平,所述导电物质60将第一电极30和第二电极50形成导电连接,所述导电物质60的硬度≥80hbs。

35.具体的,钝化层40是倒装led芯片的必要结构,其用于保护发光结构20,避免水汽、灰尘等进入发光结构20,同时避免芯片短路。为了保证第一电极30能够与第二电极50形成导电连接,必须对钝化层40进行刻蚀,以形成电极孔洞。现有的倒装led芯片直接将第二电极50的金属沉积在钝化层40的电极孔洞,以使第一电极30能够与第二电极50形成导电连接。但在封装焊接时,倒装led芯片上会施加一个下压力,由于钝化层40与第一电极30和第二电极50的金属硬度不同,因此第二电极50与封装基板上会产生大量的空洞,影响封装良率。

36.本实用新型的钝化层40由致密性好的绝缘层材料制成。优选的,所述钝化层40的材料选自sio2、tio5、sinx、sion中的一种。更优的,所述钝化层40为dbr层。

37.本实用新型将导电物质60填充在钝化层40的电极孔洞内,不仅要将钝化层40填平,还要将第一电极30和第二电极50形成导电连接,更重要的是本实用新型的导电物质60可以支撑第一电极30和第二电极50,减少封装焊接时第二电极50与封装基板之间的空洞率,提高芯片的焊接性能。

38.本实用新型的导电物质60要具有以下特性:(1)与钝化层40、第一电极30和第二电极50形成良好的粘接;(2)有良好的导电性能,将第一电极30和第二电极50形成上下导通;(3)与周围的结构具有相当的硬度,在芯片封装焊接时,只有导电物质60的硬度≥80hbs,导电物质60才不因为挤压而与周围的钝化层40、第一电极30和第二电极50产生缝隙,不会形

成新的空洞。

39.为了满足导电物质60的上述特性,本实用新型导电物质60选自镍、铬、钛、钨中的一种。

40.优选的,所述电极孔洞的形状为梯形,即所述电极孔洞的侧壁与钝化层40的表面具有预设的夹角θ1。其中,所述夹角θ1对于导电物质60的效果起着重要的作用;若夹角θ1太大,则导电物质60与钝化层40之间容易会产生裂缝,设置在导电物质60上的第二电极50容易与导电物质60断开;若夹角θ1太小,则电极孔洞的开口很宽,即电极孔洞的面积过大,这样会增加芯片的空洞率,降低芯片的焊接性。

41.优选的,所述夹角θ1为35~65

°

。更优的,所述夹角θ1为40~55

°

。

42.参见图2,本实用新型的发光结构20包括依次设置的外延层、透明导电层24、反射层25和保护层26,所述外延层包括依次设置的第一半导体层21、有源层22和第二半导体层23,其中,所述发光结构20还包括第一凹孔27和第二凹孔28,所述第一凹孔27从保护层26刻蚀至第一半导体层21,所述第二凹孔28从保护层26刻蚀至反射层25的表面。

43.参见图3,所述第一电极30包括n型第一电极31和p型第一电极32,所述n型第一电极31设置在保护层26和第一凹孔27的第一半导体层21上,所述p型第一电极32设置在第二凹孔28的反射层25上。所述保护层26用于隔开n型第一电极31和p型第一电极32,以防止芯片短路。优选的,所述保护层26由致密性好的绝缘层材料制成。优选的,所述保护层26的材料选自sio2、tio5、sinx、sion中的一种。

44.其中,位于第一凹孔27内的那部分n型第一电极31,其水平面高度略低于保护层26,形成第三凹孔33,本实用新型保护层26覆盖在第三凹孔33以外的发光结构20上。

45.参见图4,所述钝化层40设置在第一电极30上,并将第三凹孔33和第二凹孔28填平;其中,钝化层40的电极孔洞对应设置在第三凹孔33和第二凹孔28的上方,这样填充在电极孔洞内的导电物质60才起到良好的支撑作用,减少封装焊接时第二电极50与封装基板之间的空洞率,提高芯片的焊接性能。

46.具体的,所述电极孔洞包括第一电极孔洞41和第二电极孔洞,所述第一电极孔洞41对应设于第三凹孔33的上方,所述第二电极孔洞至少包括n型第二电极孔洞42和p型第二电极孔洞43,所述n型第二电极孔洞42刻蚀至n型第一电极31的表面,所述p型第二电极孔洞43刻蚀至p型第一电极32的表面。具体的,填充在n型第二电极孔洞42内的导电物质60与n型第一电极31导电连接,填充在p型第二电极孔洞43内的导电物质60与p型第一电极32导电连接,而填充在第一电极孔洞41内的导电物质60可以与n型第一电极31导电连接,也可以不与n型第一电极31导电连接,其主要取决于第一电极孔洞41的深度。为了减少空洞率,第一电极孔洞41和第二电极孔洞42的深度相同,因此填充在第一电极孔洞41内的导电物质60一般不与n型第一电极31形成导电连接。

47.其中,所述第二电极50包括n型第二电极51和p型第二电极52,所述n型第二电极51设置在第一电极孔洞41和n型第二电极孔洞42上,所述p型第二电极52设置在p型第二电极孔洞43上,其中,填充在n型第二电极孔洞42内的导电物质60将n型第二电极51和n型第一电极31形成导电连接,填充在p型第二电极孔洞43内的导电物质60将p型第二电极52导和p型第一电极32形成导电连接。

48.由此可知,导电物质60的厚度取决于电极孔洞的深度,电极孔洞的深度取决于钝

化层40的厚度,若钝化层40的厚度太薄,即导电物质60的厚度太薄,则芯片容易漏电,导电物质60的导电性会受到影响,从而影响芯片的电压,且导电物质60的填充效果下降,空洞率增加,焊接性降低;若钝化层40的厚度太厚,即导电物质60的厚度太厚,则成本增加,且导电物质60与钝化层40容易出现裂缝,空洞率反而增加,焊接性也下降。优选的,导电物质60的厚度为0.6~1.2μm。更优的,导电物质60的厚度为0.7~1.0μm。

49.本实用新型的第二电极50用于焊接封装,因此其面积受封装基板和封装工艺的影响,为了提高焊接效率和焊接效果,n型第二电极51和p型第二电极52的面积相等,且高度在同一水平面上。本实用新型的第一电极30用于芯片的电流扩展,起到降电压和提亮度的作用。优选的,第一电极30的材料选自cr、ni、al、ti、pt、au中的一种;第二电极50的材料选自cr、ni、al、ti、pt、au、sn中的一种。

50.由于第一电极30的底层需要与保护层26、外延层具有良好的粘接作用,因此第一电极30的底层选用cr或ti;而第一电极30的顶层需要在钝化层40刻蚀时具有保护下方金属的作用,且第一电极30的顶层需要与第二电极50、钝化层40具有良好的粘接作用,因此第一电极30的顶层选用pt、au、ti。优选的,所述第一电极30为cr/al/ti/pt/au/ti叠层结构,具有一定的反射率,可将外延层发出的光反射到衬底10一侧。

51.参见图5,所述第二电极50为叠层结构,包括导电层51和表层52,所述导电层51的材料选自cr、ni、al、ti、pt中的一种,所述表层52为叠层结构,包括多层sn/au叠层。

52.所述表层将纯金与纯锡复合形成sn/au叠层,通过不同比例的au、sn复合来消除表层的应力,提升表层金属和封装基板之间的润湿性能,从而降低表层和封装基板之间的封装空洞率。

53.具体的,当封装基板被加热至适合的共晶温度时,金或银元素会渗透到表层,以改变表层的组分,从而提高表层的熔点,令表层固化并将倒装led芯片紧固的焊接在封装基板上。本实用新型au

‑

sn共晶焊的优点包括:(1)降低热阻,锡(sn)和金(au)材料都是金属材料,导热好;(2)提供光效,led发光效率和热阻成反比;(3)提高效率,led共晶一次固晶成型;(4)粘结强度大于银胶固晶,大幅减少掉晶现象。

54.其中,sn/au叠层中sn的厚度和au的厚度决定了sn/au叠层中sn和au的比例,由于本实用新型的表层通过不同比例的ausn复合来消除表层的应力,提升表层金属和封装基板之间的润湿性能,从而降低表层和封装基板之间的封装空洞率,其中,au和sn的质量百分比在(15%~30%):(70%~85%)范围内,au和sn才能形成稳定的共晶化合物。因此,sn/au叠层中sn的厚度和au的厚度不能太厚也不能太薄,优选的,sn/au叠层中,sn的厚度为a1,au的厚度为b1,其中,a1:b1=(15~30):(70~85)。更优的,a1:b1=(18~25):(75~82)。

55.优选的,sn/au叠层中sn的厚度为0.2~0.4μm,au的厚度为1~1.5μm。

56.其中,表层的总厚度对降低表层和封装基板之间的封装空洞率也起着重要的作用;若表层的厚度太薄,则起不到降低封装空洞率的作用;若表层的厚度太厚,则增加制备难度和生产成本。

57.优选的,所述表层包括3~10层sn/au叠层。更优的,所述表层包括3~5层sn/au叠层。

58.所述反射层25为金属反射层,其将外延层发出的光反射到衬底10一侧,以提高倒装led芯片的出光效率。

59.优选的,所述反射层25包括ag层和ag层保护层,其中,ag层保护层覆盖在ag层上,以防ag在保护层26沉积时发生氧化、以及防止保护层26刻蚀时ag被刻蚀。

60.优选的,所述ag层保护层的材料选自ti、w、al、ni、pt中的一种金属。

61.参见图6,作为本实用新型的优选方案2,本实用新型提供的一种易于焊接的倒装led芯片,包括衬底10、设于衬底10上的发光结构20、设于发光结构20上第一电极30、设于发光结构20和第一电极30上的钝化层40、以及设于钝化层40上第二电极50,所述钝化层40设有至少两个电极孔洞,所述电极孔洞刻蚀至第一电极30的表面,所述第二电极50填充在所述电极孔洞内并与第一电极30形成导电连接,所述第二电极50设有至少两个填充孔洞,所述填充孔洞对应设置在电极孔洞的上方,所述填充孔洞内填充有导电物质60,所述导电物质60与第二电极50的表面齐平,所述导电物质60的硬度≥80hbs。

62.具体的,钝化层40是倒装led芯片的必要结构,其用于保护发光结构20,避免水汽、灰尘等进入发光结构20,同时避免芯片短路。为了保证第一电极30能够与第二电极50形成导电连接,必须对钝化层40进行刻蚀,以形成电极孔洞。由于倒装led芯片直接将第二电极50的金属沉积在钝化层40的电极孔洞内,以使第一电极30能够与第二电极50形成导电连接。但在封装焊接时,倒装led芯片上会施加一个下压力,由于钝化层40与第一电极30和第二电极50的金属硬度不同,因此第二电极50与封装基板上会产生大量的空洞,影响封装良率。

63.本实用新型的钝化层40由致密性好的绝缘层材料制成。优选的,所述钝化层40的材料选自sio2、tio5、sinx、sion中的一种。更优的,所述钝化层40为dbr层。

64.本实用新型在第二电极50上形成与电极孔洞位置对应的填充孔洞,并将导电物质60填充在填充孔洞内,不仅要将第二电极50填平,还要将第二电极50和封装基板形成导电连接,更重要的是本实用新型的导电物质60可以支撑第二电极50,避免第二电极50在挤压与封装基板产生缝隙,进而减少封装焊接时第二电极50与封装基板之间的空洞率,提高芯片的焊接性能。

65.本实用新型的导电物质60要具有以下特性:(1)与第二电极50形成良好的粘接;(2)有良好的导电性能,将导电基板和第二电极50形成上下导通;(3)与周围的结构具有相当的硬度,在芯片封装焊接时,只有导电物质60的硬度≥80hbs,导电物质60才不因为挤压而与第二电极50和封装基板产生缝隙,不会形成新的空洞。

66.为了满足导电物质60的上述特性,本实用新型的导镍电物质选自镍镍、铬、钛、钨中的一种。

67.优选的,所述填充孔洞的形状为梯形,即所述填充孔洞的侧壁与第二电极50的表面具有预设的夹角θ2。其中,所述夹角θ2对于导电物质60的效果起着重要的作用;若夹角θ2太大,则导电物质60与第二电极50、封装基板之间容易会产生裂缝;若夹角θ2太小,则填充孔洞的开口很宽,即填充孔洞的面积过大,不仅影响芯片的电压,还会增加芯片的空洞率,降低芯片的焊接性。

68.优选的,所述夹角θ2为35~65

°

。更优的,所述夹角θ2为40~55

°

。

69.参见图2,本实用新型的发光结构20包括依次设置的外延层、透明导电层24、反射层25和保护层26,所述外延层包括依次设置的第一半导体层21、有源层22和第二半导体层23,其中,所述发光结构20还包括第一凹孔27和第二凹孔28,所述第一凹孔27从保护层26刻

蚀至第一半导体层21,所述第二凹孔28从保护层26刻蚀至反射层25的表面。

70.参见图3,所述第一电极30包括n型第一电极31和p型第一电极32,所述n型第一电极31设置在保护层26和第一凹孔27的第一半导体层21上,所述p型第一电极32设置在第二凹孔28的反射层25上。所述保护层26用于隔开n型第一电极31和p型第一电极32,以防止芯片短路。优选的,所述保护层26由致密性好的绝缘层材料制成。优选的,所述保护层26的材料选自sio2、tio5、sinx、sion中的一种。

71.其中,位于第一凹孔27内的那部分n型第一电极31,其水平面高度略低于保护层26,形成第三凹孔33;本实用新型保护层26覆盖在第三凹孔33以外的发光结构20上的面积要尽可能大,这样可以降低凹孔的比例,降低空洞率,提高可焊性。

72.参见图4,所述钝化层40设置在第一电极30上,并将第三凹孔33和第二凹孔28填平;其中,钝化层40的电极孔洞对应设置在第三凹孔33和第二凹孔28的上方,这样填充在电极孔洞内的第二电极50才能与第一电极30形成导电连接。

73.具体的,所述电极孔洞包括第一电极孔洞41和第二电极孔洞42,所述第一电极孔洞41对应设于第三凹孔33的上方,所述第二电极孔洞42至少包括n型第二电极孔洞42和p型第二电极孔洞43,所述n型第二电极孔洞42刻蚀至n型第一电极31的表面,所述p型第二电极孔洞43刻蚀至p型第一电极32的表面。

74.其中,所述第二电极50包括n型第二电极51和p型第二电极52,所述n型第二电极51设置在钝化层40上并填充到第一电极孔洞41和n型第二电极孔洞42内,并与n型第一电极31形成导电连接;所述p型第二电极52设置在钝化层40上并填充到p型第二电极孔洞43内,并与p型第一电极32形成导电连接。

75.参见图7,所述填充孔洞包括第一填充孔洞53和第二填充孔洞,所述第一填充孔洞53对应设于第一电极孔洞41的上方,所述第二填充孔洞54对应设于第二电极孔洞的上方。具体的,所述第二填充通孔包括n型第二填充通孔54和p型第二填充通孔55,所述n型第二电极51设有所述第一填充孔洞53和n型第二填充孔洞54,所述p型第二电极52设有所述p型第二填充孔洞55;填充在第一填充孔洞53和第二填充孔洞内的填充物质可以抵消钝化层40上第一电极孔洞41和第二电极孔洞42内第二电极50硬度不够、支撑力不足的影响,减少封装焊接时第二电极50与封装基板之间的空洞率,提高芯片的焊接性能。

76.导电物质60的厚度取决于填充孔洞的深度,而填充孔洞的深度取决于第二电极50的厚度,若导电物质60的厚度太薄,导电物质60的导电性会受到影响,从而影响芯片的电压,且导电物质60的填充效果下降,空洞率增加,焊接性降低;若电物质的厚度太厚,则第二电极50的厚度也要相应增加,从而成本增加,且导电物质60与第二电极50容易出现裂缝,空洞率反而增加,焊接性也下降。优选的,导电物质60的厚度为0.6~1.2μm。更优的,导电物质60的厚度为0.7~1.0μm。

77.本实用新型的第二电极50用于焊接封装,因此其面积受封装基板和封装工艺的影响,为了提高焊接效率和焊接效果,n型第二电极51和p型第二电极52的面积相等,且高度在同一水平面上。本实用新型的第一电极30用于芯片的电流扩展,起到降电压和提亮度的作用。优选的,第一电极30的材料选自cr、ni、al、ti、pt、au中的一种;第二电极50的材料选自cr、ni、al、ti、pt、au、sn中的一种。

78.由于第一电极30的底层需要与保护层26、外延层具有良好的粘接作用,因此第一

电极30的底层选用cr或ti;而第一电极30的顶层需要在钝化层40刻蚀时具有保护下方金属的作用,且第一电极30的顶层需要与第二电极50、钝化层40具有良好的粘接作用,因此第一电极30的顶层选用pt、au、ti。优选的,所述第一电极30为cr/al/ti/pt/au/ti叠层结构,具有一定的反射率,可将外延层发出的光反射到衬底10一侧。

79.参见图5,所述第二电极50为叠层结构,包括导电层51和表层52,所述导电层51的材料选自cr、ni、al、ti、pt中的一种,所述表层52为叠层结构,包括多层sn/au叠层。

80.所述表层将纯金与纯锡复合形成sn/au叠层,通过不同比例的au、sn复合来消除表层的应力,提升表层金属和封装基板之间的润湿性能,从而降低表层和封装基板之间的封装空洞率。

81.具体的,当封装基板被加热至适合的共晶温度时,金或银元素会渗透到表层,以改变表层的组分,从而提高表层的熔点,令表层固化并将倒装led芯片紧固的焊接在封装基板上。本实用新型au

‑

sn共晶焊的优点包括:(1)降低热阻,锡(sn)和金(au)材料都是金属材料,导热好;(2)提供光效,led发光效率和热阻成反比;(3)提高效率,led共晶一次固晶成型;(4)粘结强度大于银胶固晶,大幅减少掉晶现象。

82.其中,sn/au叠层中sn的厚度和au的厚度决定了sn/au叠层中sn和au的比例,由于本实用新型的表层通过不同比例的ausn复合来消除表层的应力,提升表层金属和封装基板之间的润湿性能,从而降低表层和封装基板之间的封装空洞率,其中,au和sn的质量百分比在(15%~30%):(70%~85%)范围内,au和sn才能形成稳定的共晶化合物。因此,sn/au叠层中sn的厚度和au的厚度不能太厚也不能太薄,优选的,sn/au叠层中,sn的厚度为a1,au的厚度为b1,其中,a1:b1=(15~30):(70~85)。更优的,a1:b1=(18~25):(75~82)。

83.优选的,sn/au叠层中sn的厚度为0.2~0.4μm,au的厚度为1~1.5μm。

84.其中,表层的总厚度对降低表层和封装基板之间的封装空洞率也起着重要的作用;若表层的厚度太薄,则起不到降低封装空洞率的作用;若表层的厚度太厚,则增加制备难度和生产成本。

85.优选的,所述表层包括3~10层sn/au叠层。更优的,所述表层包括3~5层sn/au叠层。

86.所述反射层25为金属反射层25,其将外延层发出的光反射到衬底10一侧,以提高倒装led芯片的出光效率。

87.优选的,所述反射层25包括ag层和ag层保护层,其中,ag层保护层覆盖在ag层上,以防ag在保护层26沉积时发生氧化、以及防止保护层26刻蚀时ag被刻蚀。

88.优选的,所述ag层保护层的材料选自ti、w、al、ni、pt中的一种金属。

89.参见图8,作为本实用新型的优选方案3,本实用新型提供的一种易于焊接的倒装led芯片,包括衬底10、设于衬底10上的发光结构20、设于发光结构20上第一电极30、设于发光结构20和第一电极30上的钝化层40、以及设于钝化层40上第二电极50,所述钝化层40设有至少一个电极孔洞,所述第二电极50设有至少一个填充孔洞,所述填充孔洞对应设置在电极孔洞的上方,所述电极孔洞和填充孔洞内均填充有导电物质60,填充在电极孔洞内的导电物质60与钝化层40的表面齐平,并将第一电极30和第二电极50形成导电连接,填充在填充孔洞内的导电物质60与第二电极50的表面齐平,其中,所述导电物质60的硬度≥80hbs。

90.具体的,钝化层40是倒装led芯片的必要结构,其用于保护发光结构20,避免水汽、灰尘等进入发光结构20,同时避免芯片短路。为了保证第一电极30能够与第二电极50形成导电连接,必须对钝化层40进行刻蚀,以形成电极孔洞。由于倒装led芯片直接将第二电极50的金属沉积在钝化层40的电极孔洞内,以使第一电极30能够与第二电极50形成导电连接。但在封装焊接时,倒装led芯片上会施加一个下压力,由于钝化层40与第一电极30和第二电极50的金属硬度不同,因此第二电极50与封装基板上会产生大量的空洞,影响封装良率。

91.本实用新型的钝化层40由致密性好的绝缘层材料制成。优选的,所述钝化层40的材料选自sio2、tio5、sinx、sion中的一种。更优的,所述钝化层40为dbr层。

92.本实用新型将导电物质60填充在钝化层40的电极孔洞内,不仅要将钝化层40填平,还要将第一电极30和第二电极50形成导电连接,更重要的是本实用新型的导电物质60可以支撑第一电极30和第二电极50,减少封装焊接时第二电极50与封装基板之间的空洞率,提高芯片的焊接性能。

93.进一步地,本实用新型在第二电极50上形成与电极孔洞位置对应的填充孔洞,并将导电物质60填充在填充孔洞内,不仅要将第二电极50填平,还要将第二电极50和封装基板形成导电连接,更重要的是本实用新型的导电物质60可以支撑第二电极50,避免第二电极50在挤压与封装基板产生缝隙,进而减少封装焊接时第二电极50与封装基板之间的空洞率,提高芯片的焊接性能。

94.本实用新型的导电物质60要具有以下特性:(1)与第二电极50形成良好的粘接;(2)有良好的导电性能,将导电基板和第二电极50形成上下导通;(3)与周围的结构具有相当的硬度,在芯片封装焊接时,只有导电物质60的硬度≥80hbs,导电物质60才不因为挤压而与第二电极50和封装基板产生缝隙,不会形成新的空洞。

95.为了满足导电物质60的上述特性,本实用新型的导镍电物质选自镍镍、铬、钛、钨中的一种。

96.优选的,所述电极孔洞的形状为梯形,即所述电极孔洞的侧壁与钝化层40的表面具有预设的夹角θ1。其中,所述夹角θ1对于导电物质60的效果起着重要的作用;若夹角θ1太大,则导电物质60与钝化层40之间容易会产生裂缝,设置在导电物质60上的第二电极50容易与导电物质60断开;若夹角θ1太小,则电极孔洞的开口很宽,即电极孔洞的面积过大,这样会增加芯片的空洞率,降低芯片的焊接性。

97.优选的,所述夹角θ1为35~65

°

。更优的,所述夹角θ1为40~55

°

。

98.优选的,所述填充孔洞的形状为梯形,即所述填充孔洞的侧壁与第二电极50的表面具有预设的夹角θ2。其中,所述夹角θ2对于导电物质60的效果起着重要的作用;若夹角θ2太大,则导电物质60与第二电极50、封装基板之间容易会产生裂缝;若夹角θ2太小,则填充孔洞的开口很宽,即填充孔洞的面积过大,不仅影响芯片的电压,还会增加芯片的空洞率,降低芯片的焊接性。

99.优选的,所述夹角θ2为35~65

°

。更优的,所述夹角θ2为40~55

°

。

100.参见图2,本实用新型的发光结构20包括依次设置的外延层、透明导电层24、反射层25和保护层26,所述外延层包括依次设置的第一半导体层21、有源层22和第二半导体层23,其中,所述发光结构20还包括第一凹孔27和第二凹孔28,所述第一凹孔27从保护层26刻

蚀至第一半导体层21,所述第二凹孔28从保护层26刻蚀至反射层25的表面。

101.参见图3,所述第一电极30包括n型第一电极31和p型第一电极32,所述n型第一电极31设置在保护层26和第一凹孔27的第一半导体层21上,所述p型第一电极32设置在第二凹孔28的反射层25上。所述保护层26用于隔开n型第一电极31和p型第一电极32,以防止芯片短路。优选的,所述保护层26由致密性好的绝缘层材料制成。优选的,所述保护层26的材料选自sio2、tio5、sinx、sion中的一种。

102.参见图4,位于第一凹孔27内的那部分n型第一电极31,其水平面高度略低于保护层26,形成第三凹孔33;本实用新型保护层26覆盖在第三凹孔33以外的发光结构20上的面积要尽可能大,这样可以降低凹孔的比例,降低空洞率,提高可焊性。

103.所述钝化层40设置在第一电极30上,并将第三凹孔33和第二凹孔28填平;其中,钝化层40的电极孔洞对应设置在第三凹孔33和第二凹孔28的上方,这样填充在电极孔洞内的导电物质60才起到良好的支撑作用,减少封装焊接时第二电极50与封装基板之间的空洞率,提高芯片的焊接性能。

104.其中,所述电极孔洞包括第一电极孔洞41和第二电极孔洞42,所述第一电极孔洞41对应设于第三凹孔33的上方,所述第二电极孔洞42至少包括n型第二电极孔洞42和p型第二电极孔洞43,所述n型第二电极孔洞42刻蚀至n型第一电极31的表面,所述p型第二电极孔洞43刻蚀至p型第一电极32的表面。具体的,填充在n型第二电极孔洞42内的导电物质60与n型第一电极31导电连接,填充在p型第二电极孔洞43内的导电物质60与p型第一电极32导电连接,而填充在第一电极孔洞41内的导电物质60可以与n型第一电极31导电连接,也可以不与n型第一电极31导电连接,其主要取决于第一电极孔洞41的深度。为了减少空洞率,第一电极孔洞41和第二电极孔洞42的深度相同,因此填充在第一电极孔洞41内的导电物质60一般不与n型第一电极31形成导电连接。

105.具体的,所述第二电极50包括n型第二电极51和p型第二电极52,所述n型第二电极51设置在第一电极孔洞41和n型第二电极孔洞42上,所述p型第二电极52设置在p型第二电极孔洞43上,其中,填充在n型第二电极孔洞42内的导电物质60将n型第二电极51和n型第一电极31形成导电连接,填充在p型第二孔洞内的导电物质60将p型第二电极52导和p型第一电极32形成导电连接。

106.参见图9,所述填充孔洞包括第一填充孔洞53和第二填充孔洞,所述第一填充孔洞53对应设于第一电极孔洞41的上方,所述第二填充孔洞对应设于第二电极孔洞42的上方。具体的,所述第二填充通孔包括n型第二填充通孔54和p型第二填充通孔55,所述n型第二电极51设有所述第一填充孔洞53和n型第二填充孔洞54,所述p型第二电极52设有所述p型第二填充孔洞55;填充在第一填充孔洞53和第二填充孔洞内的填充物质可以抵消钝化层40上第一电极孔洞41和第二电极孔洞42内第二电极50硬度不够、支撑力不足的影响,减少封装焊接时第二电极50与封装基板之间的空洞率,提高芯片的焊接性能。

107.填充在电极孔洞的导电物质60的厚度取决于电极孔洞的深度,电极孔洞的深度取决于钝化层40的厚度,若钝化层40的厚度太薄,即导电物质60的厚度太薄,则芯片容易漏电,导电物质60的导电性会受到影响,从而影响芯片的电压,且导电物质60的填充效果下降,空洞率增加,焊接性降低;若钝化层40的厚度太厚,即导电物质60的厚度太厚,则成本增加,且导电物质60与钝化层40容易出现裂缝,空洞率反而增加,焊接性也下降。优选的,导电

物质60的厚度为0.6~1.2μm。更优的,导电物质60的厚度为0.7~1.0μm。

108.同样的,填充在填充孔洞的导电物质60的厚度取决于填充孔洞的深度,而填充孔洞的深度取决于第二电极50的厚度,若导电物质60的厚度太薄,导电物质60的导电性会受到影响,从而影响芯片的电压,且导电物质60的填充效果下降,空洞率增加,焊接性降低;若电物质的厚度太厚,则第二电极50的厚度也要相应增加,从而成本增加,且导电物质60与第二电极50容易出现裂缝,空洞率反而增加,焊接性也下降。优选的,导电物质60的厚度为0.6~1.2μm。更优的,导电物质60的厚度为0.7~1.0μm。

109.本实用新型的第二电极50用于焊接封装,因此其面积受封装基板和封装工艺的影响,为了提高焊接效率和焊接效果,n型第二电极51和p型第二电极52的面积相等,且高度在同一水平面上。本实用新型的第一电极30用于芯片的电流扩展,起到降电压和提亮度的作用。优选的,第一电极30的材料选自cr、ni、al、ti、pt、au中的一种;第二电极50的材料选自cr、ni、al、ti、pt、au、sn中的一种。

110.由于第一电极30的底层需要与保护层26、外延层具有良好的粘接作用,因此第一电极30的底层选用cr或ti;而第一电极30的顶层需要在钝化层40刻蚀时具有保护下方金属的作用,且第一电极30的顶层需要与第二电极50、钝化层40具有良好的粘接作用,因此第一电极30的顶层选用pt、au、ti。优选的,所述第一电极30为cr/al/ti/pt/au/ti叠层结构,具有一定的反射率,可将外延层发出的光反射到衬底10一侧。

111.参见图5,所述第二电极50为叠层结构,包括导电层51和表层52,所述导电层51的材料选自cr、ni、al、ti、pt中的一种,所述表层52为叠层结构,包括多层sn/au叠层。

112.所述表层将纯金与纯锡复合形成sn/au叠层,通过不同比例的au、sn复合来消除表层的应力,提升表层金属和封装基板之间的润湿性能,从而降低表层和封装基板之间的封装空洞率。

113.具体的,当封装基板被加热至适合的共晶温度时,金或银元素会渗透到表层,以改变表层的组分,从而提高表层的熔点,令表层固化并将倒装led芯片紧固的焊接在封装基板上。本实用新型au

‑

sn共晶焊的优点包括:(1)降低热阻,锡(sn)和金(au)材料都是金属材料,导热好;(2)提供光效,led发光效率和热阻成反比;(3)提高效率,led共晶一次固晶成型;(4)粘结强度大于银胶固晶,大幅减少掉晶现象。

114.其中,sn/au叠层中sn的厚度和au的厚度决定了sn/au叠层中sn和au的比例,由于本实用新型的表层通过不同比例的ausn复合来消除表层的应力,提升表层金属和封装基板之间的润湿性能,从而降低表层和封装基板之间的封装空洞率,其中,au和sn的质量百分比在(15%~30%):(70%~85%)范围内,au和sn才能形成稳定的共晶化合物。因此,sn/au叠层中sn的厚度和au的厚度不能太厚也不能太薄,优选的,sn/au叠层中,sn的厚度为a1,au的厚度为b1,其中,a1:b1=(15~30):(70~85)。更优的,a1:b1=(18~25):(75~82)。

115.优选的,sn/au叠层中sn的厚度为0.2~0.4μm,au的厚度为1~1.5μm。

116.其中,表层的总厚度对降低表层和封装基板之间的封装空洞率也起着重要的作用;若表层的厚度太薄,则起不到降低封装空洞率的作用;若表层的厚度太厚,则增加制备难度和生产成本。

117.优选的,所述表层包括3~10层sn/au叠层。更优的,所述表层包括3~5层sn/au叠层。

118.所述反射层25为金属反射层25,其将外延层发出的光反射到衬底10一侧,以提高倒装led芯片的出光效率。

119.优选的,所述反射层25包括ag层和ag层保护层,其中,ag层保护层覆盖在ag层上,以防ag在保护层26沉积时发生氧化、以及防止保护层26刻蚀时ag被刻蚀。

120.优选的,所述ag层保护层的材料选自ti、w、al、ni、pt中的一种金属。

121.以上所揭露的仅为本实用新型一种较佳实施例而已,当然不能以此来限定本实用新型之权利范围,因此依本实用新型权利要求所作的等同变化,仍属本实用新型所涵盖的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1