沟槽型MOS器件的制作方法

沟槽型mos器件

技术领域

1.本实用新型涉及一种mos器件,尤其涉及一种沟槽型mos器件。

背景技术:

2.沟槽功率mos器件是在平面式功率mos器件的基础上发展起来的。与平面式功率mos器件相比,其具有导通电阻低、饱和压降低、开关速度快、沟道密度高、芯片尺寸小等优点;采用沟槽式结构,消除了平面式功率mos器件存在的寄生jfet(结型场效应管)效应。目前深沟槽功率mos器件已经发展成为中低压大功率mos器件的主流。但是,现有沟槽大功率mos器件仍然存在诸多待改善的技术问题。

技术实现要素:

3.本实用新型提供一种沟槽型mos器件,此沟槽型mos器件既降低了器件的切换损耗,也改善了在高频下器件开关切换的耐冲击能力。

4.为达到上述目的,本实用新型采用的技术方案是:一种沟槽型mos器件,包括n型外延层、位于n型外延层中上部的轻掺杂p型阱层,此轻掺杂p型阱层中间隔地开有第一沟槽和第二沟槽,位于轻掺杂p型阱层中的第一沟槽和第二沟槽从轻掺杂p型阱层上表面延伸至n型外延层内,所述第一沟槽和第二沟槽内均具有一闸极多晶硅部,所述第一沟槽、第二沟槽分别与各自的闸极多晶硅部之间均通过一闸极氧化层隔离;

5.所述轻掺杂p型阱层位于第一沟槽、第二沟槽之间区域的上部间隔地设置有第一重掺杂n型源极区、第二重掺杂n型源极区,此第一重掺杂n型源极区、第二重掺杂n型源极区分别位于第一沟槽、第二沟槽的周边;

6.所述轻掺杂p型阱层位于第一重掺杂n型源极区、第二重掺杂n型源极区之间的区域设置有一重掺杂p型区,所述重掺杂p型区上表面位于轻掺杂p型阱层上表面,且重掺杂p型区下表面延伸至所述n型外延层内部,此重掺杂p型区的下端位于轻掺杂p型阱层下表面的下方,所述重掺杂p型区在横向上延伸至第一重掺杂n型源极区、第二重掺杂n型源极区相向端的正下方,所述重掺杂p型区的中部与第一沟槽和第二沟槽之间均为沟道区,所述重掺杂p型区中部的宽度大于其上部和下部的宽度;所述重掺杂p型区与轻掺杂p型阱层的接触面为外凸弧形面,所述重掺杂p型区与n型外延层的接触面为向下凸起的弧形面;

7.所述第一沟槽、第二沟槽上方和第一重掺杂n型源极区、第二重掺杂n型源极区靠近沟槽的区域上方覆盖有一介电质层,所述重掺杂p型区上方和第一重掺杂n型源极区、第二重掺杂n型源极区远离沟槽的区域上方覆盖有一金属层。

8.上述技术方案中的有关内容解释如下:

9.1、上述方案中,所述轻掺杂p型阱层与重掺杂p型区的深度比为10:3~5。

10.2、上述方案中,所述第一重掺杂n型源极区、第二重掺杂n型源极区均为高浓度砷掺杂n型源极区。

11.3、上述方案中,所述金属层为铝金属层。

12.由于上述技术方案运用,本实用新型与现有技术相比具有下列优点:

13.1、本实用新型沟槽型mos器件,其轻掺杂p型阱层位于第一重掺杂n型源极区、第二重掺杂n型源极区之间的区域设置有一重掺杂p型区,所述重掺杂p型区上表面位于轻掺杂p型阱层上表面,且重掺杂p型区下表面延伸至所述n型外延层内部,此重掺杂p型区的下端位于轻掺杂p型阱层下表面的下方,所述重掺杂p型区与轻掺杂p型阱层的接触面为外凸弧形面,所述重掺杂p型区中部的宽度大于其上部和下部的宽度,所述重掺杂p型区与n型外延层的接触面为向下凸起的弧形面,将最大电场转移至位于重掺杂p型区下方的n型外延层内,从而降低了器件的切换损耗。

14.2、本实用新型沟槽型mos器件,其轻掺杂p型阱层位于第一重掺杂n型源极区、第二重掺杂n型源极区之间的区域设置有一重掺杂p型区,所述重掺杂p型区在横向上延伸至第一重掺杂n型源极区、第二重掺杂n型源极区相向端的正下方,所述重掺杂p型区的下部与第一沟槽和第二沟槽之间均为沟道区,改善了在高频下器件开关切换的耐冲击能力,从而延长了器件的使用寿命。

附图说明

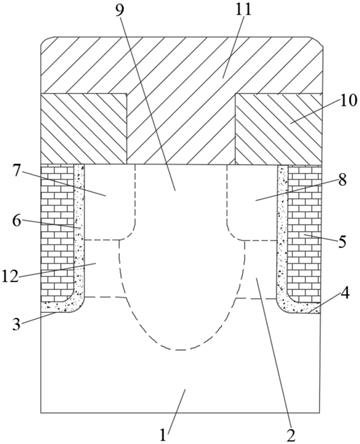

15.附图1为本实用新型沟槽型mos器件的结构示意图。

16.以上附图中:1、n型外延层;2、轻掺杂p型阱层;3、第一沟槽;4、第二沟槽;5、闸极多晶硅部;6、闸极氧化层隔离;7、第一重掺杂n型源极区;8、第二重掺杂n型源极区;9、重掺杂p型区;10、介电质层;11、金属层;12、金属层。

具体实施方式

17.下面结合实施例对本实用新型作进一步描述:

18.实施例1:一种沟槽型mos器件,包括n型外延层1、位于n型外延层1中上部的轻掺杂p型阱层2,此轻掺杂p型阱层2中间隔地开有第一沟槽3和第二沟槽4,位于轻掺杂p型阱层2中的第一沟槽3和第二沟槽4从轻掺杂p型阱层2上表面延伸至n型外延层1内,所述第一沟槽3和第二沟槽4内均具有一闸极多晶硅部5,所述第一沟槽3、第二沟槽4分别与各自的闸极多晶硅部5之间均通过一闸极氧化层隔离6;

19.所述轻掺杂p型阱层2位于第一沟槽3、第二沟槽4之间区域的上部间隔地设置有第一重掺杂n型源极区7、第二重掺杂n型源极区8,此第一重掺杂n型源极区7、第二重掺杂n型源极区8分别位于第一沟槽3、第二沟槽4的周边;

20.所述轻掺杂p型阱层2位于第一重掺杂n型源极区7、第二重掺杂n型源极区8之间的区域设置有一重掺杂p型区9,所述重掺杂p型区9上表面位于轻掺杂p型阱层2上表面,且重掺杂p型区9下表面延伸至所述n型外延层1内部,此重掺杂p型区9的下端位于轻掺杂p型阱层2下表面的下方,所述重掺杂p型区9在横向上延伸至第一重掺杂n型源极区7、第二重掺杂n型源极区8相向端的正下方,所述重掺杂p型区9的中部与第一沟槽3和第二沟槽4之间均为沟道区12,所述重掺杂p型区9中部的宽度大于其上部和下部的宽度;所述重掺杂p型区9与轻掺杂p型阱层2的接触面为外凸弧形面,所述重掺杂p型区9与n型外延层1的接触面为向下凸起的弧形面;

21.所述第一沟槽3、第二沟槽4上方和第一重掺杂n型源极区7、第二重掺杂n型源极区

8靠近沟槽的区域上方覆盖有一介电质层10,所述重掺杂p型区9上方和第一重掺杂n型源极区7、第二重掺杂n型源极区8远离沟槽的区域上方覆盖有一金属层11。

22.上述轻掺杂p型阱层2与重掺杂p型区9的深度比为10:3.2。

23.上述金属层11为铝金属层。

24.实施例2:一种沟槽型mos器件,包括n型外延层1、位于n型外延层1中上部的轻掺杂p型阱层2,此轻掺杂p型阱层2中间隔地开有第一沟槽3和第二沟槽4,位于轻掺杂p型阱层2中的第一沟槽3和第二沟槽4从轻掺杂p型阱层2上表面延伸至n型外延层1内,所述第一沟槽3和第二沟槽4内均具有一闸极多晶硅部5,所述第一沟槽3、第二沟槽4分别与各自的闸极多晶硅部5之间均通过一闸极氧化层隔离6;

25.所述轻掺杂p型阱层2位于第一沟槽3、第二沟槽4之间区域的上部间隔地设置有第一重掺杂n型源极区7、第二重掺杂n型源极区8,此第一重掺杂n型源极区7、第二重掺杂n型源极区8分别位于第一沟槽3、第二沟槽4的周边;

26.所述轻掺杂p型阱层2位于第一重掺杂n型源极区7、第二重掺杂n型源极区8之间的区域设置有一重掺杂p型区9,所述重掺杂p型区9上表面位于轻掺杂p型阱层2上表面,且重掺杂p型区9下表面延伸至所述n型外延层1内部,此重掺杂p型区9的下端位于轻掺杂p型阱层2下表面的下方,所述重掺杂p型区9在横向上延伸至第一重掺杂n型源极区7、第二重掺杂n型源极区8相向端的正下方,所述重掺杂p型区9的中部与第一沟槽3和第二沟槽4之间均为沟道区12,所述重掺杂p型区9中部的宽度大于其上部和下部的宽度;所述重掺杂p型区9与轻掺杂p型阱层2的接触面为外凸弧形面,所述重掺杂p型区9与n型外延层1的接触面为向下凸起的弧形面;

27.所述第一沟槽3、第二沟槽4上方和第一重掺杂n型源极区7、第二重掺杂n型源极区8靠近沟槽的区域上方覆盖有一介电质层10,所述重掺杂p型区9上方和第一重掺杂n型源极区7、第二重掺杂n型源极区8远离沟槽的区域上方覆盖有一金属层11。

28.上述轻掺杂p型阱层2与重掺杂p型区9的深度比为10:4.5。

29.上述第一重掺杂n型源极区7、第二重掺杂n型源极区8均为高浓度砷掺杂n型源极区。

30.采用上述沟槽型mos器件时,其轻掺杂p型阱层位于第一重掺杂n型源极区、第二重掺杂n型源极区之间的区域设置有一重掺杂p型区,所述重掺杂p型区上表面位于轻掺杂p型阱层上表面,且重掺杂p型区下表面延伸至所述n型外延层内部,此重掺杂p型区的下端位于轻掺杂p型阱层下表面的下方,所述重掺杂p型区与轻掺杂p型阱层的接触面为外凸弧形面,所述重掺杂p型区中部的宽度大于其上部和下部的宽度,所述重掺杂p型区与n型外延层的接触面为向下凸起的弧形面,将最大电场转移至位于重掺杂p型区下方的n型外延层内,从而降低了器件的切换损耗;还有,其改善了在高频下器件开关切换的耐冲击能力,从而延长了器件的使用寿命。

31.上述实施例只为说明本实用新型的技术构思及特点,其目的在于让熟悉此项技术的人士能够了解本实用新型的内容并据以实施,并不能以此限制本实用新型的保护范围。凡根据本实用新型精神实质所作的等效变化或修饰,都应涵盖在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1