一种芯片的表层结构和芯片的制作方法

1.本实用新型涉及半导体芯片领域,特别是一种芯片的表层结构和芯片。

背景技术:

2.砷化镓芯片也即砷化镓集成电路(gallium arsenide integrated circuit,gaasic),是指用半导体砷化镓(gaas)器件构成的集成电路。砷化镓集成电路具有的优势主要包括:高频率、高速度、高功率、低噪声和低功耗。其在国民经济建设和国防建设中有着许多重要用途,而且是硅集成电路所替代不了的。其主要应用领域是:通信卫星、电视卫星接收、移动通信、高清晰度电视、微波毫米波数字频率源、光通信、超高速率讯号处理、微型超级计算机、恶劣环境下用计算机和控制机、高性能仪器、微波传感以及许多重要的国防军用电子装备等。

3.参见图9,现有的砷化镓芯片1,其表层通常具有金属互联结构2和钝化层3,该金属互联结构2设有外凸的焊盘,该钝化层3覆盖于砷化镓芯片1的表层,并在金属互联结构2的焊盘处设置开孔3。这种结构下,由于金属互联结构或者底层的高低起伏影响,砷化镓芯片的表层起伏较大,起伏位置处受到较大的应力,则后续工艺或者封装测试时存在一定的损坏风险,例如裂开,水汽进入等,造成可靠性问题,导致产品无法使用。

技术实现要素:

4.本实用新型的主要目的在于克服现有的芯片表层起伏较大,影响后续工艺或封装测试的缺陷,提出一种芯片的表层结构和芯片,使得芯片表层更平坦,减小应力,提高产品可靠性。

5.本实用新型采用如下技术方案:

6.一种芯片的表层结构,包括设置于芯片表面的金属互联结构,该金属互联结构表面设有焊盘,其特征在于:还包括至少一平坦介质层,该平坦介质层覆盖于金属互联结构外露表面且在焊盘处设有开孔,该平坦介质层开孔处侧壁与该焊盘之间形成有锐角。

7.所述锐角为所述平坦介质层开孔的侧壁与对应的所述焊盘中与该侧壁相交且被所述平坦介质层覆盖的端面的夹角,锐角的角度范围为40

°‑

75

°

。

8.所述金属互联结构包括若干金属互联层和若干介质层,该若干金属互联层由下至上依次电性连接且底层的金属互联层与所述芯片的电极电性连接,该若干介质层分别设置于相邻的两金属互联层之间;所述平坦介质层覆盖于最上层的金属互联层的表面和介质层外露的表面,并在最上层金属互联层的焊盘处设有所述开孔。

9.所述平坦介质层的厚度范围是5-10um。所述平坦介质层为非感光型的有机材料或感光型的有机材料。所述非感光型的有机材料为聚酰亚胺;所述感光型的有机材料为聚苯并恶唑或bcb。

10.本实用新型还包括有钝化层,该钝化层覆盖于所述平坦介质层表面以及所述开孔与所述焊盘的交界处。所述开孔处侧壁的钝化层与所述焊盘中与该侧壁相交且被钝化层覆

盖的端面的夹角为锐角,锐角的角度范围为40

°‑

75

°

。

11.一种芯片,包括芯片,其特征在于:该芯片上述的一种芯片的表层结构。

12.由上述对本实用新型的描述可知,与现有技术相比,本实用新型具有如下有益效果:

13.1、本实用新型中,在芯片表层覆盖平坦介质层,从而减缓芯片表面的高低起伏,进一步减小应力,该平坦介质层在焊盘处设有开孔,开孔处侧壁与该焊盘之间形成有锐角,避免应力差异大导致的开裂,提高芯片可靠性。

14.2、本实用新型中,平坦介质层与金属互联结构的锐角为平坦介质层开孔的侧壁与焊盘中与该侧壁相交且被平坦介质层覆盖的端面的夹角,能避免裂开,水汽进入等,确保芯片正常使用。

15.3、本实用新型中,平坦介质层为一层或两层或多层有机材料,能大大减少芯片表层高低起伏状况,增大了后续工艺和封装测试的工艺窗口,平坦介质层可以是感光型的有机材料或非感光型的有机材料,优选为pbo,利用光刻显影制作开孔,制作工艺简单。

16.4、本实用新型中,还设置有钝化层覆盖于平坦介质层表面以及开孔与焊盘交界处,保护其所覆盖的化合物半导体器件,防止水汽入侵化合物半导体器件,以及避免机械碰撞,确保化合物半导体器件的可靠度佳,钝化层与焊盘的夹角也为锐角,避免应力差异大导致的开裂,提高芯片可靠性。

附图说明

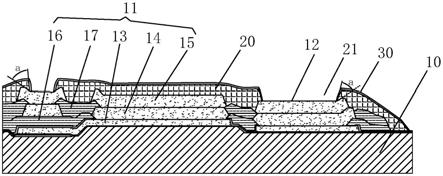

17.图1为本实用新型剖视图;

18.图2为芯片结构图;

19.图3为芯片表层覆盖平坦介质层示意图;

20.图4为平坦介质层表面覆盖遮蔽层并蚀刻示意图(实施例一);

21.图5为平坦介质层蚀刻开口示意图;

22.图6为去除遮蔽层示意图;

23.图7为感光材料的平坦介质层光刻区域示意图;

24.图8为平坦介质层光刻开孔示意图;

25.图9为现有芯片结构图;

26.其中:

27.10、芯片,11、金属互联结构,12、焊盘,13、第一金属互联层,14、第二金属互联层,15、第三金属互联层,16、第一介质层,17、第二介质层,20、平坦介质层,21、开孔,30、钝化层,40、遮蔽层。

具体实施方式

28.以下通过具体实施方式对本实用新型作进一步的描述。

29.本实用新型中出现的“第一”、“第二”等用语仅是为了方便描述,以区分具有相同名称的不同组成部件,并不表示先后或主次关系。

30.在本实用新型的描述中,需要说明的是,若采用了“上”、“下”、“左”、“右”、“前”、“后”、“表面”、“表层”、“侧壁”等指示的方位或位置关系为基于附图所示的方位或位置关

系,仅是为了便于描述本实用新型,而不是指示或暗示所指的装置必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型保护范围的限制。

31.实施例一

32.参见图1,一种芯片的表层结构,芯片10表层设有金属互联结构11,该金属互联结构11设有至少一焊盘12,还包括至少一平坦介质层20,该平坦介质层20覆盖于金属互联结构11外露表面,并在焊盘12处设有开孔21,该平坦介质层20的开孔21处侧壁与该焊盘12之间形成有锐角a。

33.进一步的,本实用新型中,平坦化前,参见图2为作业完表层金属材料后的晶圆,该晶圆的芯片具有金属互联结构,焊盘12为表层的金属互联结构11中的金属接触区域。具体的,该金属互联结构包括若干金属互联层和若干介质层,该若干金属互联层由下至上依次电性连接且底层的金属互联层与芯片10的电极电性连接,该若干介质层分别设置于相邻的两金属互联层之间。

34.本实用新型中,以三层金属互联层和两层介质层为例,由下至上包括有第一金属互联层13、第二金属互联层14,第三金属互联层15、第一介质层16和第二介质层17,第一金属互联层13与芯片的电极电性连接,第三金属互联层15设有焊盘。第一介质层16填充于第一金属互联层13和第二金属互联层14之间的非电性连接区域,第二介质层17填充于第二金属互联层14和第三金属互联层15之间非电性连接区域。该介质层可采用pbo、pi、bcb中的一种,优选的,第一介质层16可采用pi,厚度范围为1-3微米,最佳值1.6微米,第二介质层17可采用pi,厚度范围为1-4微米,最佳值2微米。

35.进一步的,平坦介质层20覆盖于最上层的金属互联层即第三金属互联层15的表面和介质层外露的表面(包括第一介质层16和第二介质层17外露的表面),并在最上层金属互联层的焊盘12处设有开孔21。

36.参见图3,可利用平坦化技术,在晶圆的芯片10表层涂布至少一层有机材料构,固化后构成平坦介质层20,固化温度约300℃左右,固化时间1h左右。该平坦介质层20完全覆盖芯片10表层,包括金属互联结构11外露表面和表层的其它结构,从而减缓芯片10表面的高低起伏,进一步减小应力。

37.本实施例中,该平坦介质层20可以是一层或两层或更多层有机材料,可根据需要设定,其厚度为5-10微米,最佳值7微米。平坦介质层20可为非感光型的有机材料,例如pi2610聚酰亚胺,但不限于此。

38.其中,对于非感光型有机材料的平坦介质层20,可采用光刻和显影来蚀刻平坦介质层20,使其在焊盘12处开孔21。参见图4,在平坦介质层20表面覆盖遮蔽层40,对遮蔽层40进行光刻及显影,而后参见图5,对外露的平坦介质层20进行蚀刻构成开孔21,去除遮蔽层40,参见图6。该开孔21面积可小于等于焊盘12的面积。

39.进一步的,开孔21处侧壁与焊盘12之间的锐角a,参见图1,是指平坦介质层20的开孔21的侧壁与焊盘12中与该侧壁相交且被平坦介质层20覆盖的端面的夹角a,锐角的角度范围为40

°‑

75

°

,最佳值60度。该锐角a能避免应力差异大导致的开裂,提高芯片可靠性。

40.本实用新型中,还包括有钝化层30,该钝化层30覆盖于平坦介质层20表面以及开孔21与焊盘12交界处。钝化层30是为了保护其所覆盖的化合物半导体器件,防止水汽入侵化合物半导体器件,以及避免机械碰撞,确保化合物半导体器件的可靠度佳。该钝化层30厚

度可估计需要设定,钝化层30材料为氧化硅或氮化硅,优选为氮化硅。

41.另外,由于钝化层30覆盖于平坦介质层20表面,则开孔21处侧壁的钝化层30与焊盘12中与该侧壁相交且被钝化层30覆盖的端面的夹角也为锐角,锐角的角度范围为40

°‑

75

°

,最佳值60度。

42.基于此,本实用新型还提出一种芯片,包括芯片10,该芯片10具有上述的一种芯片的表层结构。

43.本实施例中,该芯片10可为砷化镓芯片,其可以是砷化镓制程的功率放大器(pa),金属肖特基场效应晶体管(mesfet)、结型场效应晶体管(jfet)、高电子迁移率晶体管(hemt)和异质结双极晶体管(hbt)等。

44.实施例二

45.参见图1,一种芯片的表层结构,其主要结构与实施例一相同区别在于:平坦介质层20可为感光型的有机材料,例如hd8920等聚苯并恶唑pbo类似材料或者bcb,优选为pbo,制作的厚度可更厚,但不限于此。

46.其中,对于感光型有机材料的平坦介质层20,参见图7、图8,可采用黄光制程,直接对平坦介质层20进行光刻、显影,使其在焊盘12处开孔21。该开孔21面积可小于等于焊盘12的面积。

47.上述仅为本实用新型的具体实施方式,但本实用新型的设计构思并不局限于此,凡利用此构思对本实用新型进行非实质性的改动,均应属于侵犯本实用新型保护范围的行为。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1