含有具有电流聚焦层的选择器的存储器装置及其制造方法与流程

1.本公开大体上涉及存储器装置领域,并且具体地涉及用于磁阻随机存取存储器(mram)和相变存储器(pcm)装置的具有电流聚焦层的双向阈值开关(ots)选择器及其制造方法。

背景技术:

2.自旋转移矩(“stt”)是指磁性隧道结或自旋阀中的磁层取向由自旋极化电流修改的效应。一般地,电流是非极化的,其中电子具有随机自旋取向。自旋极化电流是电子由于优先自旋取向分布而具有非零净自旋的电流。自旋极化电流可通过使电流通过磁性极化层来生成。当自旋极化电流流过磁性隧道结或自旋阀的自由层时,自旋极化电流中的电子可将其角动量中的至少一些转移到自由层,从而对自由层的磁化产生扭矩。当足够量的自旋极化电流通过自由层时,可采用自旋转移矩以翻转自由层中的自旋取向(例如,改变磁化)。可采用自由层的不同磁化状态之间的磁性隧道结的电阻差以将数据存储在磁阻随机存取存储器(mram)单元内,取决于自由层的磁化是平行于还是反平行于偏振层(其也被称为参考层)的磁化。

技术实现要素:

3.根据本公开的一个方面,存储器单元包括双向阈值开关(ots)选择器,该双向阈值开关选择器含有:第一电极;第二电极;ots,该ots位于该第一电极与该第二电极之间;和电流聚焦层,该电流聚焦层含有位于该第一电极与该ots之间具有30nm或更小的宽度的离散的导电电流聚焦区;和存储器装置,该存储器装置定位成与该ots选择器电串联。

附图说明

4.图1和图2a是根据本公开的第一实施方案的制造具有电流聚焦层的ots选择器的方法中的步骤的竖直横截面图。

5.图2b、图2c和图2d是根据本公开的第一实施方案的替代配置的具有电流聚焦层的ots选择器的竖直横截面图。

6.图3a和图3b分别是根据本公开的第一实施方案的操作图2a和图2b的ots选择器的方法中的步骤的竖直横截面图。

7.图4a是根据本公开的第二实施方案的具有电流聚焦层的ots选择器的竖直横截面图。

8.图4b是根据本公开的第二实施方案的操作图4a的ots选择器的方法中的步骤的竖直横截面图。

9.图5a是根据本公开的第三实施方案的具有电流聚焦层的ots选择器的竖直横截面图。

10.图5b是根据本公开的第三实施方案的操作图5a的ots选择器的方法中的步骤的竖

直横截面图。

11.图5c是根据本公开的第三实施方案的替代配置的操作具有电流聚焦层的ots选择器的方法中的步骤的竖直横截面图。

12.图6a和图6b是根据本公开的各种实施方案的位于mram存储器单元中的具有电流聚焦层的ots选择器的竖直横截面图。

13.图7是根据本公开的各种实施方案的位于相变存储器单元中的具有电流聚焦层的ots选择器的竖直横截面图。

具体实施方式

14.本公开的实施方案提供用于存储器装置(诸如,磁阻随机存取存储器(mram)和相变存储器(pcm)单元)的具有电流聚焦层的双向阈值开关(ots)选择器(即,转向元件)及其制造方法。mram单元可以在高密度交叉点存储器阵列中使用,其中每个交叉点结由与mram单元串联的选择器组成。为了以低错误率进行操作,应控制选择器的电特性并使该电特性与mram单元的特性匹配。电流聚焦层改进选择器的电特性,并且当在交叉点阵列中与mram或pcm单元结合使用时实现较低的位错误率。具体地,电流聚焦层促进ots的小区中的电流聚焦和电场增强,这促进在ots中在一个或多个离散位置处形成导电细丝。因此,ots的特性可以以一种或多种方式改进。第一种是在第一次启动和/或操作期间减小接通选择器所需的电压。阈值电压的减小限制由于阈值电压过高而不能操作的交叉点阵列中的装置的数目,因此减小位错误率。第二种可能的改进是减小在关闭之前可维持选择器的最小电流。这一电流也称为保持电流。低保持电流允许在较低电流下读取存储器单元,从而降低存储器状态受读取操作干扰的概率,由此减小位错误率。额外的可能的改进包括改进的选择器特性分布和更长的耐久性。并非所有实施方案都必须提供所有可能的改进。

15.在第一实施方案中,由金属纳米团簇构成的不连续的导电除尘层用作电流聚焦层。在第二实施方案中,包括受限电流路径的金属-电介质复合层用作电流聚焦层。在第三实施方案中,跨该层施加电流和/或电压时形成导电细丝的丝状击穿层用作电流聚焦层。

16.附图未按比例绘制。在其中示出元件的单个实例的情况下可以重复元件的多个实例,除非明确地描述或以其他方式清楚地指出不存在元件的重复。序号诸如“第一”、“第二”和“第三”仅仅被用于标识类似的元件,并且在本公开的整个说明书和权利要求书中可采用不同序号。术语“至少一个”元件是指包括单个元件的可能性和多个元件的可能性的所有可能性。

17.相同的附图标号表示相同的元件或相似的元件。除非另有说明,具有相同附图标号的元件被假定具有相同的组成和相同的功能。除非另外指明,否则元件之间的“接触”是指提供元件共享的边缘或表面的元件之间的直接接触。如本文所用,定位在第二元件“上”的第一元件可以定位在第二元件的表面的外侧上或者第二元件的内侧上。如本文所用,如果在第一元件的表面和第二元件的表面之间存在物理接触,则第一元件“直接”定位在第二元件上。如本文所用,如果在第一元件和第二元件之间存在由至少一种导电材料构成的导电路径,则第一元件“电连接到”第二元件。如本文所用,“原型”结构或“过程中”结构是指随后在其中至少一个部件的形状或组成中被修改的瞬态结构。

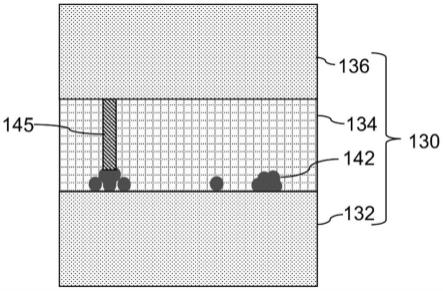

18.图1和图2a是根据本公开的第一实施方案的制造具有电流聚焦层的ots选择器130

的方法中的步骤的竖直横截面图,该ots选择器包括金属除尘层142。如图1所展示,金属除尘层142沉积在存储器单元的过程中的ots选择器(例如,转向元件)130的第一电极132上。

19.第一电极132可包括任何合适的导电材料,诸如金属,诸如钨、铜、钛、钌、金属合金;导电金属氮化物,诸如氮化钛、氮化钨或氮化钽;或导电碳类材料,诸如无定形碳、无定形硼掺杂碳、无定形氮掺杂碳(cn)、金属-碳合金或其它碳合金以及它们的层堆叠。

20.在一个实施方案中,本公开的第一实施方案的除尘层142是由多个离散纳米团簇构成的具有小于一个单层的厚度的亚单层膜。可例如通过至少一种元素金属的物理气相沉积来沉积金属除尘层142。金属除尘层142可基本上由至少一种元素金属(即,呈元素形式的金属元素)组成。至少一种元素金属可选自ti、zr、ir、mg、pt、w、ta、hf、cr、fe、cu、nb、mo、sc、y、pd、au、os、ru或rh。替代地,除尘层可包括金属氮化物,诸如tin。如果将除尘层142结合到mram存储器单元中,那么除尘层142可包括非磁性材料。

21.举例来说,在沉积除尘层142的一种方法中,使用不可混溶的两种金属(例如,ti和zr)。在第一电极132的顶部上沉积第一金属(例如,ti)的薄连续层。在这之后,在第一金属的顶部上沉积第二金属(例如,zr)的超薄层(例如,1个单层厚度或更小),使得zr的纳米团簇(例如,岛/液滴)形成在ti层上。ti层成为第一电极132的部分,而zr纳米团簇构成除尘层142。替代地,如果第一电极132包括与纳米团簇的材料(例如,zr)不混溶的材料(例如,ti),那么可省略第一层的沉积。可替代地使用其它合适的不混溶金属层对,诸如au/cr、cu/nb、fe/os、fe/ru、mo/sc、os/pt、sc/y或ti/zr。

22.沉积除尘层142的替代方法包括在碳类的第一电极132(诸如,碳或cn)上重复沉积超薄金属层(例如,3个单层或更少,诸如1到2个单层)。金属层可包括钌、钛和/或氮化钛。举例来说,堆叠可包括cn/ru、cn/ti/ru或cn/tin/ru。碳类材料充分改变超薄金属除尘层142的局部形态以改变界面粗糙度并形成金属除尘层的纳米团簇结构。

23.在沉积除尘层142的另一替代方法中,在碳类的第一电极132(诸如,碳或cnx)上沉积上述超薄金属除尘层142之后执行溅射蚀刻处理步骤。举例来说,包括cn/ru、cn/ti/ru、cn/tin/ru的堆叠的溅射蚀刻也可改变局部表面形态,使得金属除尘层142的区改变,使得第一电极132的表面在不连续金属除尘层142的区之间露出。

24.在一个实施方案中,金属除尘层142的厚度可在0.1nm至1.2nm的范围内,诸如0.1nm至0.8nm和/或0.2nm至0.5nm。在一个实施方案中,金属除尘层142具有亚单层厚度并且包括穿过其的开口。在一个实施方案中,金属除尘层142是不连续的,即,包括彼此不接触的多个纳米团簇。每个簇中的金属原子数量可在1至100的范围内。在这种情况下,金属除尘层142的厚度可在0.1nm至0.2nm的范围内。每个纳米团簇的宽度(即,平行于第一电极132的顶部表面的尺寸)可小于5nm,诸如小于2nm,诸如0.1nm至1nm,包括0.1nm至0.2nm。

25.如图2a所示,ots 134直接沉积在除尘层142上。随后在ots 134上方沉积第二电极136以完成选择器130。

26.如本文所用,双向阈值开关(ots)134是在高于阈值电压的电压下不结晶成低电阻状态,并且在跨ots材料层不经受高于阈值电压的电压时恢复到高电阻状态的装置。如本文所用,“双向阈值开关材料”是指在所施加的外部偏置电压下显示出非线性电阻率曲线,使得材料的电阻率随所施加的外部偏置电压的量值而减小的材料。换句话讲,双向阈值开关材料是非欧姆的,并且在较高的外部偏置电压下变得比在较低的外部偏置电压下更具导电

性。

27.在跨ots材料施加高于其阈值电压的电压期间,双向阈值开关材料(ots材料)在高电阻状态下可为非晶态的(例如,无定形的),并且在低电阻状态下可保持非晶态的(例如,保持无定形的)。当去除高于其阈值电压的高电压时,ots材料可恢复到高电阻状态。在整个电阻状态改变期间,双向阈值开关材料可保持非晶态的(例如,无定形的)。在一个实施方案中,双向阈值开关材料可包括在写入和读取状态下均表现出滞后的硫属化物材料层。硫属化物选择器可由si、ge、se、te和as的二元、三元或四元合金构成,并且掺杂有b、c、n、p、s、in、sn、sb、pb、zn、bi和/或o。示例性硫属化物选择器可为掺杂有n、si和/或c的site化合物、gete化合物、gese化合物、geseas化合物或geseaste化合物。

28.在一个实施方案中,可选择ots 134的材料,使得ots的电阻率在施加超过临界偏置电压量值(也称为阈值电压)的外部偏置电压时减小至少两个数量级(即,超过100倍)。在一个实施方案中,可选择ots 134的组分和厚度,使得临界偏置电压量值可在1v至4v的范围内,但临界偏置电压量值也可采用更小和更大的电压。ots 134的厚度可在例如5nm至40nm的范围内,诸如10nm至20nm,但也可采用更小和更大的厚度。

29.图2b是根据本公开的第一实施方案的替代配置的具有电流聚焦层的ots选择器130的竖直横截面图。在这一配置中,除尘层142的金属纳米团簇嵌入(即,包封)于电绝缘层144中。绝缘层144可形成于第一电极132和除尘层142上方,使得至少除尘层142的纳米团簇的顶部表面暴露在绝缘层144的顶部表面中。因此,除尘层142的纳米团簇接触沉积在除尘层142和绝缘层144上的ots 134。

30.绝缘层144可包括具有2nm或更小的厚度(诸如,0.1nm至1nm)的氧化硅、金属氧化物或氮化硅层。可使用选择性原子层沉积(ald)来沉积绝缘层144,使得绝缘层144仅润湿/粘附到第一电极132的材料但不会润湿/粘附到除尘层142的纳米团簇。替代地,可通过除尘层142的纳米团簇的氧化或氮化来形成绝缘层144。因此,绝缘层144可包括除尘层142的纳米团簇的金属的氧化物或氮化物。绝缘层可包括化学计量或非化学计量的sio

x

、tao

x

、tio

x

、geo

x

、sno

x

、hfo

x

、mgo

x

、sin

x

、alo

x

、vo

x

或nio

x

。

31.在一个实施方案中,ots选择器130可包括双层第一电极132,该双层第一电极包括金属氮化物铅下部导体(例如,tan或tin)和碳类上部导体(例如,无定形碳或cn)。除尘层142可包括超薄界面润湿层(例如,可与碳或cn混溶的ti或tin)和用于电流聚焦的不同金属(例如,zr)的离散纳米团簇。可在除尘层142上形成任选的绝缘层144。在除尘层142上方形成上述ots 134和第二电极(例如,金属、导电金属氮化物和/或碳类材料电极)136。如果需要,可在ots选择器130上方形成额外的封盖层,以将其与以下将更详细地描述的存储器装置分离。

32.图2c和图2d是根据本公开的第一实施方案的替代配置的具有电流聚焦层的ots选择器130的竖直横截面图。在图2c的配置中,除尘层142可位于ots 134的顶部表面上。在图2d的配置中,第一除尘层142a可定位为与ots 134的底部表面接触,并且第二除尘层142b可位于ots 134的顶部表面上。图2c和图2d的配置的除尘层可任选地嵌入于图2b所示的绝缘层144中。

33.图3a和图3b分别是根据本公开的第一实施方案的操作图2a和图2b的ots选择器130的方法中的步骤的竖直横截面图。在跨第一电极132与第二电极136之间的ots 134施加

电压或电流之后,导电细丝145(即,导电路径)穿过第一电极132与第二电极136之间的ots 134形成。细丝145的形成将ots选择器130从“关闭”(即,较高电阻)状态切换到“开启”(即,较低电阻)状态。操作图2c和图2d的ots选择器130的方法是类似的,不同之处在于细丝145可在形成期间向下延伸而不是向上延伸。

34.除尘层142的存在将注入到ots 134中的电流聚焦在一个或多个窄点处,并且将ots中的电流限制在狭窄区域,从而在ots 134的狭窄区中产生增强的电场。在不希望受特定理论束缚的情况下,发明人认为这导致在除尘层142中的纳米团簇上方的ots 134的特定区中形成相对狭窄的细丝145。细丝145可具有30nm或更小的宽度(即,在平行于第一电极132的顶部表面的方向上),诸如0.1nm至20nm,例如0.5nm至5nm,诸如1nm至3nm。

35.电流的点注入降低保持电流并调谐ots选择器130的偏移电压,并且因此改进ots选择器130的性能。另外,电流的点注入可避免使用ots选择器130的“第一次启动”初始化过程的必要性,其需要在ots选择器130的第一电极与第二电极之间施加高电压以初始化ots选择器130。替代地,其可减小在ots选择器130的“第一次启动”初始化过程期间所需的电压量值。

36.图4a是根据本公开的第二实施方案的具有包括金属-电介质复合层244的电流聚焦层的ots选择器130的竖直横截面图。

37.金属-电介质复合层244包括嵌入于绝缘介电基质246中的离散导电相区242。导电相区242用作穿过介电基质246的受限电流路径。鉴于复合材料可具有导电区和介电区的随机分布,电流聚焦路径可以是间接的(迂回的)并且不同于图4a中示意性地示出的直接导电路径。在一个实施方案中,金属-电介质复合层244可包括电流受限路径(ccp)复合材料,诸如cu:alox(即,掺杂铜的氧化铝)、ag:alox(即,掺杂银的氧化铝)或agin:mg-zn-o(即,掺杂银和铟的氧化镁稳定氧化锆)纳米复合材料。举例来说,对于agin:mg-zn-o纳米复合材料,导电agin区242(即,氧化镁稳定的氧化锆基质246中的银铟导电相区)可具有约5nm至10nm的直径,诸如约7nm。在一个实施方案中,导电区242可具有10nm或更小的宽度,诸如5nm至10nm,并且包括任何合适的金属,诸如铜、银、金、铟或它们的合金(例如,agin)。介电基质可包括任何合适的电介质,诸如金属氧化物,例如氧化铝、氧化锆、稳定的氧化锆(例如,氧化镁稳定的氧化锆等)或氧化硅。合适的电介质也可包括氮化物,诸如氮化硅。

38.图4b是根据本公开的第二实施方案的操作图4a的ots选择器130的方法中的步骤的竖直横截面图。在跨第一电极132与第二电极136之间的ots 134施加电压或电流之后,导电细丝145(即,导电路径)穿过第一电极132与第二电极136之间的ots 134形成。细丝145的形成将ots选择器130从“关闭”(即,较高电阻)状态切换到“开启”(即,较低电阻)状态。

39.复合层244中的纳米级导电区242的存在将注入到ots 134中的电流聚焦在一个或多个窄点处,并且将ots中的电流限制到狭窄区域,从而在ots 134的狭窄区中产生增强的电场。在不希望受特定理论束缚的情况下,发明人认为这导致在纳米级导电区242上方的ots 134的特定区中形成相对狭窄的细丝145。细丝145可具有30nm或更小的宽度(即,在平行于第一电极132的顶部表面的方向上),诸如0.1nm至20nm,例如0.5nm至5nm,诸如1nm至3nm。

40.图5a是根据本公开的第三实施方案的具有电流聚焦层的ots选择器的竖直横截面图,该电流聚焦层包括跨介电层施加电流和/或电压时形成导电细丝的丝状击穿层344。

41.丝状击穿层344可包括任何合适的介电氧化物或氮化物,在跨丝状击穿层施加电流和/或电压时,该丝状击穿层形成导电细丝。举例来说,丝状击穿层344可包括化学计量或非化学计量的电介质或半导体材料,例如sio

x

、tao

x

、tio

x

、geo

x

、sno

x

、hfo

x

、mgo

x

、sin

x

、alo

x

、vo

x

、nio

x

、gese、gete、zro

x

、zrte或它们的三元或四元化合物。丝状击穿层344可具有2nm或更小的厚度,诸如0.1nm至1nm。

42.图5b是根据本公开的第三实施方案的操作图5a的ots选择器130的方法中的步骤的竖直横截面图。当跨丝状击穿层344施加足够大的电压时,将发生基质(例如,电介质或半导体)击穿,从而产生穿过丝状击穿层344的导电路径(例如,狭窄导电细丝)342。基质击穿的机制可以是氧或氮空位形成(例如,如可在氧化钛空位/阻挡调制的电阻ram存储器单元中发生)和/或金属桥形成(例如,如可在类似于反熔丝或导电桥类型电阻ram存储器单元的氧化硅中发生)。导电细丝342可具有10nm或更小的宽度,诸如0.5nm至2nm,并且可包括氧化物或氮化物的非氧或氮化物组分(例如,si、ti、ta、mg、hf、al等)。

43.在跨第一电极132与第二电极136之间的ots 134和丝状击穿层344施加电压或电流之后,导电细丝342穿过丝状击穿层344形成,并且提供在与ots 134的界面处聚焦的电流/场。这使得导电细丝145(即,导电路径)穿过在第一电极132与第二电极136之间的ots 134形成。细丝145的形成将ots选择器130从“关闭”(即,较高电阻)状态切换到“开启”(即,较低电阻)状态。

44.导电细丝342在丝状击穿层344中的形成将注入到ots 134中的电流聚焦在一个或多个窄点处,并且将ots中的电流限制到狭窄区域,从而在ots 134的狭窄区中产生增强的电场。在不希望受特定理论束缚的情况下,发明人认为这导致在导电细丝342上方的ots 134的特定区中形成相对狭窄的细丝145。细丝145可具有30nm或更小的宽度(即,在平行于第一电极132的顶部表面的方向上),诸如0.1nm至20nm,例如0.5nm至5nm,诸如1nm至3nm。

45.图5c是根据本公开的第三实施方案的替代配置的操作具有电流聚焦层的ots选择器的方法中的步骤的竖直横截面图。在这一实施方案中,至少一个额外电极层346和/或348位于第一电极132与ots 134之间。举例来说,金属源电极346可形成于第一电极132与丝状击穿层344之间。举例来说,当第一电极132包括碳类材料,诸如cn时,金属源电极346可包括薄金属层,诸如ta、cu、ti、au或ag。金属源电极346可提供在丝状击穿层344中形成导电桥的金属原子源。在另一实例中,缓冲电极348可位于丝状击穿层344与ots 134之间。缓冲电极348可包括碳类材料,诸如无定形碳或cn;或金属层,诸如ru或rh。在一个实施方案中,电极346和348两者可存在于ots选择器130中。

46.本公开的各种实施方案提供电流聚焦层,该电流聚焦层包括具有30nm或更小的宽度,诸如0.5nm至20nm,包括5nm至10nm的离散的导电电流聚焦区。电流聚焦区可包括纳米团簇、复合材料中的导电相区或丝状击穿层中的导电细丝。这允许装置大小减小,同时仍然以低泄漏(即,关闭)电流向ots 134提供足够的电压。为ots 134中的细丝145形成提供成核位点的电流聚焦区,并且将第一次启动(形成)电压消除或减小到接近或等于ots阈值电压。这可消除建立装置阈值“老化”的设置,节省时间并且降低处理成本。还可获得减小的阈值电压,这致使存储器单元的电流和功率减小。也可获得由于丝状或点接触引起的较低保持电流,且有助于改进ots选择器130的性能。

47.在一个实施方案中,上述第一实施方案、第二实施方案或第三实施方案的ots选择

器130可用于图6a和图6b中所示的磁阻随机存取存储器(“mram”)单元500中。如上所述,第一实施方案、第二实施方案或第三实施方案的ots选择器130包括电流聚焦层44,该电流聚焦层包括包括纳米团簇、导电相区或导电细丝的离散的导电电流聚焦区42。每个mram单元500可含有与ots选择器130电串联的磁性隧道结(mtj)150。在一个实施方案中,mram单元500可包括自旋转移扭矩(stt)型mram单元。

48.参考图6a,第一导电线(例如,位线或字线)120形成于衬底110上方。然后通过在第一导电线120之间沉积介电材料层并且使介电材料层平坦化来在第一导电线120之间形成介电轨道(未在图6a的视图中展示)。

49.包括任选的金属封盖层158和mtj堆叠150的层堆叠形成在位于衬底110上方的第一导电线120上方。从顶部到底部,堆叠包括金属封盖层158、参考层152(其也称为磁性固定层)、隧道阻挡层154和自由层156,它们一起形成stt存储器单元的mtj堆叠150。mtj堆叠150的厚度可在10nm至40nm的范围内,诸如20nm至30nm。

50.金属封盖层158包括非磁性金属材料,诸如至少一个非磁性过渡金属或非磁性过渡金属合金。举例来说,金属封盖层158可包括以下并且或可基本上由以下组成:ti、v、cr、mn、zr、nb、mo、tc、ru、rh、hf、ta、w、re、os、ir、它们的合金或导电金属氮化物(例如,tan、tin)或它们的导电金属碳化物(例如,wc)。可通过物理气相沉积或化学气相沉积来沉积金属封盖层158。金属封盖层158的厚度可在1nm至20nm的范围内,诸如2nm至10nm,但也可采用更小和更大的厚度。

51.参考层152可具有固定的磁化方向,其可以是水平方向或竖直方向。参考层152可形成为单个铁磁性材料层或多个铁磁材料层,其彼此磁性耦合以始终提供相同的磁化方向。参考层152可包括co/ni多层结构或co/pt多层结构。在一个实施方案中,参考层152可额外包括由具有在0.2nm至0.5nm的范围内的厚度的钽或钨构成的薄非磁性层,和具有在0.5nm至3nm的范围内的厚度的薄cofeb层。参考层152的厚度可在2nm至5nm的范围内。

52.任选地,参考层152可设置在合成的反铁磁体(saf)结构中,该合成的反铁磁体结构包括硬磁化层(未明确展示)、反铁磁耦合层(例如,ru层,未明确展示)和参考层152。在参考层152作为saf结构的组件提供的情况下,硬磁化层的磁化和磁性固定层的磁化可通过反铁磁耦合层进行反铁磁性耦合。

53.隧道阻挡层154可包括隧道阻挡介电材料,诸如氧化镁或氧化铝。隧道阻挡层154可具有在0.6nm至2nm的范围内的厚度,诸如0.8nm至1.2nm。隧道阻挡层154接触参考层152,并且在参考层152与自由层156之间提供电流的自旋敏感隧穿。换句话讲,穿过隧道阻挡层154的电流的量取决于参考层152与自由层156之间的磁化的相对对准,即磁化方向是否彼此平行或反平行。

54.自由层156可形成为单个铁磁性材料层或多个铁磁材料层,其彼此磁性耦合以始终提供相同的磁化方向。自由层156的厚度小于2nm,并且优选地小于1.5nm,诸如0.8nm至1.5nm。举例来说,自由层156可包括cofeb层和/或cofe层。可通过沿竖直方向向上或向下流动电流来编程自由层156。额外层(未展示)可包括在mtj 150中。

55.然后将上述层图案化到存储器柱结构(158、152、154、156和130)中。可使用任何合适的图案化方法。举例来说,光刻和蚀刻可用于对ots选择器130层的堆叠进行图案化,而离子束铣削可用于对mtj堆叠150和金属封盖层158进行图案化。然后形成介电隔离结构60,使

得其横向包围存储器柱结构(158、152、154、156和130)的二维阵列。

56.每个存储器柱结构(158、152、154、156和130)包括含有mtj 150的mram存储器单元500,其中隧道阻挡层154位于参考层152与自由层156之间。金属封盖层158位于mtj 150的一侧上(例如,上方)。ots选择器130位于mtj 150的另一侧上(例如,下方)。

57.通过沉积一个或多个导电层,然后通过反应离子蚀刻(rie)对一个或多个导电层进行图案化以形成线180,可在存储器柱结构(158、152、154、156和130)上方形成第二导电线180(例如,位线或字线中的另一个)。然后通过在第二导电线180之间沉积介电材料层并且使介电材料层平坦化来在第二导电线180之间形成第二介电轨道190。

58.图6b示出mram存储器单元500的替代性实施方案。在这一实施方案中,ots选择器130形成于mtj 150上方。

59.在图7中所示的另一实施方案中,上述第一实施方案、第二实施方案或第三实施方案的ots选择器130可用于含有相变随机存取存储器(“pcram”或“pram”)装置450的相变存储器(pcm)单元600中,而不是用于mram存储器单元500中。

60.pcm装置450包括非金属导电材料层478。可用于层478的示例性非金属导电材料包括无定形碳、无定形硼掺杂碳或无定形氮掺杂碳(cn)。非金属导电材料层478厚度在10nm至50nm的范围内,诸如20nm至30nm,但也可采用更小和更大的厚度。

61.位于层478下方的相对薄的上部金属材料层476可包括元素金属,诸如w或ru;和/或导电金属化合物材料,诸如tin、tan或wn。上部金属材料层476可具有在1nm至5nm的范围内的厚度,诸如2nm至3nm,但也可采用更小和更大的厚度。

62.包括相变存储器材料层474的存储器材料层位于层476下方。如本文所用,“相变存储器材料”是指具有提供不同电阻率的至少两个不同相位的材料。可例如通过控制从受热状态冷却的速率以提供具有更高电阻率的无定形状态和具有更低电阻率的多晶状态来提供至少两个不同相位。在这种情况下,可通过在加热到无定形状态之后加快相变存储器材料的淬火来实现相变存储器材料的更高电阻率状态,并且可通过在加热到无定形状态之后减慢相变存储器材料的冷却来实现相变存储器材料的更低电阻率状态。

63.示例性相变存储器材料包括但不限于碲化锗锑化合物诸如ge2sb2te5(gst)、锗锑化合物、碲化铟锗化合物、碲化铝硒化合物、碲化铟硒化合物和碲化铝铟硒化合物。这些化合物(例如,化合物半导体材料)可为掺杂的(例如,氮掺杂的gst)或未掺杂的。因此,电阻性存储器材料层可包括选自以下的材料和/或可基本上由选自以下的材料组成:碲化锗锑化合物、锗锑化合物、碲化铟锗化合物、碲化铝硒化合物、碲化铟硒化合物或碲化铝铟硒化合物。在这种情况下,至少一个存储器材料层的厚度可在10nm至60nm的范围内,诸如20nm至50nm和/或25nm至35nm,但也可采用更小和更大的厚度。

64.下部第一金属材料层472位于层474下方。下部金属材料层472可包括元素金属,诸如w或ru;和/或导电金属化合物材料,诸如tin、tan或wn。下部金属材料层472可具有在1nm至5nm的范围内的厚度,诸如2n至3nm,但也可采用更小和更大的厚度。在替代性实施方案中,pcm装置450可位于ots选择器130下方,类似于图6b中针对mram单元500所示的配置。

65.根据本公开的实施方案,存储器单元(500,600)包括双向阈值开关(ots)选择器130和定位成与ots选择器130电串联的存储器装置(150,450),该双向阈值开关选择器含有第一电极132、第二电极136、位于第一电极与第二电极之间的ots 134和含有离散的导电电

流聚焦区42的电流聚焦层44,该离散的导电电流聚焦区位于第一电极132与ots 134之间,具有30nm或更小的宽度。在一个实施方案中,离散的导电电流聚焦区42具有0.5nm至20nm的宽度。

66.在第一实施方案中,电流聚焦层44包括导电除尘层142,并且离散的导电电流聚焦区42包括除尘层142的导电纳米团簇。导电纳米团簇可包括选自ti、zr、ir、mg、pt、w、ta、hf、cr、fe、cu、nb、mo、sc、y、pd、au、os、ru或rh或导电金属氮化物的元素金属。

67.导电纳米团簇可位于第一电极132的与导电纳米团簇的材料不混溶的金属层上。举例来说,导电纳米团簇和金属层包括选自zr/ti、au/cr、cu/nb、fe/os、fe/ru、mo/sc、os/pt、sc/y或ti/zr的不混溶金属层对。

68.在图2a所示的配置中,ots 134包围并直接接触除尘层142的导电纳米团簇。在图2b所示的替代配置中,除尘层142的导电纳米团簇嵌入于电绝缘层144中,使得导电纳米团簇的表面暴露于绝缘层的直接接触ots 134的表面。ots 134直接接触除尘层142的导电纳米团簇的暴露表面。

69.在图4a所示的第二实施方案中,电流聚焦层44包括金属-电介质复合层244,并且离散的导电电流聚焦区42包括嵌入于复合层244的介电基质246中的金属相区242。金属相区242可包括铜、银、金、铟或它们的合金,并且介电基质246可包括氧化铝、氧化锆、稳定的氧化锆或氧化硅。

70.在图5a和图5b所示的第三实施方案中,电流聚焦层144包括在跨丝状击穿层施加电流和/或电压时形成导电细丝342的丝状击穿层344,并且离散的导电电流聚焦区包括导电细丝342。丝状击穿层344可包括选自sio

x

、tao

x

、tio

x

、geo

x

、sno

x

、hfo

x

、mgo

x

、sin

x

、alo

x

、vo

x

、nio

x

、gese、gete、zro

x

、zrte或它们的三元或四元化合物的化学计量或非化学计量的电介质或半导体材料。

71.存储器装置(150,450)可包括磁性隧道结150或相变存储器装置450。通常,第一实施方案、第二实施方案或第三实施方案的ots选择器130可与任何配置中(诸如,在交叉点存储器架构中)的任何存储器装置一起使用以帮助防止潜行路径电流。

72.操作本公开的实施方案的存储器单元的方法包括跨第一电极132与第二电极136之间的ots 134施加电压或电流,以穿过第一电极与第二电极之间的ots 134形成导电细丝145,以将ots选择器130从较高电阻状态切换为较低电阻状态。离散的导电电流聚焦区42将注入到ots 134中的电流聚焦在一个或多个点处,该一个或多个点限制ots中的电流并且在ots的与导电电流聚焦区42邻近的特定区中形成导电细丝145。

73.制造存储器单元(500,600)的方法包括形成ots选择器130并且形成定位成与ots选择器130电串联的存储器装置(150,450)。在第一实施方案中,电流聚焦层44包括导电除尘层142,并且离散的导电电流聚焦区44包括除尘层142的导电纳米团簇。

74.第一实施方案的方法可进一步包括在第一电极上沉积第一金属的连续层,并且在连续层上沉积与第一金属不混溶的第二金属,以在连续层上形成第二金属的导电纳米团簇。

75.替代地,第一实施方案的方法可进一步包括在碳类材料上沉积金属,其中碳类材料改变金属的局部形态以形成导电纳米团簇。替代地,第一实施方案的方法可进一步包括溅射蚀刻导电除尘层以形成导电纳米团簇。

76.虽然前面提及特定优选实施方案,但是将理解本公开不限于此。本领域的普通技术人员将会想到,可对所公开的实施方案进行各种修改,并且此类修改旨在落在本公开的范围内。在本公开中示出采用特定结构和/或构型的实施方案,应当理解,本公开可以以功能上等同的任何其他兼容结构和/或构型来实践,前提条件是此类取代不被明确地禁止或以其他方式被本领域的普通技术人员认为是不可能的。本文引用的所有出版物、专利申请和专利均以引用方式全文并入本文。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1