半导体结构及其形成方法与流程

1.本技术涉及半导体领域,尤其涉及一种半导体结构及其形成方法。

背景技术:

2.温度变化对芯片的工作装态、电路性能有影响。芯片在工作时,输入功率只有一部分作有用功输出,还有很多的电能转化成热能,使芯片中元器件温度升高。而元器件允许的工作温度都是有限的,如果实际温度超过了元器件的允许温度,则元器件的性能会变坏,甚至烧毁。晶体管、电阻、电容、变压器、印制电路板、存储器都是如此。

3.现有虽然可以使用一些控温器件对芯片的温度进行控制,但是控温效率不高,并且控温器件与芯片的集合封装在一起使得整个器件的体积会较大。

技术实现要素:

4.本技术一些实施例提供了一种半导体结构,包括:

5.半导体衬底,所述半导体衬底包括芯片区和围绕芯片区的控温区;

6.位于所述控温区的珀尔帖器件,所述珀尔帖器件包括位于所述控温区的半导体衬底中且沿着所述芯片区边界方向交替排布的若干p型掺杂区和若干n型掺杂区;位于所述n型掺杂区和p型掺杂区远离芯片区一侧的第一端金属层和第二端金属层,所述第一端金属层电连接于所述若干n型掺杂区,所述第二端金属层电连接于所述若干p型掺杂区;位于所述n型掺杂区和p型掺杂区靠近芯片区一侧的半导体衬底中的第三端金属层,所述第三端金属层电连接于所述n型掺杂区与p型掺杂区。

7.在一些实施例中,所述第三端金属层为长条形的金属层,所述长条形的金属层电连接于所有的所述n型掺杂区和所述p型掺杂区。

8.在一些实施例中,所述第三端金属层包括若干依次间隔的第三端子金属层,每一个第三端子金属层电连接于至少一对相邻的n型掺杂区和p型掺杂区。

9.在一些实施例中,所述n型掺杂区和p型掺杂区靠近芯片区一侧的半导体衬底中具有暴露出所述n型掺杂区和p型掺杂区的靠近芯片区的一侧侧壁表面的第一沟槽,所述第三端金属层填充满所述第一沟槽。

10.在一些实施例中,所述第一端金属层和第二端金属层均包括向远离芯片区的方向凸出的若干齿状部和连接于所述若干齿状部的本体部,所述本体部与相应的n型掺杂区和p型掺杂区电连接。

11.在一些实施例中,所述第一端金属层位于第二端金属层下方,且所述第一端金属层位于所述n型掺杂区和p型掺杂区远离芯片区一侧的半导体衬底中;所述半导体结构还包括介质层,所述第一端金属层和第二端金属层通过所述介质层隔离。

12.在一些实施例中,所述半导体结构还包括若干第一连接金属垫和连接于每个所述第一连接金属垫上表面的第一金属插塞,所述第一连接金属垫位于所述p型掺杂区远离芯片区一侧的半导体衬底中且与所述p型掺杂区远离芯片区的一侧电连接,所述第二端金属

层通过位于所述介质层中的第一金属插塞与相应的第一连接金属垫连接。

13.在一些实施例中,所述第一端金属层位于第二端金属层上方,且所述第二端金属层位于所述n型掺杂区和p型掺杂区远离芯片区一侧的半导体衬底中;所述半导体结构还包括介质层,所述第一端金属层和第二端金属层通过所述介质层隔离。

14.在一些实施例中,所述半导体结构还包括若干第二连接金属垫和连接于每个所述第二连接金属垫上表面的第二金属插塞,所述第二连接金属垫位于所述n型掺杂区远离芯片区一侧的半导体衬底中且与所述n型掺杂区远离芯片区的一侧电连接,所述第一端金属层通过位于所述介质层中的第二金属插塞与相应的第二连接金属垫连接。

15.在一些实施例中,所述n型掺杂区和p型掺杂区通过离子注入工艺形成。

16.在一些实施例中,所述控温区中的所述珀尔帖器件沿着所述芯片区边界方向包围所述芯片区。

17.在一些实施例中,所述第一端金属层连接电源正极,所述第二端金属层连接电源负极。

18.在一些实施例中,所述芯片区包含半导体芯片,所述半导体结构还包括保护环器件,所述保护环器件包括若干层金属层和将相邻层的金属层连接的金属插塞,所述保护环器件设置于所述珀尔帖器件和所述半导体芯片之间,且围绕所述半导体芯片。

19.本技术一些实施例还提供了一种半导体结构的形成方法,包括:

20.提供半导体衬底,所述半导体衬底包括芯片区和围绕芯片区的控温区;

21.在所述控温区形成珀尔帖器件,包括:

22.在位于所述控温区的半导体衬底中形成沿着所述芯片区边界方向交替排布的若干p型掺杂区和若干n型掺杂区;

23.形成位于所述n型掺杂区和p型掺杂区远离芯片区一侧的第一端金属层和第二端金属层,所述第一端金属层电连接于所述若干n型掺杂区,所述第二端金属层电连接于所述若干p型掺杂区;

24.形成位于所述n型掺杂区和p型掺杂区靠近芯片区一侧的半导体衬底中的第三端金属层,所述第三端金属层电连接于所述n型掺杂区与p型掺杂区。

25.在一些实施例中,所述第三端金属层的形成过程包括:在所述n型掺杂区和p型掺杂区靠近芯片区一侧的半导体衬底中形成第一沟槽,所述第一沟槽暴露出所述n型掺杂区和p型掺杂区的靠近所述芯片区的一侧侧壁表面;在所述第一沟槽中填充金属形成第三端金属层。

26.在一些实施例中,所述第一端金属层和第二端金属层的形成过程包括:在所述n型掺杂区的远离所述芯片区的一侧半导体衬底中形成梳状的第二沟槽,所述第二沟槽暴露出所述若干n型掺杂区的远离所述芯片区的一侧的侧壁表面;在每一个所述p型掺杂区远离芯片的一侧半导体衬底中形成若干第三沟槽,每一个所述第三沟槽相应的暴露出一个所述p型掺杂区远离芯片的一侧侧壁表面;在所述梳状的第二沟槽中填充金属形成第一端金属层,在所述若干第三沟槽中填充金属,形成若干第一连接金属垫;在所述半导体衬底上形成介质层,所述介质层中形成有与相应的第一连接金属垫连接若干第一金属插塞;在所述介质层上形成与若干第一金属插塞连接的第二端金属层。

27.在一些实施例中,所述第一端金属层和第二端金属层的形成过程包括:在所述p型

掺杂区的远离所述芯片区的一侧半导体衬底中形成梳状的第四沟槽,所述第四沟槽暴露出所述若干p型掺杂区的远离所述芯片区的一侧的侧壁表面;在每一个所述n型掺杂区远离芯片的一侧半导体衬底中形成若干第五沟槽,每一个所述第五沟槽相应的暴露出一个所述n型掺杂区远离芯片的一侧侧壁表面;在所述梳状的第四沟槽中填充金属形成第二端金属层,在所述若干第五沟槽中填充金属,形成若干第二连接金属垫;在所述半导体衬底上形成介质层,所述介质层中形成有与相应的第二连接金属垫连接若干第二金属插塞;在所述介质层上形成与若干第二金属插塞连接的第一端金属层。

28.在一些实施例中,所述n型掺杂区和p型掺杂区的形成过程包括:在所述控温区中形成凹槽;在所述凹槽中填充满碲化铋材料;对所述碲化铋材料进行掺杂,形成n型掺杂区和p型掺杂区。

29.在一些实施例中,还包括:在所述芯片区形成半导体芯片,在所述珀尔帖器件和所述半导体芯片之间形成围绕所述半导体芯片的保护环器件,所述保护环器件包括若干层金属层和将相邻层的金属层连接的金属插塞。

30.本技术前述一些实施例中的半导体器件,由于第三端金属层作为冷端是位于所述n型掺杂区和p型掺杂区靠近芯片区一侧的半导体衬底中的,第一端金属层和第二端金属层作为热端是位于所述n型掺杂区和p型掺杂区远离芯片区一侧的,因而通过第三端金属层可以横向直接吸收芯片区的半导体衬底中形成的元器件产生的热量,从而提高温度控制的效率,并且由于珀尔帖器件是位于芯片区周围的控温区中,后续可以与芯片区形成的半导体芯片一体封装,不会占据太大的体积。

附图说明

31.图1-图7为本技术一些实施例中半导体器件的结构示意图;

32.图8-图11为另一些实施例中半导体器件的结构示意图;

33.图12-图13为又一些实施例中半导体器件的结构示意图。

具体实施方式

34.下面结合附图对本技术的具体实施方式做详细的说明。在详述本技术实施例时,为便于说明,示意图会不依一般比例作局部放大,而且所述示意图只是示例,其在此不应限制本技术的保护范围。此外,在实际制作中应包含长度、宽度及深度的三维空间尺寸。

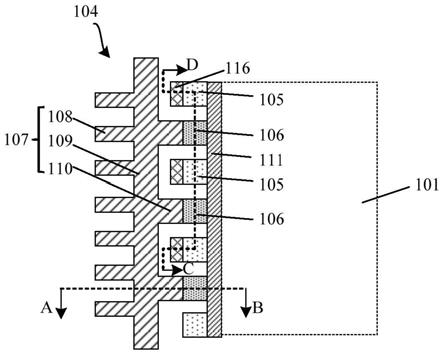

35.本技术一些实施例提供了一种半导体器件,参考图2-图7,图3和图6为图2中的珀尔帖器件的部分放大结构示意图,图4为图3沿切割线ab方向的剖面结构示意图,图5为图3沿切割线cd方向的剖面结构示意图,图7为图6沿切割线ab方向的剖面结构示意图,包括:

36.半导体衬底100,所述半导体衬底100包括芯片区101和围绕芯片区101的控温区102;

37.位于所述控温区102的珀尔帖器件104,所述珀尔帖器件104包括位于所述控温区102的半导体衬底100中且沿着所述芯片区101边界方向交替排布的若干p型掺杂区105和若干n型掺杂区106(参考图3和图5);位于所述n型掺杂区106和p型掺杂区105远离芯片区101一侧的第一端金属层107(参考图3,为方便示意,图3中未示出第二端金属层112)和第二端金属层112(参考图6,为方便示意,图6中未示出第一端金属层107),所述第一端金属层107

电连接于所述若干n型掺杂区106,所述第二端金属层112电连接于所述若干p型掺杂区105;位于所述n型掺杂区106和p型掺杂区105靠近芯片区101一侧的半导体衬底100中的第三端金属层111(参考图3和图4),所述第三端金属层111电连接于所述n型掺杂区106与p型掺杂区105。

38.所述半导体衬底100的材料可以为硅(si)、锗(ge)、或硅锗(gesi)、碳化硅(sic);也可以是绝缘体上硅(soi),绝缘体上锗(goi);或者还可以为其它的材料,例如砷化镓等

ⅲ‑ⅴ

族化合物。本实施例中,所述半导体衬底100的材料为硅。

39.所述芯片区101中为包含半导体芯片或集成电路的区域,所述半导体芯片可以为传感器芯片、存储器芯片或者具有其他功能的芯片。所述控温区102围绕所述芯片区101并与所述芯片区四周边缘接触,所述控温区102的珀尔帖器件104,所述珀尔帖器件104通过半导体制冷效应控制所述芯片区101的温度,以使得所述芯片区101的温度保持在预定的温度,防止芯片区101中的半导体芯片或集成电路因温度过高而性能下降。

40.参考图3和图5,所述n型掺杂区和p型掺杂区的数量为至少为一个,所述n型掺杂区和p型掺杂区的数量均为多个时,所述多个所述n型掺杂区和p型掺杂区沿着芯片区的边界延伸方向交替排布。

41.在一些实施例中,所述n型掺杂区和p型掺杂区通过离子注入工艺形成。具体的,向控温区102的半导体衬底100中的若干分立的第一区域注入n型杂质离子,形成若干n型掺杂区,向控温区102的半导体衬底100中的若干分立的第二区域注入p型杂质离子,形成若干p型掺杂区。所述离子注入注入的杂质离子为p型的杂质离子,所述p型的杂质离子为硼离子、镓离子或铟离子一种或几种。在另一些实施例中,所述n型掺杂区106和p型掺杂区105的形成过程还可以包括:在所述控温区102中形成凹槽;在所述凹槽中填充满碲化铋材料;对所述碲化铋材料进行掺杂,形成n型掺杂区106和p型掺杂区105。

42.本实施例中,参考图3和图4,所述第三端金属层111为长条形的金属层,所述长条形的金属层111电连接于所有的所述n型掺杂区106和所述p型掺杂区105。所述珀尔帖器件104在进行制冷时,在所述第一端金属层107和所述第二端金属层112上施加电压(具体的,将第一端金属层107接电源的正极,将所述第二端金属层112接电源的负极),所述n型掺杂区和p型掺杂区连接第三端金属层111的一端作为冷端,通过第三端金属层111吸收所述芯片区产生的热量,本技术中由于第三端金属层111是位于所述n型掺杂区106和p型掺杂区105靠近芯片区101一侧的半导体衬底100中的,因而通过第三端金属层111可以横向直接吸收芯片区的半导体衬底中形成的元器件产生的热量,从而提高温度控制的效率,并且由于珀尔帖器件104是位于芯片区101周围的控温区102中,后续可以与芯片区101形成的半导体芯片一体封装,不会占据太大的体积。

43.在一些实施例中,所述第三端金属层111可以为w、al、cu、ag、au、pt、ni、ti、tin、tan、ta、tac、tasin、wn、wsi中的一种材料所形成的单层结构或者为上述材料所组成群组中的两种以上材料所形成的叠层结构。

44.在一些实施例中,所述n型掺杂区106和p型掺杂区105靠近芯片区101一侧的半导体衬底100中具有暴露出所述n型掺杂区106和p型掺杂区105的靠近芯片区101的一侧侧壁表面的第一沟槽121(参考图9),所述第三端金属层111填充满所述第一沟槽。

45.参考图3-图7,所述第一端金属层107和所述第二端金属层112位于不同的层(需要

说明的是,为了方便示意,图3中仅示出了第一端金属层107,未示出第二端金属层112,图7中仅示出了第二端金属层112,未示出第一端金属层107)。本实施例中,所述第一端金属层107位于所述第二端金属层112的下方,所述第一端金属层107为下层或前层,所述第二端金属层112为上层或当层。在其他一些实施例中,第一端金属层位于所述第二端金属层的上方,所述第一端金属层为上层或当层,所述第二端金属层为下层或前层。

46.在一些实施例中,所述第一端金属层107和所述第二端金属层112可以为w、al、cu、ag、au、pt、ni、ti、tin、tan、ta、tac、tasin、wn、wsi中的一种材料所形成的单层结构或者为上述材料所组成群组中的两种以上材料所形成的叠层结构。

47.在一些实施例中,所述第一端金属层107(参考图3)和第二端金属层112(参考图6)均包括向远离芯片区101的方向凸出的若干齿状部(108或113)和连接于所述若干齿状部(108或113)的本体部(109或114),所述本体部(109或114)与相应的n型掺杂区106和p型掺杂区105电连接,通过前述特定的形状,第一端金属层107和第二端金属层112作为热端时,单位体积内的散热面积更大,提高了散热的效率。具体的,所述第一端金属层107(参考图3)包括向远离芯片区101的方向凸出的若干齿状部108和连接于所述若干齿状部108的本体部109,所述本体部109与相应的n型掺杂区106电连接,在一些实施例中,所述本体部109通过连接部110与相应的n型掺杂区106电连接。所述第二端金属层112(参考图6)包括向远离芯片区101的方向凸出的若干齿状部113和连接于所述若干齿状部113的本体部114,所述本体部114与相应的p型掺杂区105电连接,在一些实施例中,所述本体部114通过连接部115与相应的p型掺杂区105电连接。

48.本实施例中,参考图3-图4以及图6-图7,所述第一端金属层107位于第二端金属层112下方,且所述第一端金属层107位于所述n型掺杂区106和p型掺杂区105远离芯片区101一侧的半导体衬底100中。在一些实施例中,参考图7,所述半导体结构还包括介质层118,所述第一端金属层107和第二端金属层112通过所述介质层118隔离。

49.在一些实施例中,所述介质层118位氧化硅、氮化硅、氮氧化硅、fsg(掺氟的二氧化硅)、bsg(掺硼的二氧化硅)、psg(掺磷的二氧化硅)或bpsg(掺硼磷的二氧化硅)、低介电常数材料中的一种材料所形成的单层结构或者为上述材料所组成群组中的两种以上材料所形成的叠层结构。

50.在一些实施例中,参考图7,所述半导体结构还包括若干第一连接金属垫116和连接于每个所述第一连接金属垫116上表面的第一金属插塞117,所述第一连接金属垫116位于所述p型掺杂区105远离芯片区101一侧的半导体衬底100中且与所述p型掺杂区105远离芯片区101的一侧电连接,所述第二端金属层112通过位于所述介质层118中的第一金属插塞117与相应的第一连接金属垫116连接,从而与相应的p型掺杂区105的远离所述芯片区101的一侧电连接。

51.在一些实施例中,所述控温区102中的所述珀尔帖器件104可以位于所述芯片区的一条边界一侧或者多条边界一侧,从而可以从一个方向或多个方向对芯片区进行控温。

52.在一些实施例中,所述控温区102中的所述珀尔帖器件104沿着所述芯片区101边界方向包围所述芯片区101,使得可以从芯片区101的四周对芯片区101进行横向的直接控温,能更好的控制芯片区101的温度。

53.在一些实施例中,所述半导体结构还包括保护环器件,所述保护环器件包括若干

层金属层和将相邻层的金属层连接的金属插塞,所述保护环器件设置于所述珀尔帖器件和所述半导体芯片之间,且围绕所述半导体芯片。

54.在一些实施例中,所述控温区102还可以作为保护环区,所述半导体结构还包括保护环器件,所述保护环器件包括若干层金属层和将相邻层的金属层连接的金属插塞,所述保护环器件设置于所述珀尔帖器件上,且围绕所述芯片区,在一个区域既能实现控温又能实现对芯片区的半导体芯片的保护。

55.所述保护环器件(seal ring,也称作密封环器件、防护环器件)为了防止半导体芯片受到切割工艺的损害及避免水气引发劣化的情形,还可以阻挡水气渗透或例如含酸物、含碱物等污染源的扩散的化学损害,起到保护半导芯片的作用。所述保护环器件呈多层结构,包括若干层金属层和将相邻层的金属层连接的金属插塞,以及将若干层金属层和相应的金属插塞隔离的介质层,所述介质层为多层结构。

56.本发明另一实施例还提供了一种半导体结构,本实施例与前述实施例的区别在于,所述第一端金属层位于第二端金属层上方,具体请参考图8-图11,图9为图8沿切割线ab方向的剖面结构示意图,图11为图10沿切割线ab方向的剖面结构示意图(需要说明的是,为了方便示意,图8中仅示出了第二端金属层112,未示出第一端金属层107,图10中仅示出了第一端金属层107,未示出第二端金属层112),所述第一端金属层107位于第二端金属层112(参考图11)上方,且所述第二端金属层112位于所述n型掺杂区106和p型掺杂区105远离芯片区101一侧的半导体衬底100中(参考图8和图9);所述半导体结构还包括介质层118(参考图11),所述第一端金属层107和第二端金属层112通过所述介质层118隔离。

57.在一些实施例中,参考图11,所述半导体结构还包括若干第二连接金属垫126和连接于每个所述第二连接金属垫126上表面的第二金属插塞127,所述第二连接金属垫126位于所述n型掺杂区106远离芯片区101一侧的半导体衬底100中且与所述n型掺杂区106远离芯片区101的一侧电连接,所述第一端金属层107通过位于所述介质层118中的第二金属插塞127与相应的第二连接金属垫126连接,从而与对应的n型掺杂区106的远离所述芯片区101的一侧电连接。

58.本发明又一实施例还提供了一种半导体结构,本实施例与前述实施例的区别在于,所述第三端金属层的具体结构不同,具体请参考图12和图13,所述第三端金属层包括若干依次间隔的第三端子金属层(111a、111b、111c),每一个第三端子金属层(111a、111b、111c)电连接于至少一对相邻的n型掺杂区106和p型掺杂区105。

59.本发明一些实施例中,还提供了一种半导体结构的形成方法,包括:

60.参考图1,提供半导体衬底100,所述半导体衬底100包括芯片区101和围绕芯片区101的控温区102。

61.在一些实施例中,所述半导体衬底100为晶圆,所述半导体衬底100包括若干呈行列排布的芯片区101,每一个芯片区100周围具有一个围绕该芯片区101的控温区102,所述控温区102之间为切割道区103。所述控温区102后续用于形成珀尔帖器件,所述芯片区101后续用于形成半导体芯片,所述切割道区103后续作为分割晶圆时的切割道。

62.参考图2,在所述控温区形成珀尔帖器件104,包括:

63.参考图3和图5,在位于所述控温区102的半导体衬底100中形成沿着所述芯片区101边界方向交替排布的若干n型掺杂区106和若干p型掺杂区105。

64.在一些实施例中,所述n型掺杂区和p型掺杂区通过离子注入工艺形成。具体的,向控温区102的半导体衬底100中的若干分立的第一区域注入n型杂质离子,形成若干n型掺杂区,向控温区102的半导体衬底100中的若干分立的第二区域注入p型杂质离子,形成若干p型掺杂区。所述离子注入注入的杂质离子为p型的杂质离子,所述p型的杂质离子为硼离子、镓离子或铟离子一种或几种。在另一些实施例中,所述n型掺杂区106和p型掺杂区105的形成过程还可以包括:在所述控温区102中形成凹槽;在所述凹槽中填充满碲化铋材料;对所述碲化铋材料进行掺杂,形成n型掺杂区106和p型掺杂区105。

65.参考图3和图6,形成位于所述n型掺杂区106和p型掺杂区105远离芯片区101一侧的第一端金属层107和第二端金属层112,所述第一端金属层107电连接于所述若干n型掺杂区106,所述第二端金属层112电连接于所述若干p型掺杂区105。

66.在一些实施例中,所述第一端金属层107位于所述第二端金属层112的下方,所述第一端金属层107和第二端金属层112的形成过程包括:在所述n型掺杂区106的远离所述芯片区的一侧半导体衬底中形成梳状的第二沟槽,所述第二沟槽暴露出所述若干n型掺杂区106的远离所述芯片区的一侧的侧壁表面;在每一个所述p型掺杂区105远离芯片的一侧半导体衬底中形成若干第三沟槽,每一个所述第三沟槽相应的暴露出一个所述p型掺杂区105远离芯片的一侧侧壁表面;在所述梳状的第二沟槽中填充金属形成第一端金属层107(参考图3和图4),在所述若干第三沟槽中填充金属,形成若干第一连接金属垫116(参考图3和图5);在所述半导体衬底100上形成介质层118(参考图7),所述介质层118中形成有与相应的第一连接金属垫116连接若干第一金属插塞117;在所述介质层118上形成与若干第一金属插塞117连接的第二端金属层112。

67.在另一些实施例中,参考图8-图11,所述第一端金属层107位于所述第二端金属层112的上方,所述第一端金属层107和第二端金属层112的形成过程包括:在所述p型掺杂区105的远离所述芯片区的一侧半导体衬底中形成梳状的第四沟槽,所述第四沟槽暴露出所述若干p型掺杂区105的远离所述芯片区的一侧的侧壁表面;在每一个所述n型掺杂区106远离芯片的一侧半导体衬底中形成若干第五沟槽,每一个所述第五沟槽相应的暴露出一个所述n型掺杂区106远离芯片的一侧侧壁表面;在所述梳状的第四沟槽中填充金属形成第二端金属层112(参考图8-图9),在所述若干第五沟槽中填充金属,形成若干第二连接金属垫126(参考图8);在所述半导体衬底100上形成介质层118(参考图11),所述介质层118中形成有与相应的第二连接金属垫126连接的若干第二金属插塞127;在所述介质层118上形成与若干第二金属插塞127连接的第一端金属层107。

68.参考图3和图4,形成位于所述n型掺杂区106和p型掺杂区105靠近芯片区101一侧的半导体衬底100中的第三端金属层111,所述第三端金属层111电连接于所述n型掺杂区106与p型掺杂区105。

69.在一些实施例中,所述第三端金属层111的形成过程包括:在所述n型掺杂区106和p型掺杂区105靠近芯片区101一侧的半导体衬底100中形成第一沟槽121,所述第一沟槽121暴露出所述n型掺杂区106和p型掺杂区105的靠近所述芯片区101的一侧侧壁表面;在所述第一沟槽121中填充金属形成第三端金属层111。

70.在一些实施例中,所述第三端金属层111与位于同层的第一端金属层107或第二端金属层112同步形成,具体的,当第一端金属层107位于第二端金属层112下层时,所述第三

端金属层111与第一端金属层107同步形成。当第二端金属层112位于第一端金属层107下层时,所述第三端金属层111与第二端金属层112同步形成。

71.在一些实施例中,还包括:在所述芯片区101形成半导体芯片,在所述珀尔帖器件和所述半导体芯片之间形成围绕所述半导体芯片的保护环器件,所述保护环器件包括若干层金属层和将相邻层的金属层连接的金属插塞。

72.在一些实施例中,所述珀尔帖器件与半导体芯片的制作工艺可以集成,比如,位于上层的第一端金属层107或第二端金属层112的形成工艺可以与制作半导体芯片时的底层金属线工艺同步进行,所述n型掺杂区106和p型掺杂区105形成工艺可以与半导体芯片中的相关的掺杂工艺同步进行,所述控温区形成沟槽的工艺可以与芯片区形成沟槽的工艺同步进行。

73.在一些实施例中,在珀尔帖器件与半导体芯片的制作完成后,可以沿切割道区域对晶圆进行切割,形成若干独立的芯片。

74.本技术虽然已以较佳实施例公开如上,但其并不是用来限定本技术,任何本领域技术人员在不脱离本技术的精神和范围内,都可以利用上述揭示的方法和技术内容对本技术技术方案做出可能的变动和修改,因此,凡是未脱离本技术技术方案的内容,依据本技术的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本技术技术方案的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1