一种免蚀刻制作LED芯片的方法及LED芯片与流程

一种免蚀刻制作led芯片的方法及led芯片

技术领域

1.本发明涉及led制作的技术领域,特别是涉及一种免蚀刻制作led芯片的方法及led芯片。

背景技术:

2.现有技术条件下,常规正装及倒装led制作电极均采用从p型半导体层往n型半导体层蚀刻,再镀金属的方式制作n型电极,如图1为正装led制作,制作n型电极需要先对外延层结构进行从p型半导体层往n型半导体层蚀刻,移除上述叠层结构的边缘部分,直至n型半导体层的边缘部分被暴露,一方面蚀刻工艺流程上相对较复杂、耗时,另一方面对外延层有蚀刻破坏,对led发光的损耗较大。

技术实现要素:

3.为解决上述技术问题,本发明提供一种优化n电极制作工艺的免蚀刻制作led芯片的方法,创新提出n型半导体层的定位手段,然后在定位位置的侧面制作n电极,省略了常规led芯片制作过程中的蚀刻工艺步骤,简化了操作流程,提高了工作效率。

4.为实现上述目的,本发明是采用下述技术方案实现的:

5.一方面,本发明提供一种免蚀刻制作led芯片的方法,包括以下操作步骤:

6.s1、在衬底的正面上依次生长n型半导体层、发光层、p型半导体层的外延层结构;

7.s2、在p型半导体层的上方制作p电极;

8.s3、根据所述步骤s1中生长的外延层结构确定n型半导体层的厚度为x,n型半导体层的底部到p型半导体层的顶部的厚度为y,发光层和p型半导体层的总厚度为z,则n电极的位置设置在距p型半导体层的顶部y-z~y范围内;

9.s4、在步骤s3中确定的n电极的位置范围内的侧面制作n电极。

10.一种可能的技术方案中,所述衬底的材料选自蓝宝石、碳化硅、硅、氮化镓、zno、氮化铝和尖晶石中的任意一种。

11.一种可能的技术方案中,所述外延层采用有机金属化学气相沉积法、分子束外延法或氢化物气相外延法进行层叠。

12.一种可能的技术方案中,所述p电极和n电极采用溅射法或蒸镀法制作。

13.一种可能的技术方案中,所述发光层为单量子阱结构或多量子阱结构、量子点结构或量子线结构。

14.一种可能的技术方案中,所述n电极为cr/al/ti或其他结构的电极。

15.一种可能的技术方案中,所述步骤s4中侧面制作n电极包括以下步骤:

16.s41、将制作好p电极的外延层结构划裂成芯粒;

17.s42、将芯粒侧立固定后在y-z~y区域内制作n电极。

18.一种可能的技术方案中,所述步骤s41中将外延层结构划裂成bar条状芯粒。

19.另一方面,本发明提供一种led芯片,采用任一项上述的免蚀刻制作led芯片的方

法制得。

20.与现有技术相比本发明的有益效果为:本发明针对现有技术中led制作所必需的繁琐的蚀刻工序进行改进,创新性提出一种n型半导体层的定位手段,定位方法根据外延层结构生长情况进行物理测量厚度,测量方法简单,定位方式准确高效;完成n型半导体层的定位步骤后,对定位位置的侧面制作n电极,本发明的制作led芯片的方法整体过程能够避免常规led芯片制作过程中的蚀刻工艺步骤,防止蚀刻对外延层的破坏,简化了操作流程,提高了工作效率,减少了led发光的损耗,降低了led制作成本,有利于行业内推广应用。

附图说明

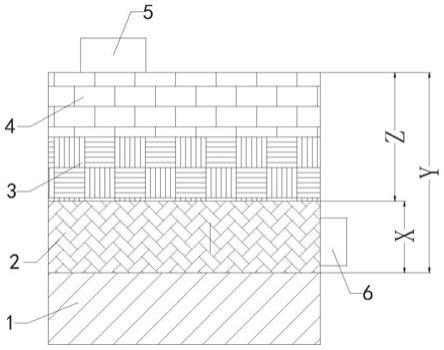

21.图1是现有技术led芯片结构示意图;

22.图2是本发明的免蚀刻制作led芯片的方法的结构示意图;

23.图3是外延层结构划裂成bar条状芯粒结构示意图;

24.附图标记:1-衬底;2-n型半导体层;3-发光层;4-p型半导体层;5-p电极;6-n电极;7-芯粒。

具体实施方式

25.下面结合附图和实施例,对本发明的具体实施方式作进一步详细描述。以下实施例用于说明本发明,但不用来限制本发明的范围。

26.实施例1

27.如图2所示,本发明实施例1免蚀刻制作led芯片的方法,包括以下操作步骤:

28.s1、在衬底1的正面上依次生长n型半导体层2、发光层3、p型半导体层4的外延层结构;

29.其中,衬底1的材料选自蓝宝石、碳化硅、硅、氮化镓、zno、氮化铝和尖晶石中的任意一种;外延层采用有机金属化学气相沉积法(mocvd法)、分子束外延法(mbe法)或氢化物气相外延法(hvpe法)进行层叠;例如,采用有机金属化学气相沉积法,将衬底1放入有机化学气相沉积炉,通入iii族金属元素的烷基化合物蒸汽与非金属的氢化物气体,在高温下通过热解反应,生成iii-v族化合物,通过沉积依次在衬底1的正面上生长n型半导体层2、发光层3、p型半导体层4的叠层结构。n型半导体层2和p型半导体层4为iii-v族化合物半导体材料,至少包括alxgayin(1-x-y)n或alxgayin(1-x-y)p,其中,0≤x≤1,0≤y≤1,且0≤x+y≤1,例如,化合物半导体可含有gan、aln、algan、gainn、inn、algainn、gap、alp、algap、gainp、inp、及algainp中的任意一种;发光层为单量子阱结构或多量子阱结构、量子点结构或量子线结构。

30.s2、在p型半导体层4的上方制作p电极5;p电极5采用溅射法或蒸镀法制作;

31.s3、根据所述步骤s1中生长的外延层结构确定n型半导体层2的厚度为x,n型半导体层2的底部到p型半导体层4的顶部的厚度为y,发光层3和p型半导体层4的总厚度为z,则n电极6的位置设置在距p型半导体层4的顶部y-z~y范围内;

32.例如,n型半导体层2的厚度为2.5um,发光层3和p型半导体层4的总厚度为0.5um,n型半导体层2的底部到p型半导体层4的顶部的厚度为3um,则n电极6的位置设置在距p型半导体层4的顶部0.5-3um范围内;用此方式可以快速通过物理测量厚度的方式进行n型半导

体层2的定位。

33.s4、在步骤s3中确定的n电极6的位置范围内的侧面溅射法或蒸镀法制作n电极6,制作完成后经过研磨、划裂成芯粒7,再将芯粒7逐一裂开成单颗led;优选地,n电极采用蒸镀法制作,并通过liff-off工艺获得;n电极可以为cr/al/ti或其他结构的电极。

34.本发明针对现有技术中led制作所必需的繁琐的蚀刻工序进行改进,创新性提出一种n型半导体层的定位手段,定位方法根据外延层结构生长情况进行物理测量厚度,测量方法简单,定位方式准确高效;完成n型半导体层的定位步骤后,对定位位置的侧面制作n电极,n电极在定位位置侧面全部或者局部制作均可实现本发明;本发明的制作led芯片的方法整体过程能够避免常规led芯片制作过程中的蚀刻工艺步骤,防止蚀刻对外延层的破坏,简化了操作流程,提高了工作效率,减少了led发光的损耗,降低了led制作成本,有利于行业内推广应用。

35.实施例2

36.本发明实施例2免蚀刻制作led芯片的方法,包括以下操作步骤:

37.s1、在衬底1的正面上依次生长n型半导体层2、发光层3、p型半导体层4的外延层结构;其中,衬底1的材料采用氮化铝,外延层采用有机金属化学气相沉积法(mocvd法)进行层叠;

38.s2、在p型半导体层4的上方制作p电极5;p电极5采用蒸镀法制作;

39.s3、根据所述步骤s1中生长的外延层结构确定n型半导体层2的厚度为4.5um,n型半导体层2的底部到p型半导体层4的顶部的厚度为5.3um,发光层3和p型半导体层4的总厚度为0.8um,则n电极6的位置设置在距p型半导体层4的顶部0.8~5.3um范围内;

40.s4、在步骤s3中确定的n电极6的位置范围内的侧面制作n电极6:如图3所示,s41、将制作好p电极5的外延层结构划裂成bar条状芯粒7;

41.s42、将芯粒7侧立固定后在0.8~5.3um区域内制作蒸镀法,并通过liff-off工艺获得n电极6;n电极6可以为cr/al/ti或其他结构的电极;然后将芯粒7逐一裂开成单颗led。

42.实施例3

43.一种led芯片,是采用本发明实施例2免蚀刻制作led芯片的方法制得。

44.本发明上述实施例还具体进行生产时,还包括其它工艺优化步骤,如清洗步骤、检测步骤、焊线步骤以及划片步骤等,但这些步骤均属于led芯片生产领域的公知常识,此外,本文中对于未具体展开的制作方法同样属于led芯片生产领域的公知常识和常规技术手段,因此本文均不再做具体展开说明。

45.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明技术原理的前提下,还可以做出若干改进和变型,这些改进和变型也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1