一种碳化硅单晶衬底、制备方法及半导体器件与流程

1.本发明涉及碳化硅单晶制造技术领域,特别涉及一种碳化硅单晶衬底、 制备方法及半导体器件。

背景技术:

2.随着半导体技术的不断革新,第三代宽禁带材料中的碳化硅(sic)由于 自身材料优良特性和碳化硅器件呈现出的巨大应用前景而得到飞速发展,碳 化硅晶体的制备以及相关器件的研究一直是国内外的前沿研究热点。碳化硅 单晶因具备禁带宽度大、击穿电场高、热导率大、电子饱和漂移速率快、化 学稳定性高、抗辐射能力强等各种优越性能,成为耐高温、高频、抗辐射、 大功率半导体器件材料的优先选择。

3.位错是碳化硅单晶衬底的主要缺陷之一,位错对于以碳化硅单晶为基底 的半导体器件的性能有着显著影响。目前市面上以碳化硅单晶为基底的半导 体器件位错密度仍然较高,近年来随着技术进步,位错密度在逐步降低,但 仍然不能显著提高半导体器件的良品率。

4.因此,如何提高半导体器件的良品率,是本领域技术人员亟需解决的技 术问题。

技术实现要素:

5.有鉴于此,本发明的目的在于提供一种碳化硅单晶衬底,以提高使用此 碳化硅单晶衬底制作的半导体器件的良品率。

6.本发明的另一目的在于提供一种上述碳化硅单晶衬底的制备方法。

7.本发明的另一目的在于提供一种使用上述碳化硅单晶衬底制作的半导体 器件。

8.为实现上述目的,本发明提供如下技术方案:

9.一种碳化硅单晶衬底,包括第一表面和第二表面,所述第一表面包括钉 扎区和制件区,所述钉扎区为人工设置的势阱,以将所述钉扎区周围区域的 位错集中于所述钉扎区,所述第一表面上设置多个所述钉扎区;

10.所述制件区用于制作包含所述碳化硅单晶衬底的半导体器件,所述制件 区周围设置有所述钉扎区,以使得所述制件区中心区域的位错密度小于边缘 区域。

11.优选地,在上述碳化硅单晶衬底中,多个所述钉扎区均匀设置于所述第 一表面上,所述制件区周围均匀设置有多个所述钉扎区。

12.优选地,在上述碳化硅单晶衬底中,所述钉扎区为边长为40μm~100μm的 正方形,所述制件区为矩形区域且所述制件区的四个顶点上均设置有所述钉 扎区。

13.优选地,在上述碳化硅单晶衬底中,所述制件区为正方形区域。

14.优选地,在上述碳化硅单晶衬底中,所述制件区可以制作单个半导体器 件,也可以制作多个半导体器件。

15.优选地,在上述碳化硅单晶衬底中,所述制件区的位错密度小于3000个 /cm2。

16.优选地,在上述碳化硅单晶衬底中,所述制件区的螺型位错密度小于500 个/cm2。

17.优选地,在上述碳化硅单晶衬底中,所述制件区的刃型位错密度小于1500 个/cm2。

18.优选地,在上述碳化硅单晶衬底中,所述制件区的基平面位错密度小于 1000个/cm2。

19.本发明还提供了一种碳化硅单晶衬底的制备方法,所述制备方法用于制 备如权利要求1-9任一项所述的碳化硅单晶衬底,所述制备方法包括以下步骤:

20.加工籽晶生长面:确定好所需碳化硅单晶衬底的钉扎区形状及分布,在 籽晶的生长面上按照钉扎区的形状制作图形;

21.退火:将加工后的籽晶在惰性气体的保护下进行第一预设温度下的退火 处理,处理时间为第一预设时长;

22.生长碳化硅单晶:将退火处理后的籽晶装炉,并使用传统物理气相传输 法进行碳化硅单晶的生长;

23.切割碳化硅单晶:使用多线切割工艺将生长完成后的碳化硅单晶加工为 所需厚度的晶片;

24.研磨抛光:对加工后的碳化硅单晶晶片进行研磨、抛光及清洗,即获得 如权利要求1-9任一项所述的碳化硅单晶衬底。

25.优选地,在上述碳化硅单晶衬底的制备方法中,在加工籽晶生长面步骤 中,在籽晶生长面上制作图形的方法为涂抹、蒸镀、磁控溅射镀、浸润和粘 贴中的一种或多种。

26.优选地,在上述碳化硅单晶衬底的制备方法中,在加工籽晶生长面步骤 中,在籽晶生长面上制作图形的材质为石墨。

27.优选地,在上述碳化硅单晶衬底的制备方法中,在加工籽晶生长面步骤 中,在籽晶生长面上制作图形的材质为铌、铼、锇、钽、钼、钨和铱中的一 种或多种。

28.优选地,在上述碳化硅单晶衬底的制备方法中,在加工籽晶生长面步骤 中,在籽晶生长面上制作图形的材质为碳化铌、碳化铼、碳化锇、碳化钽、 碳化钼、碳化钨和碳化铱中的一种或多种。

29.优选地,在上述碳化硅单晶衬底的制备方法中,在退火步骤中,所述第 一预设温度为800℃~1000℃,所述第一预设时长为20min~40min。

30.优选地,在上述碳化硅单晶衬底的制备方法中,在退火步骤中,所述惰 性气体为氩气。

31.本发明还提供了一种半导体器件,所述半导体器件为使用如权利要求1-9 任一项所述的碳化硅单晶衬底生产的半导体器件。

32.优选地,在上述半导体器件中,所述半导体器件的有效区域使用所述制 件区中心区域的所述碳化硅单晶衬底进行生产,所述有效区域为所述半导体 器件上施加电压的区域。

33.从上述的技术方案可以看出,本发明提供的碳化硅单晶衬底,与现有技 术的区别在于,在碳化硅单晶衬底的第一表面上人工设置钉扎区,以通过钉 扎区的势阱,将钉扎区周围区域的位错集中于钉扎区,在第一表面上设置多 个钉扎区;在第一表面上还设置有制件区,制件区用于制作包含碳化硅单晶 衬底的半导体器件,制件区周围设置有钉扎区,以使得制件区中心区域的位 错密度小于边缘区域。通过人工设置钉扎区,并将钉扎区设置于

制件区的周 围,可以使制件区上的位错集中在制件区周围,从而降低制件区中心区域的 位错密度,并使用制件区上低位错密度的区域来制作半导体器件上施加电压 的区域,即半导体器件的有效区域,可以显著降低有效区域的位错密度,从 而使得有效区域在受电压影响时失效概率降低,从而提高半导体器件的良品 率。

附图说明

34.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实 施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面 描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲, 在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

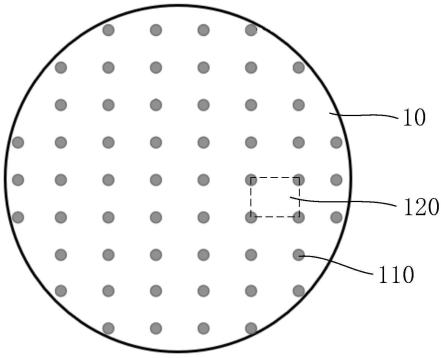

35.图1为本发明实施例提供的圆形钉扎区示意图;

36.图2为本发明实施例提供的单向条带形钉扎区示意图;

37.图3为本发明实施例提供的双向条带形钉扎区示意图;

38.图4为本发明实施例提供的碳化硅单晶衬底的制备方法流程图;

39.其中,10为第一表面,110为钉扎区,120为制件区。

具体实施方式

40.本发明的核心在于提供一种碳化硅单晶衬底,以提高使用此碳化硅单晶 衬底制作的半导体器件的良品率。

41.本发明的另一核心在于提供一种用于制备上述碳化硅单晶衬底的制备方 法。

42.本发明的另一核心在于提供一种使用上述碳化硅单晶衬底制作的半导体 器件。

43.为了使本技术领域的人员更好地理解本发明方案,下面参照附图对本发 明实施例进行说明。此外,下面所示的实施例不对权利要求所记载的发明内 容起任何限定作用。另外,下面实施例所表示的全部内容不限于作为权利要 求所记载的发明的解决方案所必需的。

44.在现有的碳化硅单晶衬底中,位错是碳化硅单晶衬底的主要缺陷之一, 且对使用碳化硅单晶衬底制作的半导体器件的性能有显著影响。现有技术在 逐步降低碳化硅单晶衬底上的位错密度,但半导体器件的良品率仍不能获得 显著提升。

45.发明人通过对半导体器件失效与碳化硅单晶衬底位错的相关性研究发 现,在半导体器件上,位错密度高的区域不一定失效,位错密度低的区域也 可能失效,半导体器件的失效原因除了与位错的平均密度有关外,还与位错 分布的位置有关。半导体器件上施加电压的区域为半导体器件的有效区域, 经发明人研究发现,在半导体器件上的有效区域位置的性能对位错更为敏感, 而远离有效区域的位置的性能对位错就不太敏感,单方面降低半导体器件上 整体位错密度并不能显著提高半导体器件的良品率,而控制位错分布位置则 可以提高半导体器件的良品率。

46.关于如何控制碳化硅单晶衬底上的位错分布,发明人经过巧妙思考,克 服了碳化硅单晶衬底上的位错均需要进行消除的技术偏见,而是通过人工在 碳化硅单晶衬底上设置钉扎区110,来控制碳化硅单晶衬底上的位错分布位 置。具体细节,请见下文具体实施的方式。

47.参见图1,本发明实施例公开了一种碳化硅单晶衬底,包括第一表面10和 第二表面,其中,第一表面10是用于制作半导体器件的碳化硅单晶衬底表面, 第二表面为固定面,以将碳化硅单晶衬底固定在加工设备上。第一表面10上 包括钉扎区110和制件区120,其中,钉扎区110为人工设置的势阱,即位错在 热驱动力下在碳化硅单晶衬底内部移动,当移动到钉扎区110附近时,位错线 不易继续运动而会被集中吸引在钉扎区110,在第一表面10上设置有多个钉扎 区110;制件区120是用于制作包含碳化硅单晶衬底的半导体器件的区域,制 件区120的周围人工设置有钉扎区110,以使得制件区120的周围吸引位错,进 而降低制件区120中心区域的位错密度,制件区120的中心区域即为低位错密 度的碳化硅单晶衬底,使用制件区120的中心区域的碳化硅单晶衬底制作半导 体器件上施加电压的区域,即半导体器件的有效区域,可以显著减低半导体 器件上有效区域的位错密度,降低有效区域失效的概率,从而提升半导体器 件的良品率。

48.本发明提供的碳化硅单晶衬底,在碳化硅单晶衬底的第一表面10上设置 钉扎区110和制件区120,通过人工设置势阱的方式将位错集中于钉扎区110, 需要说明的是,势阱可以使得势阱周围区域的位错在一定的热驱动力的作用 下运动至势阱区域,并集中于势阱处难以逃离势阱,从而将位错集中于设置 势阱的位置,同时将钉扎区110设置于制件区120的周围,以将制件区120上的 位错集中在制件区120的周围区域,在位错总量一定的情况下,制件区120中 心区域的位错密度显著降低,使用制件区120中心区域的碳化硅单晶衬底制作 半导体器件上施加电压的区域,即半导体器件的有效区域,可以降低有效区 域的位错密度,从而使得有效区域的失效概率降低,半导体器件的良品率显 著提升。

49.进一步地,参见图1,图2及图3,在本发明提供的碳化硅单晶衬底中,钉 扎区110可以为任意形状,且多个钉扎区110均匀设置于第一表面10上,均匀 设置即任意方向上相邻两个钉扎区110的距离相同。在制件区120的周围均匀 设置多个钉扎区110,以将制件区120上的位错均匀分布至制件区120的周围区 域,从而降低制件区120中心区域的位错密度。制件区120的一条边可以经过 单个钉扎区110,也可以经过多个钉扎区110。

50.需要说明的是,钉扎区110可以为矩形、正方形、圆形、三角形或条带形, 多个钉扎区110阵列设置。

51.进一步地,在本发明一具体实施例中,钉扎区110为正方形,钉扎区110 的边长为40μm~100μm的正方形,在这里优选钉扎区110的边长为60μm,钉扎 区110在第一表面10上的水平方向和竖直方向分布,钉扎区110均匀布满第一 表面10;制件区120为矩形区域,且矩形区域制件区120的四个顶点上均设置 有一个钉扎区110。

52.需要说明的是,制件区120可以充满四个钉扎区110围成的区域,也可以 小于四个钉扎区110围成的区域,仅需保证制件区120的中心区域位于四个钉 扎区110围成区域的中心位置,即可实现制件区120中心区域的位错密度小于 周围区域,在这里优选制件区120充满四个钉扎区110围成的区域。

53.参见图2,在本发明另一具体实施例中,钉扎区110为在第一表面10上竖 直方向均匀分布的条带形,相邻条带形钉扎区110间的区域即为制件区120, 制件区120的位错集中分布于上下端的条带形钉扎区110,以使得制件区120中 心区域的位错密度低于上下端靠近钉扎区110的区域。

54.需要说明的是,钉扎区110也可以为在第一表面10上水平方向或预设角度 方向均

匀分布的条带形,制件区120即为相邻两个条带形钉扎区110的中间区 域,该预设角度由加工人员根据加工需要确定。

55.为了进一步优化上述技术方案,本发明提供的碳化硅单晶衬底中,制件 区120为正方形区域,即水平方向和竖直方向上相邻的两个钉扎区110的距离 相等,相较于矩形区域的制件区120,正方形区域的制件区120的分布更为均 匀。

56.进一步地,本发明提供的碳化硅单晶衬底中,制件区120可以制作单个半 导体器件,也可以制作多个半导体器件。

57.进一步地,在本发明一具体实施例中,制件区120的位错密度小于3000个 /cm2,优选小于1500个/cm2,更优选小于600个/cm2。

58.需要说明的是,制件区120的位错类型包含螺型位错、刃型位错和基平面 位错,在此处优选三种位错密度的总和小于800个/cm2。

59.进一步地,在本发明另一具体实施例中,制件区120的螺型位错密度小于 500个/cm2,优选小于200个/cm2,更优选小于100个/cm2。

60.进一步地,在本发明另一具体实施例中,制件区120的刃型位错密度小于 1500个/cm2,优选小于800个/cm2,更优选小于300个/cm2。

61.进一步地,在本发明另一具体实施例中,制件区120的基平面位错密度小 于1000个/cm2,优选小于500个/cm2,更优选小于200个/cm2。

62.本发明还提供了一种碳化硅单晶衬底的制备方法,该制备方法用于制备 上述任一实施例提供的碳化硅单晶衬底,参见图4,该碳化硅单晶衬底的制备 方法包括以下步骤:

63.s01:在籽晶生长面制作钉扎区的图形并退火;

64.s02:使用物理气相传输法进行碳化硅单晶的生长;

65.s03:切割碳化硅单晶并研磨抛光。

66.在步骤s01中,先确定所需的碳化硅单晶衬底的钉扎区110形状及分布状 态,在籽晶的生长面上按照钉扎区110的形状制作图形,并对加工后的籽晶进 行退火处理,退火处理为将制作图形后的籽晶在惰性气体的保护下,曝露于 第一预设温度下并放置第一预设时长,之后进行缓慢冷却的热处理方式。需 要说明的是,退火处理的目的是使图形与籽晶结合更牢固。

67.在步骤s02中,使用步骤s01中加工完成后的籽晶进行碳化硅单晶的生长, 生长得到的碳化硅单晶为包含钉扎区110的晶体。

68.在步骤s03中,使用多线切割工艺将生长完成后的碳化硅单晶加工为所需 厚度的晶片,并进行研磨、抛光及清洗的加工过程,获得上述任一实施例提 供的碳化硅单晶衬底。

69.为了进一步优化上述技术方案,在步骤s01中,在籽晶生长面上制作图形 的方法为涂抹、蒸镀、磁控溅射镀、浸润和粘贴中的一种或多种,在此处优 选使用磁控溅射镀的方式进行籽晶生长面上图形的制作。需要说明的是,涂 抹、蒸镀、磁控溅射镀、浸润和粘贴的处理方式与现有技术相同,在此不再 赘述。

70.进一步地,在本发明一具体实施例中,在步骤s01中,在籽晶生长面上制 作图形的材质为石墨,石墨材质的图形耐高温,且与碳化硅晶体中的元素重 合,不会引入新的杂质。

71.进一步地,在本发明另一具体实施例中,在步骤s01中,在籽晶生长面上 制作图形的材质为铌、铼、锇、钽、钼、钨和铱中的一种或多种。

72.进一步地,在本发明另一具体实施例中,在步骤s01中,在籽晶生长面上 制作图形的材质为碳化铌、碳化铼、碳化锇、碳化钽、碳化钼、碳化钨和碳 化铱中的一种或多种。

73.进一步地,在本发明另一具体实施例中,在步骤s01中,在籽晶生长面上 制作图形的材质为难熔金属或难熔金属碳化物中的一种或多种。

74.为了进一步优化上述技术方案,在步骤s01中,退火过程的第一预设温度 为800℃~1000℃,在这里优选退火过程的第一预设温度为900℃;第一预设时 长为20min~40min,在这里优选第一预设时长为30min。

75.进一步地,在本发明一具体实施例中,在步骤s01的退火过程中,通入的 惰性气体为氩气。

76.本发明还提供了一种半导体器件,该半导体器件为使用上述任意实施例 提供的碳化硅单晶衬底进行生产的半导体器件。

77.进一步地,本发明提供的半导体器件的有效区域使用制件区120中心区域 的碳化硅单晶衬底进行生产,可以保证半导体器件有效区域的位错密度小于 半导体器件上的其他位置,从而降低半导体器件的失效概率,提高半导体器 件的良品率。

78.为了更为清楚地理解本发明提供的碳化硅单晶衬底的制备方法及本发明 提供的半导体器件的良品率提升,下面以一个具体实施例进行详细说明,实 施例如下:

79.根据本发明提供的碳化硅单晶衬底的制备方法进行碳化硅单晶衬底的制 备,在本发明的一个具体实施例中,选用一片4度6英寸sic(碳化硅)籽晶进 行碳化硅单晶衬底的制备,碳化硅单晶衬底的制备方法的具体步骤为依次进 行的以下过程:

80.步骤i:在籽晶的生长面上制作钉扎区110的图形,用石墨纸做掩膜进行籽 晶生长面上图形的制作,在籽晶的生长面上用磁控溅射镀的方式镀上一层矩 阵型排布的碳膜材质的钉扎区110,每个钉扎区110为直径50μm的圆形,每两 个相邻钉扎区110的距离为2.4mm,钉扎区110图形均匀分布于籽晶的生长面 上;

81.步骤ii:进行籽晶的退火处理,将制作完成图形后的籽晶在氩气保护下进 行900℃下的退火处理30min;

82.步骤iv:将退火完成后的籽晶使用传统的物理气相传输法(pvt法)进 行碳化硅单晶的生长,需要说明的是,具体生长过程即物理气相传输法(pvt 法)与现有技术相同,在此不再赘述;

83.步骤v:将获得的碳化硅单晶使用多线切割的方式加工成6英寸350μm厚 的碳化硅晶片,进行koh(氢氧化钾)腐蚀,并检测位错的分布情况,发现 在籽晶的钉扎区110的位错密度为9552个/cm2,籽晶的制件区120的位错密度为 2360个/cm2。

84.使用现有技术的方法进行碳化硅单晶的生长,即不进行在籽晶生长面制 作图形的步骤,直接将4度6英寸sic(碳化硅)籽晶装配于坩埚的顶部,使用 物理气相传输法(pvt法)进行碳化硅单晶的生长,得到6英寸的碳化硅晶体, 同样使用多线切割的方式将6英寸的碳化硅晶体切割成6英寸350μm厚的碳化 硅晶片,进行koh(氢氧化钾)腐蚀,并检测位错的分布情况,发现位错基 本均匀分布,平均位错密度为6385个/cm2。

85.通过对比可以看出,使用本发明提供的碳化硅单晶衬底的制备方法,得 到的碳化硅单晶衬底上,制件区120中心区域的位错密度显著低于制件区120 周围区域的位错密度,同时显著低于现有技术中碳化硅单晶衬底表面上的位 错密度,通过实施例可以看出,本发

明提供的碳化硅单晶衬底的制备方法实 现了控制碳化硅单晶衬底上位错分布位置的目的。

86.为了更清楚的理解本发明提供的半导体器件的良品率提升,下面将以两 组半导体器件的实施例进行详细说明:

87.第一组:用本发明提供的碳化硅单晶衬底10片进行半导体器件的制作, 同批次半导体器件单个尺寸均为2.4mm

×

2.4mm,与单个制件区120的尺寸相 同,半导体器件的有效区域为制件区120的中心位置,得到半导体产品10片;

88.第二组:用本发明提供的碳化硅单晶衬底10片进行半导体器件的制作, 同批次半导体器件单个尺寸均为2.4mm

×

2.4mm,单个制件区120可以制作4个 器件,即单个制件区120包含四个钉扎区110,半导体器件按矩阵分布在制件 区120的中心位置,得到半导体产品10片;

89.第三组:使用现有技术制备的碳化硅单晶衬底10片,进行半导体器件的 制作,同批次半导体器件单个尺寸均为2.4mm

×

2.4mm。

90.结果显示,第一组中的半导体器件良品率比第三组中的半导体器件良品 率提高26%,第二组中的半导体器件良品率比第三组中的半导体器件良品率 提高18%,该实施例表明本发明提供的半导体器件可以显著提高良品率,与 现有技术比有极大技术优势和显著的经济价值。

91.本发明的说明书和权利要求书及上述附图中的术语“第一”和“第二

”ꢀ

等是用于区别不同的对象,而不是用于描述特定的顺序。此外术语“包括

”ꢀ

和“具有”以及他们任何变形,意图在于覆盖不排他的包含。例如包含了一 系列步骤或单元的过程、方法、系统、产品或设备没有设定于已列出的步骤 或单元,而是可包括没有列出的步骤或单元。

92.对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用 本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易 见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下, 在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例, 而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1