半导体装置以及半导体装置的制造方法与流程

1.本公开涉及半导体装置以及半导体装置的制造方法。

背景技术:

2.作为具备高电子迁移率晶体管(high electron mobility transistor:hemt)的半导体装置,提出了具有栅电极的半导体装置,该栅电极具备基部和从基部向侧方伸出的檐部(专利文献1)。

3.现有技术文献

4.专利文献

5.专利文献1:美国专利第8741715号说明书

6.专利文献2:日本特开2013-207086号公报

7.专利文献3:日本特开2019-216188号公报

8.在以往的半导体装置中,栅电极的特性有时会发生变化。

技术实现要素:

9.本公开的目的在于提供能抑制栅电极的特性的变化的半导体装置以及半导体装置的制造方法。

10.本公开的半导体装置具有:半导体层;绝缘膜,设于所述半导体层之上,形成有开口;栅电极,经由所述开口连接于所述半导体层;以及保护膜,覆盖所述栅电极,所述绝缘膜具有:所述半导体层侧的第一面;以及与所述第一面相反侧的第二面,所述栅电极具有:第三面,离开所述第二面并与所述第二面对置;以及第四面,将所述第二面与所述第三面相连,所述栅电极包含构成所述第三面和所述第四面的ni膜,在所述第三面和所述第四面具有覆盖所述ni膜的ni氧化膜,所述保护膜从所述ni氧化膜之上覆盖所述第三面和所述第四面。

11.发明效果

12.根据本公开,能抑制栅电极的特性的变化。

附图说明

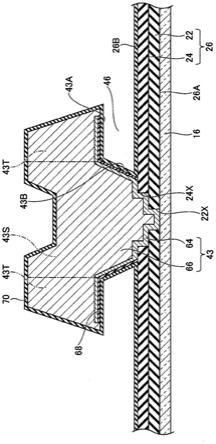

13.图1是表示实施方式的半导体装置的概要的剖视图。

14.图2是表示实施方式的半导体装置中的栅电极及其周边的详情的剖视图。

15.图3是表示实施方式的半导体装置的制造方法的剖视图(其1)。

16.图4是表示实施方式的半导体装置的制造方法的剖视图(其2)。

17.图5是表示实施方式的半导体装置的制造方法的剖视图(其3)。

18.图6是表示实施方式的半导体装置的制造方法的剖视图(其4)。

19.图7是表示实施方式的半导体装置的制造方法的剖视图(其5)。

20.图8是表示实施方式的半导体装置的制造方法的剖视图(其6)。

21.图9是表示实施方式的半导体装置的制造方法的剖视图(其7)。

22.图10是表示实施方式的半导体装置的制造方法的剖视图(其8)。

23.图11是表示实施方式的半导体装置的制造方法的剖视图(其9)。

24.图12是表示实施方式的半导体装置的制造方法的剖视图(其10)。

25.图13是表示实施方式的半导体装置的制造方法的剖视图(其11)。

26.图14是表示实施方式的半导体装置的制造方法的剖视图(其12)。

27.图15是表示实施方式的半导体装置的制造方法的剖视图(其13)。

28.图16是表示实施方式的半导体装置的制造方法的剖视图(其14)。

29.附图标记说明

30.10:基板

31.12:电子渡越层

32.14:电子供给层

33.16:帽层

34.20:层叠结构

35.22:第一绝缘膜

36.22x:开口

37.24:第二绝缘膜

38.24x:开口

39.26:绝缘膜

40.26a:第一面

41.26b:第二面

42.31、32:开口

43.41:源电极

44.42:漏电极

45.43:栅电极

46.43a:第三面

47.43b:第四面

48.43s:基部

49.43t:檐部

50.46:空隙

51.51、52、53、54、55:电子束抗蚀剂

52.51x、52x、53x、54x、55x:开口

53.61、62:金属层

54.64:ni膜

55.66:au膜

56.68:ni氧化膜

57.70:保护膜

58.100:半导体装置。

具体实施方式

59.以下,对用于实施的方式进行说明。

60.[本公开的实施方式的说明]

[0061]

首先,列举本公开的实施方案来进行说明。在以下的说明中,对相同或对应的要素标注相同的附图标记,对它们不反复进行相同的说明。

[0062]

〔1〕本公开的一个方案的半导体装置具有:半导体层;绝缘膜,设于所述半导体层之上,形成有开口;栅电极,经由所述开口连接于所述半导体层;以及保护膜,覆盖所述栅电极,所述绝缘膜具有:所述半导体层侧的第一面;以及与所述第一面相反侧的第二面,所述栅电极具有:第三面,离开所述第二面并与所述第二面对置;以及第四面,将所述第二面与所述第三面相连,所述栅电极包含构成所述第三面和所述第四面的ni膜,在所述第三面和所述第四面具有覆盖所述ni膜的ni氧化膜,所述保护膜从所述ni氧化膜之上覆盖所述第三面和所述第四面。

[0063]

在ni膜露出于栅电极的表面并且ni膜被通过化学气相沉积(chemical vapor deposition:cvd)法形成为保护膜的si氮化膜覆盖的情况下,ni会扩散至保护膜中,栅电极的特性有时会发生变化。此外,在ni膜被通过原子层沉积(atomic layer deposition:ald)法形成为保护膜的al氧化膜覆盖的情况下,ni会在保护膜与ni膜的界面扩散,栅电极的特性有时会发生变化。相对于此,在本公开的一个方案的半导体装置中,在第三面和第四面,ni膜被ni氧化膜覆盖,保护膜从ni氧化膜之上覆盖第三面和第四面。因此,能抑制ni膜中的ni的扩散,从而抑制栅电极的特性的变化。

[0064]

〔2〕在〔1〕中,也可以是,在所述保护膜的覆盖所述第三面的部分与所述第二面之间存在空隙。在该情况下,易于减小栅电极与层叠结构之间的寄生电容。

[0065]

〔3〕在〔1〕或〔2〕中,也可以是,所述保护膜包含al氧化膜或si氮化膜。在该情况下,易于保护栅电极免受来自外部的水分的侵入等。

[0066]

〔4〕在〔1〕~〔3〕中,也可以是,所述ni氧化膜的厚度为3nm以上。在该情况下,更易于抑制ni膜中的ni的扩散。

[0067]

〔5〕在〔1〕~〔4〕中,也可以是,所述保护膜还覆盖所述绝缘膜。在该情况下,能更牢固地保护层叠结构。

[0068]

〔6〕在〔1〕~〔5〕中,也可以是,所述ni膜的与所述绝缘膜接触的部分的面积为所述ni膜的与所述ni氧化膜接触的部分的面积的0.10倍以下。在该情况下,更易于抑制ni膜的与绝缘膜接触的部分处的ni的扩散。

[0069]

〔7〕本公开的另一个方案的半导体装置具有:半导体层;绝缘膜,设于所述半导体层之上,形成有开口;栅电极,经由所述开口连接于所述半导体层;以及保护膜,包含覆盖所述栅电极和所述绝缘膜的al氧化膜或si氮化膜,所述绝缘膜具有:所述半导体层侧的第一面;以及与所述第一面相反侧的第二面,所述栅电极具有:第三面,离开所述第二面并与所述第二面对置;以及第四面,将所述第二面与所述第三面相连,所述栅电极包含:ni膜,构成所述第三面和所述第四面;以及au膜,形成于所述ni膜之上,在所述第三面和所述第四面具有覆盖所述ni膜的ni氧化膜,所述保护膜从所述ni氧化膜之上覆盖所述第三面和所述第四面,在所述保护膜的覆盖所述第三面的部分与所述第二面之间存在空隙。

[0070]

〔8〕本公开的另一个方案的半导体装置的制造方法具有以下工序:在半导体层之

上形成绝缘膜,所述绝缘膜具有所述半导体层侧的第一面和与所述第一面相反侧的第二面;在所述绝缘膜形成开口;形成金属层,所述金属层经由所述开口连接于所述半导体层,所述金属层具有第三面和第四面,所述第三面离开所述第二面并与所述第二面对置,所述第四面将所述第二面与所述第三面相连,所述金属层包含构成所述第三面和所述第四面的ni膜;通过使所述ni膜氧化而在所述第三面和所述第四面形成覆盖所述ni膜的ni氧化膜,由所述金属层的剩余部分形成栅电极;以及形成保护膜,所述保护膜从所述ni氧化膜之上覆盖所述第三面和所述第四面,并且覆盖所述栅电极。

[0071]

[本公开的实施方式的详情]

[0072]

以下,对本公开的实施方式详细地进行说明,但本实施方式并不限定于此。需要说明的是,在本说明书和附图中,有时通过对具有实质上相同的功能构成的构成要素标注相同的附图标记来省略重复的说明。

[0073]

本实施方式涉及包含以氮化物半导体为主要构成材料的gan-hemt的半导体装置。图1是表示实施方式的半导体装置的概要的剖视图。图2是表示实施方式的半导体装置中的栅电极及其周边的详情的剖视图。图1和图2表示与栅极宽度方向垂直的截面。

[0074]

如图1所示,本实施方式的半导体装置100具有基板10和形成于基板10之上的多个半导体层的层叠结构20。基板10例如是具有(0001)主面的sic基板,层叠结构20的层叠方向例如是[0001]方向。层叠结构20包含从基板10侧依次形成的电子渡越层12、电子供给层14以及帽层16。电子渡越层12例如是厚度为1000nm左右的非掺杂gan层。电子供给层14例如是厚度20nm左右的n型algan层。帽层16例如是厚度5nm左右的n型gan层。层叠结构20是半导体层的一个例子。

[0075]

在层叠结构20之上形成有第一绝缘膜22。第一绝缘膜22例如是si氮化膜。在第一绝缘膜22和层叠结构20形成有源极用的开口31和漏极用的开口32。与层叠结构20欧姆接触的源电极41形成于开口31内,与层叠结构20欧姆接触的漏电极42形成于开口32内。在第一绝缘膜22、源电极41以及漏电极42之上形成有第二绝缘膜24。第二绝缘膜24例如是si氮化膜。第一绝缘膜22和第二绝缘膜24包含于绝缘膜26。绝缘膜26具有层叠结构20侧的第一面26a和与第一面26a相反侧的第二面26b。第一面26a也是绝缘膜26的下表面,第二面26b也是绝缘膜26的上表面。第一面26a可以与层叠结构20相接。

[0076]

如图2所示,在源电极41与漏电极42之间,在第一绝缘膜22形成有开口22x,在第二绝缘膜24形成有开口24x。开口24x的开口宽度即栅极长度方向的尺寸比开口22x的开口宽度大。例如,开口24x的开口宽度为140nm左右,开口22x的开口宽度为90nm左右。开口24x贯通第二绝缘膜24,开口22x贯通第一绝缘膜22。开口22x经由开口24x而露出,层叠结构20经由开口24x和22x而露出。

[0077]

半导体装置100具有经由开口22x和24x与层叠结构20相接的栅电极43。栅电极43具有ni膜64和形成于ni膜64之上的au膜66。例如,ni膜64的厚度为50nm~100nm左右,au膜66的厚度为300nm~600nm左右。栅电极43例如具备在剖视时呈t字形的形状。就是说,栅电极43具备基部43s和从基部43s向两侧伸出的檐部43t。并且,栅电极43具有离开绝缘膜26的第二面26b并与第二面26b对置的第三面43a。第三面43a也是檐部43t的下表面。栅电极43还具有将第二面26b与第三面43a相连的第四面43b。第四面43b也是基部43s的比第二面26b靠上方且比第三面43a靠下方的部分的侧面。ni膜64构成第三面43a和第四面43b。栅电极43可

以在ni膜64与au膜66之间具有pd膜,也可以在au膜66之上具有ta膜。

[0078]

半导体装置100在第三面43a和第四面43b具有覆盖ni膜64的ni氧化膜68。半导体装置100还具有覆盖栅电极43的保护膜70。保护膜70从ni氧化膜68之上覆盖第三面43a和第四面43b。保护膜70不仅覆盖栅电极43,还可以覆盖绝缘膜26。保护膜70例如是al氧化膜或si氮化膜。保护膜70的厚度不被特别限定,但覆盖第三面43a的部分的厚度优选为20nm以上,更优选为25nm以上。

[0079]

在本实施方式中,在第三面43a和第四面43b,ni膜64被ni氧化膜68覆盖。因此,能抑制ni膜64中的ni的扩散,从而抑制栅电极43的特性的变化。

[0080]

可以在保护膜70的覆盖第三面43a的部分与第二面26b之间存在空隙46。通过存在空隙46,易于减小栅电极43的檐部43t与层叠结构20之间的寄生电容。需要说明的是,也可以代替空隙46而配置所谓的低介电常数(low-k)材料。与存在空隙46的情况相比,能提高机械强度。低介电常数材料的相对介电常数优选为7.0以下,更优选为4.0以下。

[0081]

保护膜70包含al氧化膜或si氮化膜,由此易于保护栅电极43免受来自外部的水分的侵入等。在保护膜70覆盖绝缘膜26的情况下,能更牢固地保护层叠结构20。

[0082]

ni氧化膜68比ni的自然氧化膜厚,ni氧化膜68的厚度例如优选为3nm以上,更优选为5nm以上。这是为了使得更易于抑制ni膜64中的ni的扩散。

[0083]

ni膜64的与绝缘膜26接触的部分的面积优选为ni膜64的与ni氧化膜68接触的部分的面积的0.10倍以下,更优选为0.07倍以下,更优选为0.05倍以下。这是为了使得更易于抑制ni膜64的与绝缘膜26接触的部分处的ni的扩散。

[0084]

绝缘膜26也可以包含与ni膜64接触的si氮氧化膜。例如,第一绝缘膜22和第二绝缘膜24也可以包含作为主体的si氮化膜和覆盖该si氮化膜的表面的si氮氧化膜。绝缘膜26包含与ni膜64接触的si氮氧化膜,由此易于抑制ni膜64与绝缘膜26的界面处的ni的扩散。

[0085]

接着,对实施方式的半导体装置100的制造方法进行说明。图3~图16是表示实施方式的半导体装置的制造方法的剖视图。图3~图8表示图1所示的截面的变化,图9~图16表示图2所示的截面的变化。

[0086]

首先,如图3所示,使用金属有机化学气相沉积(metal organic chemical vapor deposition:mocvd)法在基板10上生长包含多个氮化物半导体层的层叠结构20。接着,使用低压(low pressure:lp)cvd法成膜出与层叠结构20的上表面相接的第一绝缘膜22。第一绝缘膜22例如是厚度为40nm的si氮化膜。可以在形成电子渡越层12之前在基板10之上形成成核层,在成核层之上形成电子渡越层12。成核层例如是厚度几十nm的aln层。

[0087]

接着,如图4所示,在第一绝缘膜22之上涂布电子束抗蚀剂51,通过电子束光刻在电子束抗蚀剂51形成开口51x。第一绝缘膜22经由开口51x而露出。

[0088]

接着,如图5所示,将电子束抗蚀剂51作为掩模,通过反应性离子刻蚀(reactive ion etching:rie)在第一绝缘膜22和层叠结构20形成源极用的开口31和漏极用的开口32。例如,在第一绝缘膜22的刻蚀中使用包含氟(f)的反应性气体,在层叠结构20的刻蚀中使用包含氯(cl)的反应性气体。

[0089]

接着,如图6所示,通过蒸镀法在开口31的内侧和开口32的内侧形成金属层61。金属层61也附着于电子束抗蚀剂51的上表面和开口51x的侧壁面。金属层61例如包含从基板10侧依次形成的ta膜、al膜以及mo膜。

[0090]

接着,如图7所示,去除电子束抗蚀剂51。随着电子束抗蚀剂51的去除,金属层61的附着于电子束抗蚀剂51的部分也被去除。另一方面,在开口31和32的内侧残存金属层61。就是说,进行剥离。接着,通过热处理使金属层61合金化(alloy)。由此,与层叠结构20欧姆接触的源电极41形成于开口31内,与层叠结构20欧姆接触的漏电极42形成于开口32内。

[0091]

接着,如图8所示,使用等离子体(plasma enhanced:pe;等离子体增强)cvd法在第一绝缘膜22、源电极41以及漏电极42之上成膜出第二绝缘膜24。第二绝缘膜24例如是厚度为20nm的si氮化膜。第一绝缘膜22和第二绝缘膜24包含于绝缘膜26。

[0092]

接着,如图9所示,在第二绝缘膜24、源电极41以及漏电极42之上涂布电子束抗蚀剂52。作为电子束抗蚀剂52,例如使用聚甲基丙烯酸甲酯(pmma:polymethyl methacrylate)。作为电子束抗蚀剂52,也可以使用日本zeon株式会社制的zep520a-7。接着,通过电子束光刻在电子束抗蚀剂52形成开口52x。开口52x的开口宽度即栅极长度方向的尺寸例如为70nm左右。第二绝缘膜24经由开口52x而露出。

[0093]

接着,如图10所示,将电子束抗蚀剂52作为掩模,通过使用了包含氟的反应性气体的rie在第二绝缘膜24形成栅极用的开口24x,在第一绝缘膜22形成栅极用的开口22x。在开口24x和22x的形成中,在一定的条件下对第二绝缘膜24和第一绝缘膜22进行刻蚀。在第二绝缘膜24发生显著的侧面刻蚀(side etch),开口24x的开口宽度成为比开口22x的开口宽度大。例如,开口24x的开口宽度为140nm左右,开口22x的开口宽度为90nm左右。层叠结构20经由开口24x和22x而露出。

[0094]

接着,如图11所示,去除电子束抗蚀剂52。接着,在帽层16、第一绝缘膜22、第二绝缘膜24、源电极41以及漏电极42之上依次涂布电子束抗蚀剂53、电子束抗蚀剂54以及电子束抗蚀剂55。使用pmma来作为电子束抗蚀剂53和55,使用聚甲基戊二酰亚胺(pmgi:polymethylglutarimide)来作为电子束抗蚀剂54。电子束抗蚀剂53和55能进行比电子束抗蚀剂54更微细的加工。接着,通过电子束光刻,在电子束抗蚀剂55形成开口55x,在电子束抗蚀剂54形成开口54x,在电子束抗蚀剂53形成开口53x。例如,开口55x的开口宽度为500nm左右,开口54x的开口宽度为580nm左右,开口53x的开口宽度为290nm左右。第二绝缘膜24、第一绝缘膜22以及帽层16经由开口55x、54x以及53x而露出。

[0095]

接着,如图12所示,进行烘烤,使电子束抗蚀剂53以开口53x的下端处的开口宽度比开口53x的上端处的开口宽度小的方式变形。就是说,使开口53x的侧壁面变形为锥形。也可以使电子束抗蚀剂53以开口53x的下端与开口24x的上端一致的方式自对准(self-alignment)地变形。

[0096]

接着,如图13所示,通过蒸镀法在开口55x、54x、53x、24x以及22x的内侧形成金属层62。在金属层62的形成中,形成ni膜64,在ni膜64之上形成au膜66。例如,ni膜64的厚度为50nm~100nm左右,au膜66的厚度为300nm~600nm左右。可以在ni膜64与au膜66之间形成pd膜,也可以在au膜66之上形成ta膜。金属层62也附着于电子束抗蚀剂55的上表面和开口55x的侧壁面。

[0097]

接着,如图14所示,去除电子束抗蚀剂55、54以及53。随着电子束抗蚀剂55、54以及53的去除,金属层62的附着于电子束抗蚀剂55的部分也被去除。另一方面,在开口24x和22x的内侧以及第一绝缘膜22和第二绝缘膜24之上残存金属层62。就是说,进行剥离。残存的金属层62例如具备在剖视时呈t字形的形状。

[0098]

接着,如图15所示,通过使金属层62中所包含的ni膜64的表面氧化来形成ni氧化膜68。由此,形成具有ni膜64和au膜66并经由开口22x与层叠结构20肖特基接触的栅电极43。就是说,由金属层62中的成为ni氧化膜68的部分的剩余部分形成栅电极43。栅电极43例如具备在剖视时呈t字形的形状。例如可以使用臭氧来使ni膜64氧化。

[0099]

接着,如图16所示,形成覆盖栅电极43的保护膜70。保护膜70与ni氧化膜68和au膜66接触,但不与ni膜64接触。保护膜70从ni氧化膜68之上覆盖ni膜64。保护膜70例如是al氧化膜或si氮化膜。al氧化膜例如可以通过ald法形成。si氮化膜例如可以通过等离子体cvd法形成。在通过等离子体cvd法形成了si氮化膜的情况下,在装置的特性上,si氮化膜也可以含有氟(f)。

[0100]

之后,根据需要形成布线等。像这样,能制造包含gan-hemt的半导体装置100。

[0101]

根据这样的制造方法,易于形成抑制ni膜64中的ni的扩散的ni氧化膜68。

[0102]

此外,在通过ald法形成al氧化膜来作为保护膜70的情况下,能使用与ni膜64的表面的氧化相同的装置来进行成膜。另一方面,在通过cvd法形成si氮化膜来作为保护膜70的情况下,能以高的成膜速率形成保护膜70。

[0103]

需要说明的是,在绝缘膜26包含si氮化膜的情况下,si氮化膜的表面也可以被氧化。就是说,绝缘膜26的表面也可以成为si氮氧化膜。例如,si氮化膜的表面可以在形成第二绝缘膜24之后直至形成ni膜64之前的期间的各种热处理等中被氧化。

[0104]

此外,ni膜64能与层叠结构20肖特基接触即可,无需从与层叠结构20接触的部分连续至第三面43a,可以部分地被截断。例如,由于蒸镀时的覆盖率(coverage)等的影响,在第一绝缘膜22的角部、第二绝缘膜24的角部等,ni膜64也可以不连续。

[0105]

以上,对实施方式进行了详细叙述,但并不限定于特定的实施方式,在权利要求书所记载的范围内,可以进行各种变形和变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1