集成电路结构及其制造方法与流程

1.本揭露是关于一种集成电路结构,特别是关于一种集成电路结构的制造方法。

背景技术:

2.半导体集成电路(integrated circuit,ic)行业经历了快速增长。集成电路材料及设计的技术进步产生了一代又一代的集成电路。与先前一代相比,每一代都有更小且更复杂的电路。

技术实现要素:

3.于一些实施方式中,集成电路结构包含下部互连结构、第一半导体鳍片、下部栅极结构、多个第一源极/漏极结构、上部栅极结构以及上部互连结构。第一半导体鳍片位于下部互连结构的上方。下部栅极结构位于第一半导体鳍片下方且延伸跨越第一半导体鳍片。多个第一源极/漏极结构位于第一半导体鳍片中,且位于下部栅极结构的相对侧上。第一源极/漏极结构与下部栅极结构形成下部晶体管。上部栅极结构位于第一半导体鳍片的上方且延伸跨越第一半导体鳍片。上部栅极结构与第一源极/漏极结构形成上部晶体管。上部互连结构位于上部栅极的上方。

4.于一些实施方式中,集成电路结构包含第一互连结构、第一栅极结构、第一半导体鳍片、第一半导体基材、第二半导体鳍片、第二栅极结构以及第二互连结构。第一栅极结构在第一互连结构的上方的第一位准高度处延伸。第一半导体鳍片延伸于第一栅极结构的上方且跨越第一栅极结构。第一半导体基材位于半导体鳍片上方。第二半导体鳍片延伸于第一半导体基材的上方。第二栅极结构在第二半导体鳍片的上方的第二位准高度处延伸且跨越第二半导体鳍片,第二位准高度高于第一位准高度。第二互连结构,位于第二栅极结构上方。

5.于一些实施方式中,集成电路结构的形成方法,包含在基材上方形成第一互连结构;在第一互连结构上方形成第一介电层;在第一介电层中蚀刻栅极沟槽;在第一介电层中该栅极沟槽中形成第一栅极结构;在第一栅极结构上方沉积第二介电层;在第二介电层中蚀刻一鳍片沟槽且在垂直于栅极沟槽的一方向上延伸;在第二介电层中鳍片沟槽中形成一半导体鳍片;以及形成延伸跨越第二半导体鳍片的一第二栅极结构。

附图说明

6.本揭露的态样在与随附附图一起研读时自以下详细描述内容来最佳地理解。应注意,根据行业中的标准规范,各种特征未按比例绘制。实际上,各种特征的尺寸可为了论述清楚经任意地增大或减小。

7.图1a至图1c是根据本揭露的一些实施例的形成集成电路结构的方法的流程图;

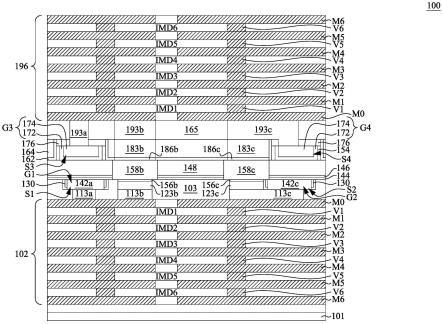

8.图2至图28示出了根据本揭露的一些实施例的形成集成电路结构的各个阶段的方法;

9.图29a及图29b示出了根据一些其他实施例的如图18a中所示的沿着线b-b'及线d-d'的集成电路结构的横截面图;

10.图30a及图30b示出了根据一些其他实施例的如图18a中所示的沿着线b-b'及线d-d'的集成电路结构的横截面图;

11.图31a及图31b示出了根据一些其他实施例的如图18a中所示的沿着线b-b'及线d-d'的集成电路结构的示意图;

12.图32a及图32b示出了根据一些其他实施例的如图18a中所示的沿着线b-b'及线d-d'的集成电路结构的示意图;

13.图33a至图33c是根据本揭露的一些实施例的形成集成电路结构的方法的流程图;

14.图34至图36示出了根据本揭露的一些实施例的形成集成电路结构的各个阶段的方法;

15.图37a至图37c示出了根据一些其他实施例的集成电路结构的示意图;

16.图38及图39示出了根据本揭露的一些实施例的制造集成电路结构中的横截面图。

17.【符号说明】

18.100:集成电路结构

19.101:基材

20.102:互连结构

21.103:介电层

22.104:隔离介电质

23.113:导电材料

24.113a:栅极通孔

25.113b:源极/漏极通孔

26.113c:抵接触点

27.123:导电材料

28.123b:源极/漏极触点

29.123c:抵接触点

30.130:栅极间隔物

31.132:第一间隔层

32.134:第二间隔层

33.142a,142c:栅电极

34.144:栅极介电层

35.143:侧壁

36.144:栅极介电层

37.146:界面层

38.148:半导体鳍片

39.148r:源极/漏极开口

40.152a,152c:虚设栅极结构

41.154:栅极间隔物

42.156b,156c:硅化物层

43.158b,158c:磊晶源极/漏极结构

44.162:接触蚀刻终止层

45.164:介电层

46.165:介电层

47.172:栅极介电层

48.174:金属栅电极

49.176:介电帽

50.183b,183c:源极/漏极触点

51.186b,186c:硅化物层

52.193a:栅极通孔

53.193b:源极/漏极通孔

54.193c:抵接触点

55.196:互连结构

56.200:集成电路结构

57.201:基材

58.202:互连结构

59.203:介电层

60.213a:栅极通孔

61.213b:源极/漏极通孔

62.213c:抵接触点

63.223b,223c:源极/漏极触点

64.230:栅极间隔物

65.248a:第一半导体鳍片

66.248b:第二半导体鳍片

67.254:栅极间隔物

68.256b,256c:硅化物

69.258b~258e:磊晶源极/漏极结构

70.262:接触蚀刻终止层

71.265:介电层

72.283b,283c:源极/漏极触点

73.286b,286c:硅化物

74.293a:栅极通孔

75.293b:源极/漏极通孔

76.293c:抵接触点

77.296:互连结构

78.300:集成电路结构

79.301:基材

80.302:互连结构

81.303:介电层

82.313b:源极/漏极通孔

83.313c:抵接触点

84.323b,323c:源极/漏极触点

85.330:栅极间隔物

86.348a:第一半导体鳍片

87.348b:第二半导体鳍片

88.354:栅极间隔物

89.356b,356c:硅化物

90.358b~358e:磊晶源极/漏极结构

91.362:接触蚀刻终止层

92.365:介电层

93.383b,383c:源极/漏极触点

94.386b,386c:硅化物

95.393a:栅极通孔

96.393b:源极/漏极通孔

97.393c:抵接触点

98.396:互连结构

99.400:集成电路结构

100.401:基材

101.402:互连结构

102.403:介电层

103.413a:栅极通孔

104.413b:源极/漏极通孔

105.413c:抵接触点

106.423b,423c:源极/漏极触点

107.430:栅极间隔物

108.448a,448b:半导体鳍片

109.454:栅极间隔物

110.456b,456c:硅化物层

111.458b~458e:磊晶源极/漏极结构

112.462:接触蚀刻终止层

113.465:介电层

114.483b,483c:源极/漏极触点

115.486b,486c:硅化物层

116.493b:源极/漏极通孔

117.493c:抵接触点

118.496:互连结构

119.500:集成电路结构

120.501:基材

121.502:互连结构

122.503:介电层

123.513a:栅极通孔

124.513b:源极/漏极通孔

125.513c:抵接触点

126.523b,523c:源极/漏极触点

127.530:栅极间隔物

128.548a,548c:半导体鳍片

129.554:栅极间隔物

130.556b,556c:硅化物层

131.558b~558e:磊晶源极/漏极结构

132.562:接触蚀刻终止层

133.565:介电层

134.583b,583c:源极/漏极触点

135.586b,586c:硅化物层

136.593a:栅极通孔

137.593b:源极/漏极通孔

138.593c:抵接触点

139.596:互连结构

140.600:集成电路结构

141.601:基材

142.602:互连结构

143.603:介电层

144.607:基材

145.613a:栅极通孔

146.613b:源极/漏极通孔

147.613c:抵接触点

148.623b,623c:源极/漏极触点

149.630:栅极间隔物

150.648a,648b:半导体鳍片

151.648r:源极/漏极开口

152.654:栅极间隔物

153.656b,656c:硅化物层

154.658b~658e:磊晶源极/漏极结构

155.662:接触蚀刻终止层

156.665:介电层

157.676:介电帽

158.683b,683c:源极/漏极触点

159.686b,686c:硅化物层

160.693a:栅极通孔

161.693b:源极/漏极通孔

162.693c:抵接触点

163.696:互连结构

164.700:集成电路结构

165.700a,700b:半导体结构

166.707:基材

167.707':基材

168.709:钝化层

169.709':钝化层

170.748b:半导体鳍片

171.748b':半导体鳍片

172.754:栅极间隔物

173.754':栅极间隔物

174.758d,758e:磊晶源极/漏极结构

175.758d',758e':磊晶源极/漏极结构

176.762:接触蚀刻终止层

177.762':接触蚀刻终止层

178.765:介电层

179.765':介电层

180.776:介电帽

181.776':介电帽

182.783b,783c:源极/漏极触点

183.783b',783c':源极/漏极触点

184.793a:栅极通孔

185.793a':栅极通孔

186.793b:源极/漏极通孔

187.793b':源极/漏极通孔

188.793c:抵接触点

189.793c':抵接触点

190.796:互连结构

191.796':互连结构

192.800:集成电路结构

193.803:介电层

194.813a:栅极通孔

195.813b:源极/漏极通孔

196.813c:抵接触点

197.823b,823c:源极/漏极触点

198.830:栅极间隔物

199.848:半导体鳍片

200.854:栅极间隔物

201.865:介电层

202.856b,856c:硅化物层

203.858b,858c:磊晶源极/漏极结构

204.883b,883c:源极/漏极触点

205.886b,886c:硅化物层

206.893b:源极/漏极通孔

207.893c:抵接触点

208.900:集成电路结构

209.903:介电层

210.907:基材

211.913a:栅极通孔

212.913b:源极/漏极通孔

213.913c:抵接触点

214.923b,923c:源极/漏极触点

215.930:栅极间隔物

216.948a,948b:半导体鳍片

217.954:栅极间隔物

218.956b,956c:硅化物层

219.958c:磊晶源极/漏极结构

220.965:介电层

221.983b,983c:源极/漏极触点

222.986b,986c:硅化物层

223.993b:源极/漏极通孔

224.993c:抵接触点

225.b-b':线

226.c-c':线

227.d1:深度

228.d-d':线

229.ft:鳍片沟槽

230.g1~g4,g21~g24,g32~g34,g41,g42,g44,g51~g54,g61~g64,g73~g74,g7

231.3'~g74',g81~g86,g91~g96:栅极结构

232.gt1~gt2:栅极沟槽

233.imd1~imd6:imd层

234.l1:长度

235.m1~m2:方法

236.m0~m6:金属化层

237.o1~o3:开口

238.o4~o5:凹槽

239.s1,s61:第一晶体管

240.s101~s127:方块

241.s2,s62:第二晶体管

242.s21~s24,s51~s54:晶体管

243.s201~s231:方块

244.s3,s63:第三晶体管

245.s4,s64:第四晶体管

246.v1~v6:金属化通孔或互连件

247.w1:宽度

具体实施方式

248.以下揭示内容提供用于实施所提供标的物的不同特征的许多不同实施例、或实例。下文描述组件及配置的特定实例以简化本揭露。当然,这些仅为实例且非意欲为限制性的。举例而言,在以下描述中第一特征于第二特征上方或上的形成可包括第一特征与第二特征直接接触地形成的实施例,且亦可包括额外特征可形成于第一特征与第二特征之间使得第一特征与第二特征可不直接接触的实施例。此外,本揭露在各种实例中可重复参考数字及/或字母。此重复是出于简单及清楚的目的,且本身且不指明所论述的各种实施例及/或组态之间的关系。

249.此外,为了便于描述,在本文中可使用空间相对术语,诸如“在

……

下面”、“在

……

之下”、“下部”、“在

……

之上”、“上部”及类似者,来描述诸图中图示的一个元件或特征与另一(多个)元件或特征的关系。空间相对术语意欲涵盖除了诸图中所描绘的定向以外的装置在使用或操作时的不同定向。装置可另外定向(旋转90度或处于其他定向),且本文中所使用的空间相对描述符可类似地加以相应解释。

250.如本文中所使用,“大约”、“约”、“大致”、或“大体上”应通常指给定值或范围的20%内、或10%内、或5%内。然而,熟悉此项技术者将认识到,在整个描述中所引用的值或范围仅是实例,且可随着集成电路的规模缩小而减小。本文中给定的数量为近似值,从而意谓术语“大约”、“约”、“大致”、或“大体上”在并未明确陈述情况下可予以推断。

251.本揭露的实施例涉及但不限于鳍式场效晶体管(fin-like field-effect transistor,finfet)装置。举例而言,finfet装置可是互补金属氧化物半导体(complementary metal-oxide-semiconductor,cmos)装置,包括p型金属氧化物半导体(p-type metal-oxide-semiconductor,pmos)finfet装置及n型金属氧化物半导体(n-type metal-oxide-semiconductor,nmos)finfet装置。以下揭示内容将继续使用一或多个finfet实例来说明本揭露的各种实施例。然而,应理解,除非特别声明,否则该应用不应限于特定类型的装置。

252.鳍片可通过任何适合的方法来图案化。举例而言,可使用一或多个光学微影术制程(包括双重图案化或多重图案化制程)来图案化鳍片。双重图案化或多重图案化制程结合了光学微影术及自对准制程,允许产生具有例如比使用单个直接光学微影术制程获得的间距更小的图案。举例而言,在一个实施例中,在基材上方形成牺牲层且使用光学微影术制程

图案化。使用自对准制程沿着经图案化牺牲层形成间隔物。接着移除牺牲层,剩余的间隔物接着可用于图案化鳍片。

253.在集成电路(integrated circuit,ic)的演进过程中,功能密度(即每一晶片面积的互连装置数目)通常有所增加,而几何尺寸(即,可使用制造制程产生的最小组件(或接线))有所减小。这种缩小规模的过程通常通过提高生产效率及降低相关成本来提供益处。然而,这些进步增加了集成电路加工及制造的复杂性。由于特征尺寸继续减小,制造制程继续变得更加难以执行。因此,形成尺寸越来越小的可靠半导体装置是一挑战。

254.因此,在各种实施例中,本揭露在晶片的给定晶体管面积上提供了“双半导体装置”。更具体地,在给定晶体管面积内,晶体管设置于另一晶体管之上,这进而使给定晶体管面积内的晶体管数目加倍,从而可增加ic的功能密度。

255.现在参考图1a至图1c,示出了根据一些实施例的用于制造集成电路结构的例示性方法m1的流程图。方法m1包括整个制造制程的相关部分。应理解,可在图1a至图1c中所示的操作之前、期间、及之后提供额外操作,且对于该方法的额外实施例,可替换或消除下面描述的一些操作。操作/制程的次序可互换。方法m1包括制造集成电路结构。然而,集成电路结构的制造仅是用于描述根据本揭露的一些实施例的制造制程的一实例。

256.图2至图28示出了根据本揭露的一些实施例的在形成集成电路结构100的各个阶段中的方法m1。图14a、图15a、图16a、及图18a示出了根据本揭露的一些实施例的集成电路结构100的俯视图。图2至图13、图14b、图14c、图15b、图15c、图16b、图16c、图17、图18b、图18c、及图19至图28示出了根据本揭露的一些实施例的集成电路结构100的横截面图,其中图14b、图15b、图16b、及图18b是沿着图14a、图15a、图16a、及图18a中的线b-b'截取的横截面图,且图14c、图15c、图16c、及图18c是沿着图14a、图15a、图16a、及图18a中的线c-c'截取的横截面图,包括集成电路结构100的下部晶体管的下部栅电极。

257.方法m1开始于方块s101,其中在基材上方形成下部互连结构。参考图2,在方块s101的一些实施例中,基材101包括硅。或者,基材101可包括锗、硅锗、砷化镓或其他适当半导体材料。亦可替代地,基材101可包括磊晶层。举例而言,基材101可具有上覆体半导体的磊晶层。此外,基材101可施加应变以增强性能。举例而言,磊晶层可包括不同于体半导体的半导体材料,诸如上覆体硅的硅锗层或上覆体硅锗的硅层。这种应变基材可通过选择性磊晶生长(selective epitaxial growth,seg)形成。此外,基材101可包括绝缘体上半导体(semiconductor-on-insulator,soi)结构。同样可替代地,基材101可包括埋入式介电层,诸如埋入式氧化物(buried oxide,box)层,诸如通过分离植入氧气(separation by implantation of oxygen,simox)技术、晶圆接合、seg、或另一适当方法而形成的层。

258.在一些实施例中,互连结构102在晶体管形成之前形成于基材101上。互连结构102包括例如标记为m0至m6的七个金属化层、及标记为v1至v6的六个层的金属化通孔或互连件。其他实施例可含有更多或更少的金属化层及相应的更多或更少数目的通孔。此处所示的金属线仅作为实例,金属线可以其他方式定向(旋转90度或以其他定向)。集成电路结构100包括全金属化堆叠,包括通过互连件v1~v6连接的金属化层m0~m6中的各者的一部分,其中m0将堆叠连接至后续形成的晶体管的后续形成的源极/漏极触点。集成电路中亦包括多个imd层。图2中描述了六个imd层,标识为imd1至imd6。imd层可在许多制造制程步骤期间为集成电路的各种特征提供电绝缘及结构支撑。

259.返回参考图1a,方法m1接着进行至方块s102,其中在下部互连结构上方形成第一介电层。参考图3,在方块s102的一些实施例中,在互连结构102上方形成介电层103。在一些实施例中,在形成介电层103之前在互连结构102上方形成蚀刻终止层(未显示)。在一些实施例中,介电层103可由与imd层类似的材料形成。作为实例但不限制本揭露地,介电层103可由氧化硅、氮化硅、氧氮化硅、四乙氧基硅烷(teos)氧化物、磷硅玻璃(psg)、硼磷硅玻璃(bpsg)、低k介电材料、其他适合材料、或其组合物制成。低k介电材料的实例包括但不限于氟硅酸盐玻璃(fsg)、或掺碳氧化硅、。在一些实施例中,用于形成介电层103的介电材料可使用任何适合的方法来沉积,诸如化学气相沉积(cvd)、ald、peald、pecvd、sacvd、fcvd、旋装、及/或其组合。

260.返回参考图1a,方法m1接着进行至方块s103,其中第一介电层经蚀刻以形成多个第一开口,其曝光下部互连结构中最上金属化层。参考图4,在方块s103的一些实施例中,介电层103经蚀刻以形成开口o1、o2、及o3,这些开口曝光互连结构102中最上金属化层m0,其中开口o1、o2、及o3可具有栅极通孔(或称为栅极触点)113a、源极/漏极通孔113b、及将在后续制程中形成于其中的抵接触点113c(见图6),这些通孔将与后续形成的晶体管s1及s2的栅电极142a及142c以及磊晶源极/漏极结构158b及158c进行实体连接及电连接,如图28中所示。具体而言,这些开口o1、o2、及o3曝光金属化层m0的多个分离区域。通过使用光学微影术及第一蚀刻制程形成开口o1、o2、及o3。举例而言,可在介电层103上方形成第一经图案化遮罩(未显示),且用于保护下伏其的介电层103不受第一蚀刻制程的影响。随后,穿过第一经图案化遮罩在介电层103上执行第一蚀刻制程且直到达到金属化层m0终止。第一蚀刻制程可包括干式蚀刻、湿式蚀刻、反应离子蚀刻(reactive ion etch,rie)、另一适合的蚀刻制程、或其组合。因此,金属化层m0曝光于开口o1、o2、及o3中。第一经图案化遮罩随后经剥离,诸如通过湿式剥离或电浆灰化。

261.返回参考图1a,方法m1接着进行至方块s104,其中一或多个第一导电材料沉积于第一介电层上方,以填充第一介电层中的第一开口。参考图5,在方块s105的一些实施例中,一或多个导电材料113沉积于介电层103上方,以填充介电层103中的开口o1、o2、及o3。在一些实施例中,导电材料113可由铜(cu)、铝(al)、co(钴)、钛(ti)、氮化钛(tin)、钽(ta)、氮化钽(tan)、碳化钽(tac)、氮化钽硅(tasin)、钨(w)、氮化钨(wn)、氮化钼(mon)、类似物及/或其组合物形成。在一些实施例中,导电材料113可使用任何适合的方法沉积,诸如cvd、ald、peald、pecvd、pvd、ecp、化学镀、及/或类似者、或其组合。

262.返回参考图1a,方法m1接着进行至方块s105,其中执行第一平坦化制程以自第一介电层的顶表面之上移除多余的第一导电材料,以在第一介电层中形成用于下部晶体管的下部栅极通孔、下部源极/漏极通孔、及/或下部抵接触点。参考图6,在方块s105的一些实施例中,可使用化学机械研磨(chemical mechanical polish,cmp)制程自介电层103的顶表面之上移除多余的导电材料113。剩余导电结构填充介电层103中的开口o1、o2、及o3,且用作栅极通孔113a、源极/漏极通孔113b、及抵接触点113c,与互连结构102中金属化层m0进行实体连接及电连接。在一些实施例中,栅极通孔113a、源极/漏极通孔113b、及抵接触点113c可同时形成,或通过使用光学微影术、蚀刻及沉积技术的分离图案化制程形成。

263.返回参考图1a,方法m1接着进行至方块s106,其中用于下部晶体管的下部源极/漏极通孔及/或下部抵接触点经蚀刻以形成凹槽。参考图7,在方块s106的一些实施例中,源

极/漏极通孔113b及抵接触点113c的部分经蚀刻以在介电层103中形成凹槽o4及o5。具体而言,这些凹槽o4及o5曝光经蚀刻源极/漏极触点113b及抵接触点113c。凹槽o4及o5通过使用第二光学微影术及第二蚀刻制程形成。举例而言,可在栅极通孔113a、抵接触点113c的第一部分、及源极/漏极通孔113b的第一部分上方形成第二经图案化遮罩(未显示)。随后,经由第二经图案化遮罩在源极/漏极通孔113b的第二部分及抵接触点113c的第二部分上执行第二蚀刻制程,以使源极/漏极触点113b的第二部分及抵接触点113的第二部分凹陷,从而在源极/漏极通孔113b的第二部分之上形成凹槽o4,且在抵接触点的第二部分之上形成凹槽o5。第二蚀刻制程可包括干式蚀刻、湿式蚀刻、反应离子蚀刻(reactive ion etch,rie)、另一适合的蚀刻制程、或其组合。第二经图案化遮罩随后经剥离,诸如通过湿式剥离或电浆灰化。

264.返回参考图1a,方法m1接着进行至方块s107,其中一或多个第二导电材料沉积于第一介电层上方,以填充下部源极/漏极通孔及/或下部抵接触点上的凹槽。参考图8,在方块s107的一些实施例中,在介电层上方沉积一或多个导电材料123以填充介电层103中凹槽o4及o5。在一些实施例中,导电材料123可由铜(cu)、铝(al)、钛(ti)、钴(co)、氮化钛(tin)、钽(ta)、氮化钽(tan)、碳化钽(tac)、氮化硅钽(tasin)、钨(w)、氮化钨(wn)、氮化钼(mon)、类似物及/或其组合物形成。在一些实施例中,导电材料123可使用任何适合的方法沉积,诸如cvd、ald、peald、pecvd、pvd、ecp、化学镀、及/或类似者、或其组合。

265.参考图1a,方法m1接着进行至方块s108,其中执行第二平坦化制程以自第一介电层的顶表面之上移除多余的第二导电材料,以在下部源极/漏极通孔及/或下部抵接触点上形成用于下部晶体管的下部源极/漏极触点。参考图9,在方块s108的一些实施例中,平坦化制程(例如,cmp)可用于自介电层103的顶表面之上移除多余的导电材料123。剩余的导电结构填充介电层103中凹槽o4及o5,且用作源极/漏极通孔113b及抵接触点113c上的源极/漏极触点123b及源极/漏极触点123c。在一些实施例中,源极/漏极触点123b及123c可通过使用光学微影术、蚀刻及沉积技术同时形成。

266.返回参考图1a,方法m1接着进行至方块s109,其中蚀刻下部栅极通孔及/或下部抵接触点以在其上形成第一栅极沟槽。参考图10,在方块s109的一些实施例中,蚀刻栅极通孔113a、抵接触点113c、及相邻于栅极通孔113a及抵接触点113c的介电层103的部分,以在介电层103中形成栅极沟槽gt1及gt2。具体而言,这些栅极沟槽gt1及gt2曝光栅极通孔113a及抵接触点113c的第一部分。栅极沟槽gt1及gt2通过使用第三光学微影术及第三蚀刻制程形成。举例而言,可在源极/漏极触点123b及123c上方形成第三经图案化遮罩(未显示),且用于保护源极/漏极触点123b及123c免受第三蚀刻制程的影响。随后,经由第三经图案化遮罩对栅极通孔113a及抵接触点113c的第一部分执行第三蚀刻制程,以使栅极通孔113a及抵接触点113c的第一部分凹陷,从而形成栅极沟槽gt1及gt2。第三蚀刻制程可包括干式蚀刻、湿式蚀刻、反应离子蚀刻(reactive ion etch,rie)、另一适合的蚀刻制程、或其组合。第三经图案化遮罩随后经剥离,诸如通过湿式剥离或电浆灰化。

267.返回参考图1b,方法m1接着进行至方块s110,其中间隔层沉积于第一介电层上方,以衬于第一栅极沟槽的侧壁及下部栅极通孔及/或下部抵接触点的顶表面。参考图11,在方块s110的一些实施例中,第一间隔层132及第二间隔层134沉积于图10所示的结构上方。其他实施例可含有更多或更少的间隔层。在图11中,第一间隔层132衬于栅极沟槽gt1及gt2的

侧壁及栅极沟槽gt1中的栅极通孔113a的顶表面、及栅极沟槽gt2中的抵接触点113c的顶表面。随后,在第一间隔层132上方共形地形成第二间隔层134。第二间隔层134可由不同于第一间隔层132的材料制成。在一些实施例中,第二间隔层134具有小于第一间隔层132的介电常数。

268.在一些实施例中,第一间隔层132及/或第二间隔层134可包括低k含碳材料,诸如举例而言,氧化硅、氮化硅、氧碳氮化硅(siocn)、氧碳化硅(sioc)、碳化硅(sic)、或其他适合的介电材料。在一些实施例中,第一间隔层132及/或第二间隔层134可包括多孔介电材料。在一些实施例中,第一间隔层132及/或第二间隔层134可包括其他低k介电材料,诸如掺碳二氧化硅、低k氮化硅、低k氧氮化硅、聚酰亚胺、旋装玻璃(sog)、掺氟硅酸盐玻璃(fsg)、磷硅玻璃(psg)、其他适合的低k介电材料、及/或其组合物。在一些实施例中,第一间隔层132及/或第二间隔层134可通过沉积制程形成,诸如原子层沉积(atomic layer deposition,ald)制程、化学气相沉积(chemical vapor deposition,cvd)制程(诸如电浆增强化学气相沉积(plasma enhanced cvd,pecvd)、低压化学气相沉积(low pressure cvd,lpcvd)、原子层沉积(atomic layer deposition,ald)、或其他适合的技术。

269.返回至图1b,方法m1接着进行至方块s111,其中间隔层经图案化以形成第一栅极间隔物。参考图12,在方块s111的一些实施例中,执行第四蚀刻制程以移除第一介电层132及第二介电层134的部分,且第一介电层132及第二介电层134的剩余部分可用作位于栅电极142a及142c(见图13)的相对侧上的栅极间隔物130,其将在后续制程中形成。即,如图13中所示,两个栅极间隔物130分别位于后续形成的栅电极142a及142c的两个相对侧壁143上。第四蚀刻制程可是,举例而言,各向异性蚀刻制程。第四蚀刻制程可包括单个步骤或多个步骤。在一些实施例中,第四蚀刻制程是干式蚀刻制程。作为实例而非限制地,干式蚀刻制程可实施含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、及/或c4f6、c4f8)、含氯气体(例如,cl2及/或bcl3)、含溴气体(例如,hbr)、含碘气体、其他适合的气体及/或电浆、及/或其组合物。

270.返回参考图1b,方法m1接着进行至方块s112,其中在第一栅极沟槽中形成下部晶体管的下部栅电极。参考图13,在方块s112的一些实施例中,栅电极142a及142c分别形成于栅极沟槽gt1及gt2中,且在栅极通孔113a及抵接触点113c的第一部分上方。另一方面,抵接触点113c的第一部分与栅电极142c重叠,且抵接触点113c的第二部分与源极/漏极触点123c重叠。形成这些栅电极142a及142c的例示性方法可包括在介电层103上方形成一或多个功函数金属层,在一或多个功函数金属层上方形成填充金属层,及执行cmp制程以移除栅极沟槽gt1及gt2之外的填充金属层及一或多个功函数金属层的多余材料。

271.在一些实施例中,栅电极142a或142c可包括适合的功函数金属以提供适合的功函数。在一些实施例中,栅电极142a或142c可包括用于在基材101上形成n型晶体管的一或多个n型功函数金属(n型金属)。n型功函数金属可例示性地包括但不限于钛铝(tial)、氮化钛铝(tialn)、碳氮化钽(tacn)、铪(hf)、锆(zr)、钛(ti)、钽(ta)、铝(al)、金属碳化物(例如,碳化铪(hfc)、碳化锆(zrc)、碳化钛(tic)、碳化铝(alc))、铝化物、及/或其他适合的材料。在替代实施例中,栅电极142a或142c可包括用于在基材101上形成p型晶体管的一或多个p型功函数金属(p型金属)。p型功函数金属可例示性地包括但不限于氮化钛(tin)、氮化钨(wn)、钨(w)、钌(ru)、钯(pd)、铂(pt)、钴(co)、镍(ni)、导电金属氧化物、及/或其他适合材

料。栅电极142a及142c中的至少两者可由不同的功函数金属制成,以便在一些实施例中达成适合的功函数。在一些实施例中,栅电极142a或142c的整体是功函数金属。

272.返回参考图1b,方法m1接着进行至方块s113,其中隔离介电质沉积于第一介电层上方。参考图14a至图14c,在方块s113的一些实施例中,隔离介电质104沉积于介电层上方。隔离介电质104可包括任何适合的介电材料,诸如氧化硅。形成隔离介电质104的方法可包括在介电层103上沉积隔离介电质104,以覆盖栅电极142a及142c、栅极间隔物130、及源极/漏极触点123b及123c。在一些实施例中,隔离介电质104可通过沉积制程形成,诸如化学气相沉积(chemical vapor deposition,cvd)、原子层沉积(atomic layer deposition,ald)、电浆增强化学气相沉积(plasma enhanced cvd,pecvd)或其他适合技术。

273.返回参考图1b,方法m1接着进行至方块s114,其中隔离介电质经蚀刻以形成多个鳍片沟槽,鳍片沟槽具有延伸跨越栅电极的长度,且具有向下至下部栅电极的深度。参考图15a至图15c,在方块s114的一些实施例中,在隔离介电质104上执行第五蚀刻制程,以形成多个鳍片沟槽ft。各个鳍片沟槽ft具有如图15a及图15b中所示的延伸跨越栅极142a及142c的长度l1、如图15c中所示向下至栅电极142a及142c的深度d1、及如图15a及图15c中所示的宽度w1。换言之,鳍片沟槽ft的深度d1大于隔离介电质104的厚度。在一些实施例中,鳍片沟槽ft通过使用第五光学微影术及第五蚀刻制程形成。举例而言,可在隔离介电质104上方形成第五经图案化遮罩(未显示)。随后,在隔离介电质104上穿过第五经图案化遮罩执行第五蚀刻制程,以蚀刻穿过隔离介电质104且进一步蚀刻栅电极142a及142c的部分,因此形成鳍片沟槽ft。第五蚀刻制程可包括干式蚀刻、湿式蚀刻、反应离子蚀刻(reactive ion etch,rie)、另一适合的蚀刻制程、或其组合。第五经图案化遮罩随后经剥离,诸如通过湿式剥离或电浆灰化。

274.返回参考图1b,方法m1接着进行至方块s115,其中在鳍片沟槽中形成下部晶体管的界面层、栅极介电层、及半导体鳍片,其中界面层及栅极介电层绕半导体鳍片包覆。参考第16a至图16c,在方块s115的一些实施例中,形成栅极介电层144以衬于鳍片沟槽ft的侧壁及底表面。在一些实施例中,栅极介电层144与下伏栅电极142a或142c可统称为栅极结构g1或g2。随后,在栅极介电层144上共形地形成界面层146。随后,形成半导体鳍片148以填充鳍片沟槽ft且由栅极介电层144及界面层146包覆,如图16c所示。形成半导体鳍片148的方法可包括在隔离介电质104上方沉积半导体材料且填充鳍片沟槽ft,可选地执行平坦化制程,诸如化学机械研磨(chemical mechanical polish,cmp)制程,以移除鳍片沟槽ft之外的多余的半导体鳍片148、栅极介电层144、及界面层146,且形成如图16a至图16c中所示的结构。在一些实施例中,半导体材料可通过沉积制程形成,诸如化学气相沉积(chemical vapor deposition,cvd)、熔炉(lpcvd)、原子层沉积(atomic layer deposition,ald)、电浆增强cvd(plasma enhanced cvd,pecvd)或其他适合技术。在一些实施例中,可在约300℃至约600℃(例如,约300、350、400、450、500、550、或600℃)范围内的温度下执行沉积制程。选择沉积制程的温度及其他制程条件,以允许在栅电极材料、通孔材料及介电材料上形成半导体材料。在一些实施例中,半导体鳍片可通过在鳍片沟槽ft中沉积非晶半导体材料(例如,非晶硅)来形成,后续使用例如rta(快速热退火)将非晶半导体材料结晶成单晶半导体材料(例如,单晶硅)。

275.在一些实施例中,半导体鳍片148可包括硅、硅锗(si

x

ge

1-x

,其中x可在约0与1之

间)、碳化硅、锗、iii-v化合物半导体、ii-vi化合物半导体、或类似物。举例而言,用于形成iii-v化合物半导体的可用材料包括但不限于inas、alas、gaas、inp、gan、ingaas、inalas、gasb、alsb、alp、gap、或类似物。

276.在一些实施例中,栅极介电层144可包括例如高k介电材料,例如金属氧化物、金属氮化物、金属硅酸盐、过渡金属氧化物、过渡金属氮化物、过渡金属硅酸盐、金属氧氮化物、金属铝酸盐、硅酸锆、铝酸锆、或其组合物。在一些实施例中,栅极介电层144可包括氧化铪(hfo2)、氧化硅铪(hfsio)、氧氮化硅铪(hfsion)、氧化钽铪(hftao)、氧化钛铪(hftio)、氧化锆铪(hfzro)、氧化镧(lao)、氧化锆(zro)、氧化钛(tio)、氧化钽(ta2o5)、氧化钇(y2o3)、氧化钛锶(srtio3,sto)、氧化钛钡(batio3,bto)、氧化锆钡(bazro)、氧化镧铪(hflao)、氧化硅镧(lasio)、氧化硅铝(alsio)、氧化铝(al2o3)、氮化硅(si3n4)、硅氧氮化物(sion)、及其组合物。在一些实施例中,界面层146可包括诸如氧化硅。在一些实施例中,界面层146可由与栅极介电层144不同的材料制成。

277.返回参考图1b,方法m1接着进行至方块s116,其中隔离介电质凹陷至半导体鳍片的顶表面之下。参考图17,在方块s116的一些实施例中,隔离介电质104凹陷至半导体鳍片148的顶表面之下。在使隔离介电质104凹陷之后,半导体鳍片148突出于隔离介电质104。换言之,半导体鳍片148的上部部分高于隔离介电质104的顶表面。在一些实施例中,执行的蚀刻制程可是湿式蚀刻制程。作为实例但不限制本揭露地,可使用稀hf、siconi(包括hf及nh3)、或类似物(可用作蚀刻剂)来执行湿式蚀刻制程。在替代实施例中,蚀刻制程可是干式蚀刻制程。作为实例但不限制本揭露地,干式蚀刻制程可使用cf4、c4f6、及/或c4f8作为蚀刻气体来执行。

278.返回参考图1b,方法m1接着进行至方块s117,其中形成至少一个虚设栅极结构以延伸跨越半导体鳍片。参考图18a至图18c,在方块s117的一些实施例中,形成虚设栅极结构152a及152c以延伸穿过半导体鳍片148。这将参考图18a至图18c更详细地描述,栅极介电层毯覆形成于基材101上方以覆盖半导体鳍片148及隔离介电质104,且虚设栅电极层形成于栅极介电层上方。

279.在一些实施例中,栅极介电层由高k介电材料制成,诸如金属氧化物、过渡金属氧化物、或类似物。高k介电材料的实例包括但不限于氧化铪(hfo2)、氧化硅铪(hfsio)、氧化钽铪(hftao)、氧化钛铪(hftio)、氧化锆铪(hfzro)、氧化锆、氧化钛、氧化铝、氧化铪氧化铝(hfo

2-al2o3)合金、或其他适用的介电材料。在一些实施例中,栅极介电层可是氧化层。栅极介电层可通过沉积制程形成,诸如化学气相沉积(chemical vapor deposition,cvd)、物理气相沉积(physical vapor deposition,pvd)、原子层沉积(atomic layer deposition,ald)、电浆增强化学气相沉积(plasma enhanced cvd,pecvd)或其他适合的技术。在一些实施例中,虚设栅电极层可包括多晶硅(聚si)、多晶硅锗(聚sige)、金属氮化物、金属硅化物、金属氧化物、或金属。在一些实施例中,虚设栅电极层可包括含金属材料,诸如tin、tan、tac、co、ru、al、其组合物、或其多层。虚设栅电极层可通过cvd、物理气相沉积(physical vapor deposition,pvd)、溅射沉积、或其他适于沉积导电材料的技术来沉积。

280.随后,在虚设栅电极层上方形成经图案化遮罩层(未显示)且接着图案化以形成分离的遮罩部分。经图案化遮罩层可通过一系列操作形成,包括沉积、光学微影术图案化、及蚀刻制程。光学微影术图案化制程可包括光阻剂涂布(例如,旋装涂布)、软烘烤、遮罩对准、

曝光、曝光后烘烤、显影光阻剂、冲洗、干燥(例如,硬烘烤)、及/或其他适用制程。蚀刻制程可包括干式蚀刻、湿式蚀刻、及/或其他蚀刻方法(例如,反应离子蚀刻)。如图18c中所示,使用经图案化遮罩作为蚀刻遮罩,执行一或多个蚀刻制程以形成绕半导体鳍片148包覆的虚设栅极结构152a及152c,且在蚀刻之后移除经图案化遮罩层。当在如图18a中所示的俯视图中观察时,各个虚设栅极结构152a及152c包括栅极介电层及栅极介电层上方的虚设栅电极层。如图18a中所示,虚设栅极结构152a及152c具有基本上平行的纵轴,该纵轴基本上垂直于半导体鳍片148的纵轴。使用“后栅极”或替换栅极制程,将虚设栅极结构152a及152c替换为替换栅极结构。

281.返回参考图1b,方法m1接着进行至方块s118,其中第二栅极间隔物沿虚设栅极结构的侧壁形成。参考图19,在方块s118的一些实施例中,栅极间隔物154沿假栅极结构152a及152c的侧壁形成。在一些实施例中,栅极间隔物154可包括氧化硅、氮化硅、氧氮化硅、碳化硅、碳氮化硅、氧碳氮化硅、氧碳化硅、多孔介电材料、掺氢氧碳化硅(sioc:h)、低k介电材料、或其他适合的介电材料。栅极间隔物154可包括由不同介电材料制成的单层或多层结构。形成栅极间隔物154的方法包括使用例如cvd、ald、或peald在图18a至图18c中所示的结构上毯覆形成介电层,且接着执行诸如各向异性蚀刻的蚀刻制程以移除介电层的水平部分。虚设栅极结构152a及152c的侧壁上的介电层的剩余部分可用作栅极间隔物154。在一些实施例中,栅极间隔物154可用于偏移后续形成的掺杂区,例如源极/漏极区。栅极间隔物154可进一步用于设计或修改源极/漏极区轮廓。

282.返回参考图1b,方法m1接着进行至方块s119,其中源极/漏极开口形成于半导体鳍片中。参考图20,在方块s119的一些实施例中,移除未由虚设栅极结构152a及152c以及栅极间隔物154覆盖的半导体鳍片148的部分,以形成源极/漏极开口148r,从而曝光源极/漏极触点123b及123c。在一些实施例中,源极/漏极开口148r通过使用光学微影术及蚀刻制程形成。蚀刻制程可包括干式蚀刻制程、湿式蚀刻制程、或组合干式及湿式蚀刻制程。作为实例但不限制本揭露地,这个蚀刻制程可包括使用虚设栅极结构152a及152c以及栅极间隔物154作为遮罩的反应离子蚀刻(reactive ion etch,rie),或通过任何其他适合的移除制程。在一些实施例中,在蚀刻制程之后,可执行预清洗制程以用氢氟酸(hf)或其他适合的溶液清洗源极/漏极开口148r。

283.返回参考图1c,方法m1接着进行至方块s120,其中在源极/漏极开口中形成磊晶源极/漏极结构。参考图21,在方块s120的一些实施例中,磊晶源极/漏极结构158b及158c分别形成于源极/漏极开口148r中。因此,栅极结构g1与栅极结构g1相对侧上的源极/漏极结构(如图38中所示,栅极结构g82/g85相对侧上的磊晶源极/漏极结构858b及858c)共同形成第一晶体管s1,栅极结构g2与栅极结构g2相对侧上的源极/漏极结构共同形成第二晶体管s2,栅极结构152a与栅极结构152a相对侧上的源极/漏极结构共同形成第三晶体管s3,且栅极结构152c与栅极结构152c相对侧上的源极/漏极结构形成第四晶体管s4。这将参考图38至图39更详细地描述,第一晶体管s1与第三晶体管s3共享半导体鳍片148的第一通道区及磊晶源极/漏极结构158b,第二及第四晶体管s2及s4共享半导体鳍片148的第二通道区及磊晶源极/漏极结构158c。

284.尽管在如图18a至图27中所示的图示实施例中,磊晶源极/漏极结构158b及158c在虚设栅极形成之后形成,但在其他一些实施例中,磊晶源极/漏极结构158b及158c可在虚设

栅极形成之前形成于半导体鳍片148中。

285.磊晶源极/漏极结构158b及158c可使用一或多个磊晶生长或磊晶(epi)制程形成,使得可在半导体鳍片148上以结晶状态形成si特征、sige特征、磷酸硅(sip)特征、碳化硅(sic)特征及/或其他适合的特征。在一些实施例中,磊晶源极/漏极结构158b及158c的晶格常数不同于半导体鳍片148的晶格常数,使得相邻于磊晶源极/漏极结构158b及158c的通道区可由磊晶源极/漏极结构158b及158c施加应变或应力,以提高半导体装置的载流子移动率且增强装置性能。

286.磊晶制程包括化学气相沉积技术(例如,气相磊晶(vapor-phase epitaxy,vpe)及/或超高真空cvd(ultra-high vacuum cvd,uhv-cvd))、分子束磊晶、及/或其他适合制程。磊晶制程可使用与半导体鳍片148的组合物(例如,硅、硅锗、磷酸硅、或类似物)相互作用的气体及/或液体前驱物。磊晶源极/漏极结构158b及158c可经原位掺杂。掺杂种类包括p型掺杂剂,诸如硼或bf2;n型掺杂剂,诸如磷或砷;以及/或其他适合的掺杂剂,包括其组合物。若磊晶源极/漏极结构158a及158c非原位掺杂,则执行布植制程以掺杂磊晶源极/漏极结构158b及158c。可执行一或多个退火制程来活化磊晶源极/漏极结构158b及158c。退火制程包括快速热退火(rapid thermal annealing,rta)及/或激光退火制程。

287.在源极/漏极触点123b及123c上形成磊晶源极/漏极结构158b及158c之后,执行一或多个退火步骤以引起磊晶源极/漏极结构158b及158c的半导体材料与源极/漏极触点123b及123c的金属材料之间的反应,从而在磊晶源极/漏极结构158b及158c与源极/漏极触点123b及123c之间形成硅化物层156b及156c。硅化制程使金属与硅(或多晶硅)发生反应。第一快速热退火(rapid thermal annealing,rta)制程可在例如ar、he、n2或其他惰性气氛中在第一温度(诸如低于约200~300℃)下执行,以将源极/漏极触点123b及123c的金属材料转化成金属硅化物。后续在高于第一温度的第二温度(诸如约400~500℃)下进行第二退火或快速热退火步骤,从而形成具有低电阻的稳定硅化物层156b及156c。在一些实施例中,硅化物层156b及156c可包括硅化钛(tisi)、硅化镍(nisi)、硅化钴(cosi)、ni-pt、或其组合物。

288.返回参考图1c,方法m1接着进行至方块s121,其中在磊晶源极/漏极结构上方形成接触蚀刻终止层(contact etch stop layer,cesl)及第二介电层。参考图22,在方块s121的一些实施例中,在磊晶源极/漏极结构158b及158c、虚设栅极结构152a及152c以及栅极间隔物154上方形成接触蚀刻终止层(contact etch stop layer,cesl)162,且在接触蚀刻终止层162上方形成介电层164,随后,执行cmp制程以移除介电层164及接触蚀刻终止层162的多余材料,从而曝光虚设栅极结构152a及152c以及栅极间隔物154。cmp制程可将介电层164的顶表面与虚设栅极结构152a及152c以及栅极间隔物154的顶表面平坦化。在一些实施例中,介电层164包括氧化硅、氮化硅、氧氮化硅、四乙氧基硅烷(teos)氧化物、磷硅玻璃(psg)、硼磷硅玻璃(bpsg)、低k介电材料、及/或其他适合的介电材料。低k介电材料的实例包括但不限于氟硅酸盐玻璃(fsg)、掺碳氧化硅。介电层164可使用例如cvd、ald、旋装玻璃(sog)或其他适合的技术形成。在一些实施例中,接触蚀刻终止层162可包括氮化硅、氧氮化硅或其他适合材料。接触蚀刻终止层162可使用例如电浆增强cvd、低压cvd、ald或其他适合的技术形成。

289.返回参考图1c,方法m1接着进行至方块s122,其中移除虚设栅极结构以在第二栅

极间隔物之间形成第二栅极沟槽。参考图23,在方块s122的一些实施例中,移除虚设栅极结构152a及152c(如图22中所示),以形成栅极沟槽gt3及gt4,其中栅极间隔物154作为其侧壁。换言之,栅极沟槽gt3及gt4各形成于栅极间隔物154之间。栅极沟槽gt3及gt4的宽度与图22中所示的相应虚设栅极结构152a及152c相关联。在一些实施例中,通过执行第一蚀刻制程及在第一蚀刻制程之后执行第二蚀刻制程来移除虚设栅极结构152a及152c。在一些实施例中,虚设栅极结构152a及152c的虚设栅电极层主要通过第一蚀刻制程移除,且虚设栅极结构152a及152c的栅极介电层主要通过第二蚀刻制程移除,第二蚀刻制程采用与第一蚀刻制程中使用的蚀刻剂不同的蚀刻剂。在一些实施例中,移除虚设栅极结构152a及152c的虚设栅电极层,而虚设栅极结构152a及152c的栅极介电层保留于栅极沟槽gt3及gt4中。

290.返回参考图1c,方法m1接着进行至方块s123,其中在第二栅极沟槽中形成上部晶体管的上部栅极结构。参考图24,在方块s123的一些实施例中,替换栅极结构g3及g4分别形成于栅极沟槽gt3及gt4中(如图23中所示)。在图24中,第三晶体管s3的栅极结构g3与第一晶体管s1的栅极结构g1重叠,且第四晶体管s4的栅极结构g4与第二晶体管s2的栅极结构g2重叠。形成这些替换栅极结构的例示性方法可包括在基材101上方毯覆形成栅极介电层172,在毯覆栅极介电层上方形成一或多个功函数金属层,且在一或多个功函数金属层上方形成填充金属层,及执行cmp制程以移除栅极沟槽gt3及gt4之外的填充金属层、一或多个功函数金属层及栅极介电层172的多余材料。作为这个方法的结果,替换栅极结构g3及g4各包括栅极介电层172及由栅极介电层172围绕包覆的金属栅电极174。

291.在一些实施例中,栅极介电层172可包括例如高k介电材料,诸如金属氧化物、金属氮化物、金属硅酸盐、过渡金属氧化物、过渡金属氮化物、过渡金属硅酸盐、金属氧氮化物、金属铝酸盐、硅酸锆、铝酸锆、或其组合物。在一些实施例中,栅极介电层172可包括氧化铪(hfo2)、氧化硅铪(hfsio)、氧氮化硅铪(hfsion)、氧化钽铪(hftao)、氧化钛铪(hftio)、氧化锆铪(hfzro)、氧化镧(lao)、氧化锆(zro)、氧化钛(tio)、氧化钽(ta2o5)、氧化钇(y2o3)、氧化钛锶(srtio3,sto)、氧化钛钡(batio3,bto)、氧化锆钡(bazro)、氧化镧铪(hflao)、氧化硅镧(lasio)、氧化硅铝(alsio)、氧化铝(al2o3)、氮化硅(si3n4)、硅氧氮化物(sion)、及其组合物。在替代实施例中,栅极介电层172可具有多层结构,诸如一层氧化硅(例如,界面层)及另一层高k材料。在一些实施例中,栅极介电层172由相同的材料制成,因为它们由毯覆沉积于基材101上方的相同介电层形成。

292.金属栅电极174可包括适合的功函数金属,以提供适合的功函数。在一些实施例中,金属栅电极174可包括用于在基材101上形成n型晶体管的一或多种n型功函数金属(n型金属)。n型功函数金属可例示性地包括但不限于钛铝(tial)、氮化铝钛(tialn)、氮化碳钽(tacn)、铪(hf)、锆(zr)、钛(ti)、钽(ta)、铝(al)、金属碳化物(例如碳化铪(hfc)、碳化锆(zrc)、碳化钛(tic)、碳化铝(alc))、铝化物、及/或其他适合的材料。在替代实施例中,金属栅电极260可包括用于在基材101上形成p型晶体管的一或多种p型功函数金属(p型金属)。p型功函数金属可例示性地包括但不限于氮化钛(锡)、氮化钨(wn)、钨(w)、钌(ru)、钯(pd),铂(pt)、钴(co)、镍(ni)、导电金属氧化物、及/或其他适合材料。金属栅电极174中的至少两者由不同的功函数金属制成,以便在一些实施例中达成适合的功函数。在一些实施例中,金属栅电极174的整体是功函数金属。

293.返回参考图1c,方法m1接着进行至方块s124,其中在上部栅极结构上执行金属栅

极回蚀(metal gate etch back,mgeb)制程,以薄化上部栅极结构。参考图25,在方块s124的一些实施例中,mgeb制程可是电浆蚀刻制程,且驱动电浆以缩小栅极结构g3及g4。在一些实施例中,mgeb制程使用cl2、o2、bcl3、及ar的气体混合物,其偏置范围为约25v至约1200v。

294.返回至图1b,方法m1接着进行至方块s125,其中在栅极结构上方形成介电帽。参考图26,在方块s125的一些实施例中,使用例如沉积制程在基材101上方沉积介电材料、接着通过cmp制程移除栅极沟槽gt3及gt4之外的多余介电材料来在栅极结构g3及g4上方形成介电帽176。在一些实施例中,介电帽176可包括氮化硅或其他适合的介电材料。在一些实施例中,介电帽176具有不同于栅极间隔物154、接触蚀刻终止层162、及/或介电层164的蚀刻选择性。举例而言,若介电帽176为sin,则栅极间隔物154、接触蚀刻终止层162、及/或介电层164为不同于sin的介电材料。在一些实施例中,介电帽176可用于界定自对准接触区域,且因此称为sac结构或sac层。

295.返回参考图1c,方法m1接着进行至方块s126,其中在磊晶源极/漏极结构上形成上部源极/漏极触点,在上部栅极结构及上部源极/漏极触点上形成上部栅极通孔及上部源极/漏极通孔,及/或在上部晶体管的上部源极/漏极触点及上部栅极结构上形成上部抵接触点。参考图27,在方块s126的一些实施例中,源极/漏极触点183b及183c穿过介电层164及接触蚀刻终止层162形成,以着陆于磊晶源极/漏极结构158b及158c上。源极/漏极触点183b及183c的例示性形成方法可包括通过一或多个蚀刻制程形成接触孔,从而依序蚀刻穿过介电层164向下至个别磊晶源极/漏极结构158b及158c,及通过沉积制程在接触孔中沉积金属或其他适合的导电材料,以形成源极/漏极触点183b及183c。在一些实施例中,源极/漏极触点183b及183c可包括钨(w)、铝(al)、铜(cu)、钴(co)、另一适合的导电材料、或其组合物。

296.在一些实施例中,在源极/漏极触点沉积制程之前,通过硅化制程在磊晶源极/漏极结构158b及158c上形成硅化物层186b及186c。随后,在硅化物层186b及186c上分别形成源极/漏极触点183b及183c。举例而言,硅化制程使金属与硅(或多晶硅)之间进行反应。第一快速热退火(rapid thermal annealing,rta)制程可在例如ar、he、n2或其他惰性气氛中在第三温度(诸如低于200~300℃)下执行,以将金属材料转化成金属硅化物。后续在高于第三温度的第四温度(例如400~500℃)下进行第二退火或rta步骤,从而形成具有低电阻的稳定硅化物层186b及186c。在一些实施例中,硅化物层186b及186c可包括硅化钛(tisi)、硅化镍(nisi)、硅化钴(cosi)、ni-pt、或其组合物。

297.介电层165沉积于栅极结构g3及g4上方。至栅极结构g3及源极/漏极触点183b的通孔开口形成于介电层165中。至栅极结构g4及源极/漏极触点183c的抵接触点开口亦形成于介电层165中。在一些实施例中,在介电层165上形成光阻剂层(未显示),且接着经图案化以界定抵接触点开口及触点开口的位置。接着根据经图案化光阻剂层蚀刻介电层165以形成抵接触点开口及触点开口。

298.随后,可使用金属沉积制程在抵接触点开口及触点开口中填充导电接触材料,诸如铜、钴、钛、钽、钨、铝、或其合金。可在半导体基材上应用诸如化学机械研磨(chemical mechanical polish,cmp)制程的平坦化制程,以移除介电层165上的多余金属形成物,金属形成物的剩余部分可用作抵接触点193c、源极/漏极通孔193b、及栅极通孔193a。抵接触点193c的第一部分着陆于替换栅电极g4上,且抵接触点193c的第二部分着陆于源极/漏极触点183c上。

299.返回参考图1c,方法m1接着进行至方块s127,其中上部互连结构形成于上部栅极通孔、上部源极/漏极通孔、及/或上部抵接触点上方。参考图28,在方块s127的一些实施例中,在晶体管形成之后形成互连结构196。互连结构196包括例如标记为m0至m6的七个金属化层、及标记为v1至v6的六个层的金属化通孔或互连件。其他实施例可含有更多或更少的金属化层及相应的更多或更少数目的通孔。此处所示的金属线仅作为实例,金属线可以其他方式定向(旋转90度或以其他定向)。集成电路结构100包括全金属化堆叠,包括通过互连件v1~v6连接的金属化层m0~m6中的各者的一部分,其中m0将堆叠连接至晶体管的源极/漏极触点。集成电路中亦包括多个imd层。图28中描绘了六个imd层,标识为imd1至imd6。imd层可为集成电路的各种功能提供电绝缘以及结构支撑。

300.图29a及图29b示出了根据一些其他实施例的集成电路结构200沿着图18a中所示的线b-b'及线d-d'的横截面图。用于形成本实施例的集成电路结构200的操作与在与图2至图28相关联的前述描述中所描述的用于形成集成电路结构100的操作基本相同,且因此为了清楚起见,此处不再重复。举例而言,与基材201、互连结构202及296、第一半导体鳍片248a及第二半导体鳍片248b、栅极结构g21、g22、g23、及g24、磊晶源极/漏极结构258b、258c、258d、及258e、晶体管s21、s22、s23、及s24、栅极通孔213a及293a、源极/漏极触点223b、223c、283b、及283c、源极/漏极通孔213b及293b、抵接触点213c及293c、硅化物层256b、256c、286b、及286c、栅极间隔物230及254、介电层203及265、及接触蚀刻终止层262有关的材料及制造制程可与如图2至图28中所示的基材101、互连结构102及196、半导体鳍片148、栅极结构g1、g2、g3、及g4、磊晶源极/漏极结构158b及158c、晶体管s1、s2、s3、及s4、栅极通孔113a及193a、硅化物层156b、156c、186b、及186c、源极/漏极触点123b、123c、183b、及183c、源极/漏极通孔113b及193b、抵接触点113c及193c、栅极间隔物130及154、介电层103及165、及接触蚀刻终止层162的基本相同。因此,相关详细说明可参考前述段落,且此处不再描述。

301.本实施例与图2至图28中的实施例之间的区别在于,用于上部晶体管s23及s24的上部源极/漏极通孔293b、上部源极/漏极触点283b及283c、及上部抵接触点293c形成于如图29a中所示的第一半导体鳍片248a中磊晶源极/漏极结构258b及258c上,且用于下部晶体管s21及s22的下部源极/漏极触点213b、下部源极/漏极触点223b及223c、及下部抵接触点213c形成于第二半导体鳍片248b中磊晶源极/漏极结构258d及258e上,而非如图29b中所示的第一半导体鳍片248a上。在一些实施例中,如图29a中所示的第一半导体鳍片248a中磊晶源极/漏极结构258b可与如图29b中所示的第二半导体鳍片248b中磊晶源极/漏极结构258d合并,及/或如图29a中所示的第一半导体鳍片248a中磊晶源极/漏极结构258c可与如图29b中所示的第二半导体鳍片248b中磊晶源极/漏极结构258e合并。在一些实施例中,如图29a中所示的第一半导体鳍片248a中磊晶源极/漏极结构258b与如图29b中所示的第二半导体鳍片248b中磊晶源极/漏极结构258d侧向间隔开,及/或如图29a中所示的第一半导体鳍片248a中磊晶源极/漏极结构258c与如图29b中所示的第二半导体鳍片248b中磊晶源极/漏极结构258e侧向间隔开。

302.图30a及图30b示出了根据一些其他实施例的集成电路结构300沿着图18a中所示的线b-b'及线d-d'的横截面图。用于形成本实施例的集成电路结构300的操作与在与图2至图28相关联的前述描述中所描述的用于形成集成电路结构100的操作基本相同,且因此为

了清楚起见,此处不再重复。举例而言,与基材301、互连结构302及396、第一半导体鳍片348a及第二半导体鳍片348b、栅极结构g32、g33、及g34、磊晶源极/漏极结构358b、358c、358d、及358e、栅极通孔393a、源极/漏极触点323b、323c、383b、及383c、源极/漏极通孔313b及393b、抵接触点313c及393c、硅化物层356b、356c、386b、及386c、栅极间隔物330及354、介电层303及365、及接触蚀刻终止层362相关的材料及制造制程可与如图2至图28中所示的基材101、互连结构102及196、半导体鳍片148、栅极结构g2、g3、及g4、磊晶源极/漏极结构158b及158c、栅极通孔193a、硅化物层156b、156c、186b、及186c、源极/漏极触点123b、123c、183b、及183c、源极/漏极通孔113b及193b、抵接触点113c及193c、栅极间隔物130及154、介电层103及165、及接触蚀刻终止层162的基本相同。因此,相关详细说明可参考前述段落,且此处不再描述。

303.本实施例与图2至图28中的实施例之间的区别在于,在本实施例中省略了图2至图28中所示的下部栅极结构g1及下部栅极通孔113a,且因此上部栅极结构g33可控制图30a中所示的与上部互连结构396电连接的第一半导体鳍片348a中的通道区,且可同时控制图30b中所示的与下部互连结构302电连接的第二半导体鳍片348b中的通道区。

304.此外,如图30a中所示,上部源极/漏极通孔393b及上部源极/漏极触点383b形成于第一半导体鳍片348a中磊晶源极/漏极结构358b上,且下部源极/漏极触点313b及下部源极/漏极触点323b形成于第二半导体鳍片348b中磊晶源极/漏极结构358d上而非第一半导体鳍片348a上,如图30b中所示。在一些实施例中,如图30a中所示的第一半导体鳍片348a中磊晶源极/漏极结构358b可与如图30b中所示的第二半导体鳍片348b中磊晶源极/漏极结构358d合并,及/或如图30a中所示的第一半导体鳍片348a中磊晶源极/漏极结构358c可与如图30b中所示的第二半导体鳍片348b中磊晶源极/漏极结构358e合并。在一些实施例中,如图30a中所示的第一半导体鳍片348a中磊晶源极/漏极结构358b与如图30b中所示的第二半导体鳍片348b中磊晶源极/漏极结构358d侧向间隔开,及/或如图30a中所示的第一半导体鳍片348a中磊晶源极/漏极结构358c与如图30b中所示的第二半导体鳍片348b中磊晶源极/漏极结构358e侧向间隔开。

305.图31a及图31b示出了对应于图28的集成电路结构400及沿图18a中所示的线b-b'及线d-d'的横截面图。用于形成本实施例的集成电路结构400的操作与在与图2至图28相关联的前述描述中所描述的用于形成集成电路结构100的操作基本相同,且因此为了清楚起见,此处不再重复。举例而言,与基材401、互连结构402及496、半导体鳍片448a及448b、栅极结构g41、g42、及g44、磊晶源极/漏极结构458b、458c、458d、及458e、栅极通孔413a、源极/漏极触点423b、423c、483b、及483c、源极/漏极通孔413b及493b、抵接触点413c及493c、硅化物层456b、456c、486b、及486c、栅极间隔物430及454、介电层403及465、及接触蚀刻终止层462相关的材料及制造制程可与如图2至图28中所示的基材101、互连结构102及196、半导体鳍片148、栅极结构g1、g2、及g4、磊晶源极/漏极结构158b及158c、栅极通孔113a、硅化物层156b、156c、186b、及186c、源极/漏极触点123b、123c、183b、及183c、源极/漏极通孔113b及193b、抵接触点113c及193c、栅极间隔物130及154、介电层103及165、及接触蚀刻终止层162的基本相同。因此,相关详细说明可参考前述段落,且此处不再描述。

306.本实施例与图2至图28中的实施例之间的区别在于,在本实施例中省略了图2至图28中所示的上部栅极结构g3及上部栅极通孔193a,且因此下部栅极结构g41可控制图31a中

所示的与下部互连结构402电连接的第一半导体鳍片448a中的通道区,且可同时控制图31b中所示的与上部互连结构496电连接的第二半导体鳍片448b中的通道区。

307.此外,如图31a中所示,下部源极/漏极通孔413b及下部源极/漏极触点423b形成于第一半导体鳍片448a中磊晶源极/漏极结构458b上,且上部源极/漏极触点493b及上部源极/漏极触点483b形成于第二半导体鳍片448b中磊晶源极/漏极结构458d上而非第一半导体鳍片448a上,如图31b中所示。在一些实施例中,如图31a中所示的第一半导体鳍片448a中磊晶源极/漏极结构458b可与如图31b中所示的第二半导体鳍片448b中磊晶源极/漏极结构458d合并,及/或如图31a中所示的第一半导体鳍片448a中磊晶源极/漏极结构458c可与如图31b中所示的第二半导体鳍片448b中磊晶源极/漏极结构458e合并。在一些实施例中,如图31a中所示的第一半导体鳍片448a中磊晶源极/漏极结构458b与如图31b中所示的第二半导体鳍片448b中磊晶源极/漏极结构458d侧向间隔开,及/或如图31a中所示的第一半导体鳍片448a中磊晶源极/漏极结构458c与如图31b中所示的第二半导体鳍片448b中磊晶源极/漏极结构458e侧向间隔开。

308.图32a至图32b示出了对应于图28的集成电路结构500且沿图18a中所示的线b-b'及线d-d'的横截面图。用于形成本实施例的集成电路结构500的操作与在与图2至图28相关联的前述描述中所描述的用于形成集成电路结构100的操作基本相同,且因此为了清楚起见,此处不再重复。举例而言,与基材501、互连结构502及596、半导体鳍片548a及548c、栅极结构g51、g52、g53、及g54、磊晶源极/漏极结构558b、558c、558d、及558e、晶体管s51、s52、s53、及s54、栅极通孔513a及593a、源极/漏极触点523b、523c、583b、及583c、源极/漏极通孔513b及593b、抵接触点513c及593c、硅化物层556b、556c、586b、及586c、栅极间隔物530及554、介电层503及565、及接触蚀刻终止层562相关的材料及制造制程可与如图2至图28中所示的基材101、互连结构102及196、半导体鳍片148、栅极结构g1、g2、g3、及g4、磊晶源极/漏极结构158b及158c、晶体管s1、s2、s3、及s4、栅极通孔113a及193a、硅化物层156b、156c、186b、及186c、源极/漏极触点123b、123c、183b、及183c、源极/漏极通孔113b及193b、抵接触点113c及193c、栅极间隔物130及154、介电层103及165、及接触蚀刻终止层162的基本相同。因此,相关详细说明可参考前述段落,且此处不再描述。

309.本实施例与图2至图28中的实施例之间的区别在于,图32a中所示的上部栅极结构g53沿与图32b中所示的上部晶体管s51的下部栅极结构g51相同的方向延伸,且与下部栅极结构g51不重叠。或者,图32a中所示的上部晶体管s54的上部栅极结构g54沿与图32b中所示的上部晶体管s52的下部栅极结构g52相同的方向延伸,且与下部栅极结构g52不重叠。

310.此外,如图32a中所示,上部晶体管s53及s54的上部源极/漏极触点593b、上部源极/漏极触点583b及583c、及上部抵接触点593c形成于第一半导体鳍片548a中磊晶源极/漏极结构558b及558c上,且下部晶体管s51及s52的下部源极/漏极触点513b、下部源极/漏极触点523b及523c、及下部抵接触点513c形成于第三半导体鳍片548c中磊晶源极/漏极结构558d及558e上而非第一半导体鳍片548a上,如图32b中所示。在一些实施例中,如图32a中所示的第一半导体鳍片548a中磊晶源极/漏极结构558b可与如图32b中所示的第三半导体鳍片548c中磊晶源极/漏极结构558d合并,及/或如图32a中所示的第一半导体鳍片548a中磊晶源极/漏极结构558c可与如图32b中所示的第三半导体鳍片548c中磊晶源极/漏极结构558e合并。在一些实施例中,如图32a中所示的第一半导体鳍片548a中磊晶源极/漏极结构

558b与如图32b中所示的第三半导体鳍片548c中磊晶源极/漏极结构558d侧向间隔开,及/或如图32a中所示的第一半导体鳍片548a中磊晶源极/漏极结构558c与如图32b中所示的第三半导体鳍片548c中磊晶源极/漏极结构558e侧向间隔开。

311.现在参考图33a至图33c,示出了根据一些实施例的用于制造集成电路结构的例示性方法m2的流程图。方法m2包括整个制造制程的相关部分。应理解,可在图33a至图33c中所示的操作之前、期间、及之后提供额外操作,且对于该方法的额外实施例,可替换或消除下面描述的一些操作。操作/制程的次序可互换。方法m2包括制造集成电路结构。然而,集成电路结构的该制造仅是用于描述根据本揭露的一些实施例的制造制程的实例。

312.图34至图36示出了根据本揭露的一些实施例的在形成集成电路结构600的各个阶段中的方法m2。在本实施例的图34之前,用于形成集成电路结构600的方法m2的方块s201~s215与图2至图16c相关联的前述描述中所描述的用于形成集成电路结构100的方法m1的方块s201~s215基本相同,且因此为了清楚起见,此处不再重复。举例而言,与基材601、互连结构602、半导体鳍片648a、栅极结构g61及g62、栅极通孔613a、源极/漏极触点623b及623c、源极/漏极通孔613b、抵接触点613c、栅极间隔物630、及介电层603相关的材料及制造制程可与如图2至图16c中所示的基材101、互连结构102及196、半导体鳍片148、栅极结构g1及g2、栅极通孔113a、源极/漏极触点123b及123c、源极/漏极通孔113b、抵接触点113c、栅极间隔物130、及介电层103的基本相同。因此,相关详细描述可参考前述段落,且在此不再描述。

313.返回参考图33b,方法m2接着进行至方块s216,其中源极/漏极开口形成于下部半导体鳍片中。参考图34,在方块s216的一些实施例中,移除半导体鳍片648a的部分以形成源极/漏极开口648r,从而曝光源极/漏极触点623b及623c。在一些实施例中,源极/漏极开口648r通过使用光学微影术及蚀刻制程形成。蚀刻制程可包括干式蚀刻制程、湿式蚀刻制程、或组合干式及湿式蚀刻制程。作为实例但不限制本揭露地,该蚀刻制程可包括反应离子蚀刻(reactive ion etch,rie)或通过任何其他适合的移除制程。在一些实施例中,在蚀刻制程之后,可执行预清洗制程以用氢氟酸(hf)或其他适合的溶液来清洗源极/漏极开口648r。

314.返回参考图33b,方法m2接着进行至方块s217,其中在第一源极/漏极开口中形成下部磊晶源极/漏极结构。参考图34,在方块s217的一些实施例中,磊晶源极/漏极结构658b及658c分别形成于源极/漏极开口648r中。因此,栅极结构g61与栅极结构g61相对侧上的源极/漏极结构共同形成第一晶体管s61(如图38中所示,栅极结构g82/g85相对侧上的磊晶源极/漏极结构858b及858c),且栅极结构g62与栅极结构g62的相对侧上的源极/漏极结构共同形成第二晶体管s62。

315.磊晶源极/漏极结构658b及658c可使用一或多个磊晶生长或磊晶(epi)制程形成,使得可在半导体鳍片648a上以结晶状态形成si特征、sige特征、磷酸硅(sip)特征、碳化硅(sic)特征及/或其他适合特征。在一些实施例中,磊晶源极/漏极结构658b及658c的晶格常数不同于半导体鳍片648a的晶格常数,因此磊晶源极/漏极结构658b与658c之间的通道区可由磊晶源极/漏极结构658b及658c施加应变或应力,以提高半导体装置的载流子移动率且增强装置性能。

316.磊晶制程包括cvd沉积技术(例如,气相磊晶(vapor-phase epitaxy,vpe)及/或超高真空cvd(ultra-high vacuum cvd,uhv-cvd))、分子束磊晶、及/或其他适合制程。磊晶制程可使用与半导体鳍片648a的组合物(例如,硅、硅锗、磷酸硅、或类似物)相互作用的气体

及/或液体前驱物。磊晶源极/漏极结构658b及658c可经原位掺杂。掺杂种类包括p型掺杂剂,如硼或bf2;n型掺杂剂,如磷或砷;以及/或其他适合的掺杂剂,包括其组合物。若磊晶源极/漏极结构658b及658c未原位掺杂,则执行布植制程以掺杂磊晶源极/漏极结构658b及658c。可执行一或多个退火制程来活化磊晶源极/漏极结构658b及658c。退火制程包括快速热退火(rapid thermal annealing,rta)及/或激光退火制程。

317.在源极/漏极触点623b及623c上形成磊晶源极/漏极结构658b及658c之后,执行一或多个退火步骤以引起磊晶源极/漏极结构658b及658c的半导体材料与源极/漏极触点623b及623c的金属材料之间的反应,从而在磊晶源极/漏极结构658b及658c与源极/漏极触点623b及623c之间形成硅化物层656b及656c。硅化制程使金属与硅(或多晶硅)发生反应。第一快速热退火(rapid thermal annealing,rta)制程可在例如ar、he、n2或其他惰性气氛中在第一温度(诸如低于约200~300℃)下执行,以将源极/漏极触点623b及623c的金属材料转化成金属硅化物。后续在高于第一温度的第二温度(诸如约400~500℃)下进行第二退火或rta步骤,从而形成具有低电阻的稳定硅化物层656b及656c。在一些实施例中,硅化物层656b及656c可包括硅化钛(tisi)、硅化镍(nisi)、硅化钴(cosi)、ni-pt或其组合物。

318.返回参考图33b,方法m2接着进行至方块s218,其中第二基材接合至第一基材且覆盖第一隔离介电质、下部半导体鳍片、及下部磊晶源极/漏极结构。参考图35,在方块s218的一些实施例中,基材607包括硅。或者,基材607可包括锗、硅锗、砷化镓或其他适合的半导体材料。同样可选地,基材607可包括磊晶层。举例而言,基材607可具有上覆于体半导体的磊晶层。此外,基材607可施加应变以增强性能。举例而言,磊晶层可包括与体半导体不同的半导体材料,诸如上覆体硅的硅锗层或上覆体硅锗的硅层。这种应变基材可通过选择性磊晶生长(selective epitaxial growth,seg)形成。此外,基材607可包括绝缘体上半导体(semiconductor-on-insulator,soi)结构。同样可选地,基材607可包括埋入式介电层,诸如埋入式氧化物(buried oxide,box)层,诸如通过分离布植氧气(separation by implantation of oxygen,simox)技术、晶圆接合、seg、或另一适当方法形成的层。在一些实施例中,基材607可通过沉积制程形成,诸如化学气相沉积(chemical vapor deposition,cvd)、电浆增强原子层沉积(plasma enhanced atomic layer deposition,peald)、原子层沉积(atomic layer deposition,ald)、电浆增强cvd(plasma enhanced cvd,pecvd)或其他适合技术。

319.返回参考图33b,方法m2接着进行至方块s219,其中在第二基材上形成上部半导体鳍片用于上部晶体管。参考图36,在方块s219的一些实施例中,基材607可经历一系列沉积及光学微影术制程,使得可在基材607上形成衬垫层、遮罩层、及经图案化光阻剂层(未显示)。在一些实施例中,衬垫层为包括使用例如热氧化制程形成的氧化硅的薄膜。衬垫层可充当基材607及遮罩层之间的附着层。衬垫层亦可充当蚀刻遮罩层的蚀刻终止层。在一些实施例中,遮罩层由氮化硅形成,举例而言,使用低压化学气相沉积(low pressure cvd,lpcvd)或电浆增强化学气相沉积(plasma enhanced cvd,pecvd)。遮罩层在后续光学微影术制程期间用作硬遮罩。在遮罩层上形成光阻剂层且接着经图案化,在光阻剂层中形成开口,使得遮罩层的区域经曝光。

320.基材607可经图案化以形成至少一个半导体鳍片648b。遮罩层及衬垫层(未显示)可蚀刻穿过光阻剂层,曝光下伏基材607。接着蚀刻经曝光基材607,形成沟槽。相邻沟槽之

间的基材607的一部分可称为半导体鳍片648b。在蚀刻基材607之后,移除光阻剂层。接下来,可选地可执行清洗步骤以移除半导体基材607的原生氧化物。举例而言,可使用稀氢氟酸(hf)来执行清洗。

321.返回参考图33b,方法m2接着进行至方块s220,其中形成第二隔离介电质以围绕上部半导体鳍片的下部部分。参考图36,在方块s220的一些实施例中,形成隔离介电材料(未显示)以覆盖半导体鳍片648b。隔离介电材料形成为过度填充沟槽且覆盖半导体鳍片648b。沟槽中隔离介电材料可称为浅沟槽隔离(shallow trench isolation,sti)结构。在一些实施例中,隔离介电材料可由氧化硅、氮化硅、氧氮化硅、氟硅酸盐玻璃(fsg)、或其他低k介电材料制成。在一些实施例中,隔离介电材料可使用高密度电浆(high-density-plasma,hdp)化学气相沉积(chemical vapor deposition,cvd)制程形成,使用硅烷(sih4)及氧(o2)作为反应前驱物。在一些其他实施例中,隔离介电材料可使用次大气压cvd(sub-atmospheric cvd,sacvd)制程或高深宽比制程(high aspect-ratio process,harp)形成,其中制程气体可包括四乙氧基硅烷(teos)及臭氧(o3)。在其他实施例中,隔离介电材料可使用旋装介电质(spin-on-dielectric,sod)制程形成,诸如氢倍半硅氧烷(hsq)或甲基倍半硅氧烷(msq)。可使用其他制程及材料。在一些实施例中,隔离介电材料可具有多层结构,举例而言,在衬里上方形成具有氮化硅的热氧化衬里层。此后,可选地可对隔离介电材料执行热退火。

322.随后,执行诸如化学机械研磨(chemical mechanical polish,cmp)的平坦化制程,以移除半导体鳍片648b上方的多余隔离介电材料。在一些实施例中,平坦化制程亦可移除遮罩层及衬垫层,使得半导体鳍片648b的顶表面经曝光。在一些其他实施例中,当遮罩层曝光时,平坦化制程终止。在此类实施例中,遮罩层可充当平坦化中的cmp终止层。若遮罩层及衬垫层未通过平坦化制程移除,则遮罩层(若由氮化硅形成)可通过使用热h3po4的湿式制程移除,且衬垫层(若由氧化硅形成)可使用稀hf移除。随后,例如经由蚀刻操作,隔离介电材料凹陷,其中稀hf、siconi(包括hf及nh3)、或类似物可用作蚀刻剂。在使隔离介电材料凹陷之后,半导体鳍片648b的一部分高于隔离介电材料的顶表面。

323.应理解,上述方块s219及s220仅是半导体鳍片648b及sti结构材料如何形成的实例。在其他实施例中,可在基材607的顶表面上方形成介电层;沟槽可蚀刻穿过介电层;同质磊晶结构可在沟槽中磊晶生长;且介电层可凹陷,使得同质磊晶结构突出于介电层以形成鳍片。在其他实施例中,异质磊晶结构可用于鳍片。举例而言,半导体鳍片648b可凹陷,且在其位置磊晶生长不同于凹陷半导体鳍片648b的材料。在更进一步的实施例中,可在基材607的顶表面上形成介电层;沟槽可蚀刻穿过介电层;异质磊晶结构可使用不同于基材607的材料在沟槽中磊晶生长;且介电层可凹陷,使得异质磊晶结构突出于介电层以形成鳍片。在磊晶生长同质磊晶结构或异质磊晶结构的一些实施例中,所生长的材料可在生长期间经原位掺杂,这可避免鳍片的事先布植,尽管原位掺杂与布植掺杂可一起使用。在一些实施例中,半导体鳍片648b可包括硅锗(si

x

ge

1-x

,其中x可在约0与1之间)、碳化硅、纯锗或基本纯锗、iii-v化合物半导体、ii-vi化合物半导体、或类似物。举例而言,用于形成iii-v化合物半导体的可用材料包括但不限于inas、alas、gaas、inp、gan、ingaas、inalas、gasb、alsb、alp、gap、或类似物。

324.返回参考图33c,方法m2接着进行至方块s221,其中形成至少一个虚设栅极结构以

延伸跨越上部半导体鳍片。参考图36,在方块s221的一些实施例中,形成虚设栅极结构(未显示)以延伸跨越半导体鳍片648b。在一些实施例中,与本实施例的虚设栅极结构相关的材料及制造制程可与图2至图28中所示的虚设栅极结构152a及152c的材料及制造制程基本相同。因此,相关详细说明可参考前述段落,且在此不再描述。本实施例的虚设栅极结构具有基本平行的纵轴,这些纵轴基本垂直于半导体鳍片648b的纵轴。使用“后栅极”或替换栅极制程,将虚设栅极结构替换为替换栅极结构g63及g64。

325.返回参考图33c,方法m2接着进行至方块s222,其中第二栅极间隔物沿着虚设栅极结构的侧壁形成。参考图36,在方块s222的一些实施例中,沿着将由替换栅极结构g63及g64替换的虚设栅极结构的侧壁形成栅极间隔物654。在一些实施例中,与本实施例的栅极间隔物654相关的材料及制造制程可与图2至图28中所示的栅极间隔物154的材料及制造制程基本相同。因此,相关详细描述可参考前述段落,且此处不再描述。在一些实施例中,栅极间隔物654可用于偏移后续形成的掺杂区,诸如源极/漏极区。栅极间隔物654可进一步用于设计或修改源极/漏极区轮廓。

326.返回参考图33c,方法m2接着进行至方块s223,其中第二源极/漏极开口形成于上部半导体鳍片中。参考图36,在方块s223的一些实施例中,移除未由虚设栅极结构652a及652c以及栅极间隔物654覆盖的半导体鳍片648b的部分,以形成源极/漏极开口。在一些实施例中,与本实施例的源极/漏极开口相关的制造制程可与图2至图28中所示的源极/漏极开口148r的制造制程基本相同。因此,相关详细描述可参考前述段落,且在此不再描述。在形成源极/漏极开口之后,在一些实施例中,可执行预清洗制程以用氢氟酸(hf)或其他适合溶液清洗源极/漏极开口。

327.返回参考图33c,方法m2接着进行至方块s224,其中上部晶体管的上部磊晶源极/漏极结构形成于第二源极/漏极开口中。参考图36,在方块s224的一些实施例中,磊晶源极/漏极结构658d及658e分别形成于源极/漏极开口中。因此,栅极结构g63与栅极结构g63相对侧上的源极/漏极结构(如图38中所示,栅极结构g82/g85相对侧上的磊晶源极/漏极结构858b及858c)共同形成第三晶体管s63,且栅极结构g64与栅极结构g64的相对侧上的源极/漏极结构共同形成第四晶体管s64。参考图38及图39对此进行更详细的描述,第三晶体管s63的栅极结构g63与第一晶体管s61的栅极结构g61重叠,且第四晶体管s64的栅极结构g64与第二晶体管s62的栅极结构g62部分重叠。

328.磊晶源极/漏极结构658d及658e可使用一或多个磊晶生长或磊晶(epi)制程形成,使得可在半导体鳍片648b上以结晶状态形成si特征、sige特征、磷酸硅(sip)特征、碳化硅(sic)特征及/或其他适合特征。在一些实施例中,磊晶源极/漏极结构658d及658e的晶格常数不同于半导体鳍片648b的晶格常数,使得磊晶源极/漏极结构658d与658e之间的通道区可由磊晶源极/漏极结构658d及658e施加应变或应力,以提高半导体装置的载流子移动率且增强装置性能。磊晶制程包括cvd沉积技术(例如,气相磊晶(vapor-phase epitaxy,vpe)及/或超高真空cvd(ultra-high vacuum cvd,uhv-cvd))、分子束磊晶、及/或其他适合制程。磊晶制程可使用与半导体鳍片648b的组合物(例如,硅、硅锗、磷酸硅、或类似物)相互作用的气体及/或液体前驱物。磊晶源极/漏极结构658d及658e可经原位掺杂。掺杂种类包括p型掺杂剂,如硼或bf2;n型掺杂剂,如磷或砷;以及/或其他适合的掺杂剂,包括其组合物。若磊晶源极/漏极结构658e及658e未原位掺杂,则执行布植制程以掺杂磊晶源极/漏极结构

658d及658e。可执行一或多个退火制程来活化磊晶源极/漏极结构658d及658e。退火制程包括快速热退火(rapid thermal annealing,rta)及/或激光退火制程。

329.在一些实施例中,在源极/漏极磊晶制程之前,通过硅化制程在磊晶源极/漏极结构658d及658e上形成硅化物层686b及686c。在一些实施例中,与本实施例的硅化物层686b及686c相关的材料及制造制程可与图2至图28中所示的硅化物层186b及186c的材料及制造制程基本相同。因此,相关详细说明可参考前述段落,且在此不再描述。

330.随后,用于形成本实施例的集成电路结构600的方法m2的方块s225~s231与用于形成与图22至图28相关联的前述描述中所描述的集成电路结构100的方法m1的方块s121~s127基本相同,且因此为了清楚起见,此处不再重复。举例而言,与互连结构696、栅极结构g63及g64、栅极通孔693a、源极/漏极触点683b及683c、源极/漏极通孔693b、抵接触点693c、栅极间隔物654、介电层665、接触蚀刻终止层662、及介电帽676相关联的材料及制造制程可与如图22至图28中所示的互连结构196、栅极结构g3及g4、栅极通孔193a、源极/漏极触点183b及183c、源极/漏极通孔193b、抵接触点193c、栅极间隔物154、介电层165、接触蚀刻终止层162、及介电帽176的基本相同。因此,相关详细说明可参考前述段落,且此处不再描述。

331.图37a至图37c示出了根据一些其他实施例的制造集成电路结构700中的横截面图。在本实施例的图37a之前用于形成集成电路结构700的方法与用于形成与图36相关联的前述描述中所描述的集成电路结构600的方法m2的方块s218~s231基本相同,因此为了清楚起见,此处不再重复。举例而言,与图37a中半导体结构700a的基材707、半导体鳍片748b、栅极结构g73及g74、栅极间隔物754、介电帽776、磊晶源极/漏极结构758d及758e、互连结构796、栅极通孔793a、源极/漏极触点783b及783c、源极/漏极通孔793b、抵接触点793c、介电层765、及接触蚀刻终止层762相关联的材料及制造制程可与如图36中所示的基材607、半导体鳍片648b、栅极结构g63及g64、栅极间隔物654、介电帽676、磊晶源极/漏极结构658d及658e、互连结构696、栅极通孔693a、源极/漏极触点683b及683c、源极/漏极通孔693b、抵接触点693c、介电层665、及接触蚀刻终止层662的基本相同。因此,相关详细说明可参考前述段落,且此处不再描述。

332.参考图37a,作为实例但非限制性地,半导体结构700a的基材707可使用研磨及/或湿式蚀刻或干式蚀刻技术来减薄。作为实例但非限制性地,剩余基材厚度在约50nm至约500nm的范围内。在一些实施例中,作为实例但非限制性地,接着执行厚度的进一步减小,下至约1μm的半导体厚度。在一些实施例中,可通过在装置晶圆中并入可充当蚀刻终止层的掺杂层来达成减薄。接着,作为实例但非限制性地,将终止于掺杂层上的选择性湿式蚀刻步骤应用于减薄半导体晶片至约1μm的所需厚度。随后,通过钝化制程在基材707的背面上形成钝化层709。在一些实施例中,钝化层709可包括氧化硅、sicn、或用于达成后续直接介电至介电接合制程的任何其他材料。在一些实施例中,在形成钝化层709之前,使基材707的背面经受研磨制程。

333.图37b示出了半导体结构700b的示意图。形成半导体结构700b的方法与形成半导体结构700a的方法基本相同,且因此为了清楚起见,此处不再重复。举例而言,与如图37b中所示的半导体结构700b的钝化层709'、基材707'、半导体鳍片748b'、栅极结构g73'及g74'、栅极间隔物754'、介电帽776'、磊晶源极/漏极结构758d'及758e'、互连结构796'、栅极通孔793a'、源极/漏极触点783b'及783c'、源极/漏极通孔793b'、抵接触点793c'、介电层765'、

及接触蚀刻终止层762'相关的材料及制造制程可与如图36中所示的半导体结构700a的钝化层709a、基材707a、半导体鳍片748b、栅极结构g73及g74、栅极间隔物754、介电帽776、磊晶源极/漏极结构758d及758e、互连结构796、栅极通孔793a、源极/漏极触点783b及783c、源极/漏极通孔793b,抵接触点793c、介电层765、及接触蚀刻终止层762的基本相同。因此,相关详细说明可参考前述段落,且此处不再描述。

334.随后,参考图37c,如图37a中所示的半导体结构700a经由钝化层709及709'连接至如图37b中所示的半导体结构700b,以达成直接介电至介电接合,从而获得如图37c中所示的接合半导体结构堆叠。

335.图38示出了根据本揭露的一些实施例的集成电路结构800的示意图。用于形成本实施例的集成电路结构800的操作与在与图2至图28相关联的前述描述中所描述的用于形成集成电路结构100的操作基本相同,且因此为了清楚起见,此处不再重复。举例而言,与半导体鳍片848、栅极结构g81、g82、g83、g84、g85、及g86、磊晶源极/漏极结构858b及858c、栅极通孔813a及893a、源极/漏极触点823b、823c、883b、及883c、源极/漏极通孔813b及893b、抵接触点813c及893c、硅化物层856b、856c、886b、及886c、栅极间隔物830及854、及介电层803及865相关的材料及制造制程可与如图2至图28中所示的半导体鳍片148、栅极结构g1、g2、g3、及g4、磊晶源极/漏极结构158b及158c、栅极通孔113a及193a、硅化物层156b、156c、186b、及186c、源极/漏极触点123b、123c、183b、及183c、源极/漏极通孔113b及193b、抵接触点113c及193c、栅极间隔物130及154、及介电层103及165的基本相同。因此,相关详细说明可参考前述段落,且此处不再描述。

336.图39示出了根据本揭露的一些实施例的集成电路结构900的示意图。用于形成本实施例的集成电路结构900的操作与在前述描述中所描述的用于形成集成电路结构600的操作基本相同,且因此为了清楚起见,在此不再重复。举例而言,与基材907、半导体鳍片948a及948b、栅极结构g91、g92、g93、g94、g95、及g96、磊晶源极/漏极结构958b、958c、958d、及958e、栅极通孔913a及993a、源极/漏极触点923b、923c、983b、及983c、源极/漏极通孔913b及993b、抵接触点913c及993c、硅化物层956b、956c、986b、及986c、栅极间隔物930及954、介电层903及965相关的材料及制造制程可与如图34至图36中所示的基材607、半导体鳍片648a及648b、栅极结构g61、g62、g63、及g64、磊晶源极/漏极结构658b及658c、栅极通孔613a及693a、硅化物层656b、656c、686b、及686c、源极/漏极触点623b、623c、683b、及683c、源极/漏极通孔613b及693b、抵接触点613c及693c、栅极间隔物630及654、及介电层603及665的基本相同。因此,相关详细描述可参考前述段落,且在此不再描述。

337.基于上述讨论,可看出本揭露具有优点。然而应理解,其他实施例可提供额外的优点,且并非所有的优点都必须在本文中揭示。此外,没有特定的优点需要用于所有的实施例。在各种实施例中,本揭露在晶片的给定晶体管面积上提供“双半导体装置”。更具体地,在给定晶体管面积内,一晶体管设置于另一晶体管之上,这进而使给定晶体管面积内的晶体管数目加倍,从而可增大ic的功能密度。

338.在一些实施例中,集成电路结构包括下部互连结构、第一半导体鳍片、下部栅极结构、第一源极/漏极结构、上部栅极结构、及上部互连结构。第一半导体鳍片在下部互连结构之上。下部栅极结构在第一半导体鳍片下方且延伸跨越第一半导体鳍片。第一源极/漏极结构在第一半导体鳍片中且在下部栅极结构的相对侧上。第一源极/漏极结构与下部栅极结

构形成下部晶体管。上部栅极结构在第一半导体鳍片之上且延伸跨越第一半导体鳍片。上部栅极结构与第一源极/漏极结构形成上部晶体管。上部互连结构在上部栅极之上。在一些实施例中,上部栅极结构与下部栅极结构重叠。在一些实施例中,第一源极/漏极结构穿透第一半导体鳍片。在一些实施例中,第一半导体鳍片具有嵌入下部栅极结构中的底端及嵌入上部栅极结构中的顶端。在一些实施例中,下部栅极结构的顶表面具有凹陷区域。在一些实施例中,集成电路结构进一步包括自下部栅极结构向下延伸至下部互连结构的下部栅极通孔及自上部栅极结构向上延伸至上部互连结构的上部栅极通孔。在一些实施例中,上部栅极通孔与下部栅极通孔重叠。在一些实施例中,集成电路结构进一步包括将下部栅极结构电连接至第一源极/漏极结构中的一者的抵接触点。在一些实施例中,集成电路结构进一步包括平行于第一半导体鳍片延伸的第二半导体鳍片及第二半导体鳍片中第二源极/漏极结构,且下部栅极结构及上部栅极结构进一步延伸跨越第二半导体鳍片。在一些实施例中,第二半导体鳍片中第二源极/漏极结构与第一半导体鳍片中第一源极/漏极结构间隔开。

339.在一些实施例中,集成电路结构包括第一互连结构、第一栅极结构、第一半导体鳍片、第一半导体基材、第二半导体鳍片、第二栅极结构、及第二互连结构。第一栅极结构在第一位准高度处延伸至第一互连结构之上。第一半导体鳍片在第一栅极结构之上延伸且跨越第一栅极结构。第一半导体基材在半导体鳍片上方。第二半导体鳍片在第一半导体基材之上延伸。第二栅极结构在高于第一位准高度的第二位准高度处在第二半导体鳍片之上延伸且跨越第二半导体鳍片。第二互连结构在第二栅极结构上方。在一些实施例中,第二栅极结构与第一栅极结构重叠。在一些实施例中,第二栅极结构与第一栅极结构不重叠。在一些实施例中,第一半导体基材在第一半导体鳍片与第二半导体鳍片之间。在一些实施例中,集成电路结构进一步包括第一半导体基材与第二半导体鳍片之间的第二半导体基材以及第一半导体基材与第二半导体基材之间的钝化层。在一些实施例中,集成电路结构进一步包括在第一半导体鳍片中且在第一栅极结构的相对侧上的第一磊晶结构及在第二半导体鳍片中且在第二栅极结构的相对侧上的第二磊晶结构。

340.在一些实施例中,用于形成集成电路结构的方法包括:在基材上方形成第一互连结构;在第一互连结构上方形成第一介电层;在第一介电层中蚀刻栅极沟槽;在第一介电层中栅极沟槽中形成第一栅极结构;在第一栅极结构上方沉积第二介电层;在第二介电层中蚀刻鳍片沟槽且在垂直于栅极沟槽的方向上延伸;在第二介电层中鳍片沟槽中形成半导体鳍片;以及形成延伸跨越第二半导体鳍片的第二栅极结构。在一些实施例中,蚀刻鳍片沟槽经执行,使得鳍片沟槽延伸至第一栅极结构中。在一些实施例中,该方法进一步包括:在形成半导体鳍片之后且在形成第二栅极结构之前,将第二介电层回蚀至半导体鳍片的顶表面之下。在一些实施例中,该方法进一步包括:蚀刻半导体鳍片以在第一栅极结构的相对侧上形成多个开口;以及分别在多个开口中磊晶生长多个源极/漏极结构。

341.前述内容概述若干实施例的特征,使得熟悉此项技术者可更佳地理解本揭露的态样。熟悉此项技术者应了解,其可易于使用本揭露作为用于设计或修改用于实施本文中引入的实施例的相同目的及/或达成相同优势的其他制程及结构的基础。熟悉此项技术者亦应认识到,此类等效构造并不偏离本揭露的精神及范畴,且此类等效构造可在本文中进行各种改变、取代、及替代而不偏离本揭露的精神及范畴。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1