具复合式针脚结构的封装元件及其制法的制作方法

1.本发明关于一种封装元件,尤指一种具有复合式针脚结构的封装元件。

背景技术:

2.传统半导体封装元件的针脚(pin)主要是以铜制导线架(lead frame)构成,以图16所示的功率电晶体为例,制作时将一晶片300黏置在一导线架301的晶垫区,而该导线架301上预制作有多个并列的针脚302,于黏晶后执行打线步骤,将该晶片300上的信号接点通过导线303分别电连接至导线架301上的不同针脚302,最后于晶片300上包覆绝缘的封胶材304。

3.图17及18分别表示水平式及垂直式的封装方式,若晶片300的信号接点皆位于同一平面,打线时会采取图17的水平式封装,将位于晶片300表面的信号接点通过导线303连接到导线架301上的对应针脚302;若晶片300的信号接点分别位于表面及底面,打线时会如图18垂直式封装所示,将位于晶片300表面的信号接点通过导线303连接到对应的针脚302,而位于晶片300底面的另一信号接点通过银或焊锡等焊料连接在导线架301上。

4.无论采取水平式或垂直式的封装方式,通孔插装(pth)的封装元件主要还是利用导线架已预先成型的接脚作为封装元件的针脚,但使用导线架的缺点在于需针对各种不同封装元件设计、制作专属型态的导线架,对封装厂而言需要向供应商购买导线架作为原材料,故封装制作成本相对较高。

5.另一方面,完成封装之后的成品,因为具有导线架厚度、晶片高度、打线高度及封胶材厚度,因此封装成品的整体厚度相对较大而不利于元件薄型化。

技术实现要素:

6.有鉴于此,本发明主要提供一种不需使用导线架作为原材料的具复合式针脚结构的封装元件及其制法。

7.本发明的具复合式针脚结构的封装元件包含有:

8.一封装元件本体,包含一基板,该基板以一绝缘本体及多个导电层构成,该基板形成有一晶片放置口,于该晶片放置口内容置一晶片;

9.多个针脚,该多个针脚从该封装元件本体向外延伸并且电性连接该晶片,各针脚为复合式层叠结构,该复合式层叠结构包含有:

10.从该封装元件本体一体延伸的该绝缘本体,该多个导电层设置在该绝缘本体相对的两面以电性连接该晶片。

11.本发明的具复合式针脚结构的封装元件制法包含有:

12.准备一基板,该基板划分为一本体区及一针脚区,其中,该针脚区预设有多个针脚位置,该基板包含一绝缘本体,该绝缘本体的相对两面分别具有至少一导电层;

13.在该本体区形成一晶片放置口及至少一导通孔;

14.将一晶片置入于该晶片放置口;

15.将该晶片电性连接至该基板的导电层及该导通孔;

16.成型封装元件本体及針脚,是沿着该本体区及针脚位置的边缘切割,其令该本体区形成一封装元件本体,于该针脚位置所保留的基板构成多个针脚,其中,每个针脚包含有该绝缘本体及其相对两面的该导电层。

17.本发明利用同一基板提供晶片设置,该晶片电性连接该基板的导电层,通过切削该基板及该导电层可成型得到多个针脚,各针脚上的导电层电性连接晶片,借此构成一薄型化的封装元件而不需使用传统的导线架。

附图说明

18.图1a~图1e:本发明一较佳实施例的制作流程示意图。

19.图2a~图2b:本发明另一较佳实施例的部分制作流程示意图。

20.图3:本发明一较佳实施例进行针脚切削的操作示意图。

21.图4:本发明一较佳实施例的平面示意图。

22.图5:本发明针脚的局部放大图。

23.图6a~图6e:本发明另一较佳实施例的制作流程示意图。

24.图7:图6a~6e实施例在针脚区形成通孔后的平面示意图。

25.图8:图6a~6e实施例完成针脚切削后的平面示意图。

26.图9:图6a~6e实施例完成针脚切削后的立体示意图。

27.图10:本发明的针脚另一实施例的平面示意图。

28.图11:图10所示针脚插接于电路板之后的示意图。

29.图12:本发明的针脚另一实施例的平面示意图。

30.图13:图12所示的针脚插接于电路板之后的示意图。

31.图14:本发明针脚另一实施例的平面示意图。

32.图15:图14所示针脚插接于电路板之后的示意图。

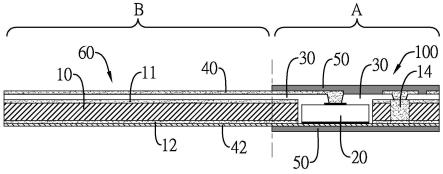

33.图16:现有功率电晶体的立体透视示意图。

34.图17:现有水平式封装元件的剖面示意图。

35.图18:现有垂直式封装元件的剖面示意图。

具体实施方式

36.关于本发明的第一实施例,请参考图1a~1d所示,在制作过程中不需使用金属导线架作为原材料,通过面板级封装制程(panel level package process)即可形成所需的针脚,此实施例以通孔插装(pin through hole,pth)封装元件为例。首先参看图1a所示,本实施例中选用一铜箔板(copper clad laminate,简称ccl)作为基板,该铜箔板是在一绝缘的本体10其上、下表面压合铜箔,以该铜箔作为导电层11、12,在基板可预先划分有一本体区a及一针脚区b,该本体区a供容置晶片、形成导电通孔、或是制作重布线层(rdl)以形成封装元件本体的区域,而针脚区b则是指最终会形成封装元件针脚的区域,在该针脚区b根据产品规格规划好各针脚的位置及数量。

37.参考图1b及1c所示,在本体区a形成有晶片放置口13以及导通孔14,该导通孔14的内壁面电镀导电材或是在该导通孔14的内部填充导电材,使导通孔14电性连接该导电层

11、12;晶片20置入在该晶片放置口13的内部,晶片20具有信号接点21,该信号接点21的位置不限,可以是在晶片20的同一表面或是位于晶片20的上、下表面。在图1c的实施例中,晶片20的上、下表面具有信号接点21。

38.参考图1d所示,在放置晶片20之后,根据元件需求将不同信号接点21分别电性连接至针脚区b,实现电性连接的作法可包含电镀、形成一层或多层的重分布线路层(rdl)等方式;图1d只是示意表现出信号接点21与针脚区b的导电层11、12电性连接,例如在基板上先形成一绝缘层30以覆盖基板及晶片20并且延伸至针脚区b,再于该绝缘层30表面经由黄光制程形成一线路层40,该线路层40电性连接对应的信号接点21且亦延伸至针脚区b;而晶片20底面的信号接点21可制作一底面线路层42以电性连接至对应的导电层12、导通孔14等。

39.参考图1e所示,在基板本体区a的最外表面形成一保护层(solder mask)50,该保护层50不需延伸覆盖至针脚区b;本实施例是在基板的本体区a的上、下两侧各形成一保护层50。

40.在前面的实施例中,该基板是一铜箔基板。除此之外,该基板也可以是一般介电材料构成的绝缘基板,其上、下表面没有预先压合的铜箔,可以通过黄光制程在该绝缘基板的表面制作出所需的导电线路层,例如通过黄光制程形成上述的导电层11、12以及线路层40等。

41.请参考图2a、2b,在另一实施例中,在该基板上不需额外制作线路层40,利用该基板其上、下表面原先压合的导电层11、12及底面线路层42电连接至晶片20即可。

42.请参考图3、图4所示,利用一切削工具对基板的本体区a及针脚区b进行切割,其中,沿着该本体区a的边缘切割后形成一封装元件本体100,该封装元件本体100为一矩形。而在针脚区b的切割进行针脚成型作业,保留预定的针脚位置并移除非必要的基板区域,保留下来的基板构成封装元件的针脚60;图1a~1e示意图的左侧只是呈现单一支针脚60的侧视结构,实际上该封装元件会有多个并列的针脚。在本实施例中,可利用成型机(routing machine)切削多余的基板而成型所需的针脚60,其它的成型方式例如冲压、镭射切割等方式也是可用于制作针脚60,例如控制铣刀200沿着图3的切削路径r,即沿着预设的针脚60的位置边缘移动。

43.各针脚60的结构如图5所示,包含有至少位于中间的绝缘本体10以及在该绝缘本体10正、反两面上的导电层,该导电层可包含基板本身的铜箔层12或是后续再制作形成的线路层40、底面线路层42等;每一支针脚60通过导电层电性连接至晶片20。因为该针脚60是切削本体10之后所形成,因此针脚60本身的长度/宽度、相邻针脚60之间的脚距(pitch)等可以根据产品的规格需求而切割成型,不受传统导线架的既定规格所限。各针脚60本身的厚度或是表面导电层的厚度也可调整,例如借由堆叠绝缘层30或线路层40来提高整体针脚60的厚度,或是电镀制作较厚的线路层40来提高整体针脚60的厚度。

44.关于本发明的另一实施例请参考图6a~图6e所示,与图1a~图1e的实施例差别是先经由机械钻孔(如箭头所示)在针脚区b形成多个通孔15,如图7所示所述通孔15的位置分布在各针脚位置的边缘,且在各个通孔15的内壁面电镀一电镀层151。当封装元件的针脚区b在进行针脚成型步骤时,切削工具沿着针脚60的边缘切割可同时将各通孔15切开,如图8、图9所示,被切开的各通孔15在针脚60的相对两侧面自然形成内凹的弧形缺口601,每个缺

口601的表面具有电镀层151以增加各针脚60侧面的上锡面积,提高封装元件的沾锡性。本实施例因为在制作本体区a的导通孔14时即同步制作通孔15及孔壁电镀,因此在成型针脚60后不需要额外进行钻孔及电镀作业,可简化制程步骤。但是在其它实施例中,也可以在成型针脚60之后,再对针脚60的全部表面进行电镀,使针脚60表面具有更多面积沾附焊锡。

45.请参考图10、图11所示,在成型针脚的步骤中,该针脚60形成一针脚本体61及一窄缩部62,该窄缩部62的一端连接封装元件本体100的底面,另一端连接该针脚本体61;该窄缩部62的宽度略小于针脚本体61的宽度。因为该窄缩部62的宽度亦小于电路板p上的焊孔的孔径,当针脚60插接进入电路板p时,该封装元件本体100的底面能够贴平在电路板p的表面,此实施例可提高表面黏着元件(smt)在焊接至电路板表面时的稳定度,确保封装元件不会在电路板p上产生晃动。于制作该窄缩部62时,可以利用铣刀沿着图10所示的切割路径r切削,当铣刀移动至针脚60与封装本体元件100底面的接合处时,控制铣刀朝针脚60的中心移动以略微切削针脚60部分顶端,铣刀向外退出之后再沿着针脚60的边缘切削,便可在针脚60的一端形成窄缩部62。

46.再参考图12、图13所示,在成型针脚的步骤中,也可在封装元件本体100的底面形成凹槽102,该凹槽102位于每一个针脚60的相对两侧;同样的,当针脚60插接进入电路板p时,该封装元件本体100的底面能够贴平在电路板p的表面,使封装元件不会在电路板p上产生晃动,而且该封装元件本体100与电路板p表面之间因为凹槽102形成的间隙也可以增加散热效果。该凹槽102的制作可以利用铣刀沿着图12所示的切割路径r切削,当铣刀移动至针脚60与封装本体元件100的交接面时,控制铣刀朝封装元件本体100的底面略微向内移动,铣刀向外退出之后再沿着针脚60的边缘切削,便可在封装元件本体100的底面形成该凹槽102。

47.参考图14、图15所示,相较于图10的实施例,本发明的针脚60可进一步形成一支撑部63,该支撑部63与封装元件本体100的底面相接且宽度略大于针脚本体61的宽度,同时该支撑部63的宽度也大于电路板p上的焊孔的孔径;在该支撑部63的底端形成该窄缩部62,该窄缩部62的宽度略小于电路板p上的焊孔的孔径。当封装元件插接于电路板p时,该支撑部63的下缘扺靠在电路板p的表面,使封装元件本体100的底面与电路板p之间形成一散热间隙g,而该窄缩部62以下可进入至焊孔内部;该封装元件本体100与电路板p表面之间因为具有散热间隙g,可更加提升散热效果。

48.基于上述的详细说明,本发明当中的实施例具有以下的一或多个优点:

49.1.本发明利用面板级封装(plp)技术制作封装元件,不需使用导线架即可制作出封装元件所需的针脚。

50.2.相较于传统封装元件,本发明因不需使用导线架、打线(wire bonding)及封胶(molding),可有效缩减封装元件的整体厚度,有助于缩小产品体积及提高散热效果。

51.3.当针脚侧面形成缺口时,可以提高沾锡面积,提高产品的可焊性(solderbility)。

52.4.成型产品可以利用自动光学检测仪器(aoi)进行品管判断,检测外观是否具有瑕疵。

53.以上所述仅是本发明的优选实施例而已,并非对本发明做任何形式上的限制,虽然本发明已以优选实施例揭露如上,然而并非用以限定本发明,任何熟悉本专业的技术人

员,在不脱离本发明技术方案的范围内,当可利用上述揭示的技术内容作出些许更动或修饰为等同变化的等效实施例,但凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1