一种铁电存储器及其制备方法、应用

1.本发明涉及半导体生产工艺领域,特别涉及一种铁电存储器及其制备方法、应用。

背景技术:

2.hfo2基铁电材料(hzo)是一种新型的铁电材料,具有优异的铁电性,与传统的pzt、bst等铁电材料相比,其与cmos工艺兼容,且其较高的介电常数可以将薄膜厚度控制到很薄;其在低于10nm的超薄厚度下仍具有稳定的铁电性,而pzt、sbt等铁电材料在较厚是才能保持其铁电性,可以有效减小fefet等器件的尺寸,从而提升芯片的集成度;不含有pb元素,可以减少对环境的污染。hzo基铁电存储器有着高速、低功耗、读取速度快与操作电压低的优点,是有希望解决“存储墙”问题的新型非易失性存储器,有着广阔的发展前景与潜力。

3.在电极-铁电层-电极(mfm)这种铁电存储器结构中,如何将铪基铁电存储器件集成于cmos集成电路中,且使得铁电存储器件有着较大的剩余极化强度,是一个亟待解决的问题,这限制了铁电存储器走向商业化应用的进程。

4.为此,提出本发明。

技术实现要素:

5.本发明的主要目的在于提供一种铁电存储器的制备方法,该方法提高了集成于芯片中的铁电存储器的剩余极化强度。

6.为了实现以上目的,本发明提供以下技术方案。

7.本发明的第一方面提供了一种铁电存储器的制备方法,包括:

8.在衬底上沉积tin底电极,然后在cvd腔室中通入nh3对底电极进行处理;

9.在所述底电极表面沉积氧化铪基铁电膜;

10.在所述氧化铪基铁电膜表面沉积顶电极;

11.利用干法刻蚀手段图形化所述顶电极;

12.然后进行退火处理:退火时间为20-40s,温度为400-600℃;

13.之后进行金属互连。

14.本发明的第二方面提供了一种铁电存储器,采用上述的制备方法得到。

15.本发明的第三方面提供了上述的铁电存储器在集成电路中的应用。

16.与现有技术相比,本发明达到了以下技术效果。

17.(1)本发明采用特定的工艺顺序形成底电极、铁电层和顶电极后再退火,同时对底电极进行nh3处理,减少底电极上的缺陷,以及特定的退火条件实现氧化铪基铁电膜的结晶以促进铁电相的产生,基于这些方面提高了集成于芯片中的铁电存储器的剩余极化强度。

18.(2)本发明提供的工艺与cmos工艺兼容,且工艺简单成本较低,可在大规模生产中应用。

附图说明

19.通过阅读下文优选实施方式的详细描述,各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。附图仅用于示出优选实施方式的目的,而并不认为是对本发明的限制。

20.图1为本发明实施例提供的制备方法中沉积氧化铪基铁电膜后的结构图;

21.图2为本发明实施例提供的制备方法中沉积顶电极并图形化后的结构图;

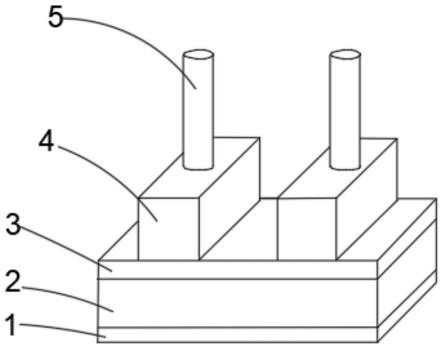

22.图3为本发明实施例提供的制备方法中形成金属互连结构后的存储器单元结构图。

具体实施方式

23.以下,将参照附图来描述本公开的实施例。但是应该理解,这些描述只是示例性的,而并非要限制本公开的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本公开的概念。

24.在附图中示出了根据本公开实施例的各种结构示意图。这些图并非是按比例绘制的,其中为了清楚表达的目的,放大了某些细节,并且可能省略了某些细节。图中所示出的各种区域、层的形状以及它们之间的相对大小、位置关系仅是示例性的,实际中可能由于制造公差或技术限制而有所偏差,并且本领域技术人员根据实际所需可以另外设计具有不同形状、大小、相对位置的区域/层。

25.在本公开的上下文中,当将一层/元件称作位于另一层/元件“上”时,该层/元件可以直接位于该另一层/元件上,或者它们之间可以存在居中层/元件。另外,如果在一种朝向中一层/元件位于另一层/元件“上”,那么当调转朝向时,该层/元件可以位于该另一层/元件“下”。

26.如背景技术所述,现有的铁电存储器件制备工艺使得铁电存储器件有着较小的剩余极化强度。本发明发现工艺顺序以及工艺条件对该极化强度有关键影响,为此提供以下制备方法。

27.如图1所示,提供衬底1;该衬底1可以是是本领域技术人员熟知的任何用以承载半导体集成电路组成元件的底材,例如绝缘体上硅(silicon-on-insulator,soi)、体硅(bulk silicon)、锗、锗硅、砷化镓或者绝缘体上锗等,相应的顶层半导体材料为硅、锗、锗硅或砷化镓等,也可以是已经在上述列举的衬底上加工了其他结构的载体,例如已制作栅极、晶体管等结构的载体。该载体可预先清洁。

28.然后在衬底1上沉积tin底电极2,如图1所示。沉积法包括但不限于pvd、lpcvd、ald、rtcvd或者pecvd等手段,优选采用pvd法。pvd法的工艺条件对存储器剩余极化强度有显著影响。经研究发现,当离子束能量为600~1100ev,电流值为30~50ma时,沉积得到的存储器能够获得较高的剩余极化强度。

29.利用上述方法沉积tin底电极2时,可能会因为溅射时粒子轰击效应等原因使得电极自身存在很多缺陷。为此,本发明在沉积之后将其转移至cvd腔室中,通入nh3对底电极进行处理,以提高底电极的电可靠性。nh3处理时优选在惰性气氛中进行,例如n2气氛中。并且该处理的工艺条件对存储器剩余极化强度有显著影响,经研究发现,当压强为20~80pa,功率为10~1000w,流量为10~100sccm,处理时间为1-30min时,能够获得较高的剩余极化强

度。

30.对于底电极2的厚度优选控制在20nm~50nm,以获得良好的电性能。

31.接下来在底电极2表面沉积氧化铪基铁电膜3,如图1所示。该膜3可采用lpcvd、ald、rtcvd或者pecvd等手段,优选ald(原子层沉积法),ald是脉冲式供应反应气体和前驱体进行沉积的方法,即脉冲供应前驱体、氧化剂。优选的ald工艺条件包括:前驱体分别为hf[n(c2h5)ch3]4和zr[n(c2h5)ch3]4,氧源为o3或h2o,温度200℃~300℃,以尽量减小铁电膜中的空位缺陷。

[0032]

氧化铪基铁电膜3的厚度优选控制在5nm~13nm,以获得良好的电性能。

[0033]

接下来在氧化铪基铁电膜3表面沉积顶电极4,如图2所示,顶电极的类型不限定,例如常见的各类金属,优选与底电极采用相同的材料,即tin。同样地,顶电极的沉积法包括但不限于pvd、lpcvd、ald、rtcvd或者pecvd等手段,优选采用pvd法。pvd法的工艺条件对存储器剩余极化强度有显著影响。经研究发现,当离子束能量为600~1100ev,电流值为30~50ma时,沉积得到的存储器能够获得较高的剩余极化强度。

[0034]

之后利用干法刻蚀手段图形化所述顶电极4,其具有快速、杂质少等优点。优选的干法刻蚀条件为:刻蚀气体为sf6和c3f8,射频功率为400-600w,刻蚀时间为20-30s。

[0035]

顶电极4的图形根据期间需求而定。

[0036]

接下来再进行退火处理,退火主要作用是实现氧化铪基铁电膜的结晶以促进铁电相的产生,优选的退火条件是:退火时间为20-40s,温度为400-600℃。该条件结合底电极的处理可以显著提高存储器的剩余极化强度。退火处理时在惰性气氛中进行,例如优选n2气氛中。

[0037]

最后进行金属互连,形成互连结构5,如图3所示。可采用铝、钨等金属材料,优选al。

[0038]

在金属互连工序中,通常借助反复沉积介质层、刻蚀介质层形成通孔、介质层等工艺实现,这些工艺均可采用本领域常见的手段。

[0039]

本发明的以上方法流程简单,只通过特定的工艺顺序和工艺条件就达到了提高集成于芯片中的铁电存储器的剩余极化强度的效果。

[0040]

以上对本公开的实施例进行了描述。但是,这些实施例仅仅是为了说明的目的,而并非为了限制本公开的范围。本公开的范围由所附权利要求及其等价物限定。不脱离本公开的范围,本领域技术人员可以做出多种替代和修改,这些替代和修改都应落在本公开的范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1