一种高集成度纳米墙集成电路结构

1.本发明涉及微电子技术和集成电路领域。

背景技术:

2.传统平面mosfet结构在22nm之后逐步被三维的finfet所取代。finfet由美国加州大学伯克利分校的胡正明教授于2000年左右正式发表论文提出;finfet的沟道区域是一个被栅极三面包裹的鳍状半导体,三面栅结构增强了栅控能力,有效的抑制了短沟道效应,使得摩尔定律得以延续。沿着finfet三面栅结构的思路,在5nm节点以后,人们提出了四面栅结构的gaafet(栅极全包围场效应晶体管)结构。

3.mosfet分为n型和p型,n型的沟道载流子为电子,p型的沟道载流子为空穴,而电子迁移率约是空穴迁移率的3倍,所以在cmos工艺中,为了形成对称的互补电特性,在相同沟道长度条件下,每个pmos的沟道宽度是nmos宽度的3倍。在传统平面mosfet中,常使用折叠栅的方法展宽沟道,在finfet中,则大多由3个pmos并联的方法实现,两者都大大增加了集成电路的面积,限制了集成度的提高。

4.dibl(漏极诱生势垒降低)效应是平面mosfet进入小于22nm工艺节点以后,阻止其进一步缩小的主要问题。近十年来,人们采用了fdsoi、finfet和gaafet等方法,在“等比例缩小”基础上,利用mos栅极作用,使沟道区“全耗尽”的方法,来克服短沟道mosfet的dibl效应,基于全耗尽理论的finfet和gaafet必须要将沟道区三面或四面包裹,才能实现mosfet功能。以nmosfet为例,全耗尽原理要求p-well为本征或低掺杂;其带来的负面效果是:第一,需要用栅极包裹硅沟道区,从而降低了集成度;第二,mosfet的宽长比调整很不方便,就finfet而言,在fin的高度、宽度被工艺固化、l

ch

已经是最小的条件下,想要增加宽长比只能采用多管并联方式。多管并联意味着宽长比是以成倍增加的方式实现的。这对需精确控制宽长比的模拟ic而言,无疑是十分不方便的。

5.传统的mosfet,包括平面mosfet、soifet、finfet和gaafet等,结构决定了,以nmosfet为例,p-well的掺杂浓度是远低于源漏区浓度的。即便轻掺杂源漏区(ldd)存在,也不能本质改变这种状况。因为,“轻掺杂源漏区”术语中所指“轻掺杂”是对重掺杂源漏区而言。ldd的掺杂浓度一定是高于p-well掺杂浓度的。这是由硅栅源漏自对准离子注入(含退火)工艺决定的。pn结的雪崩击穿电压是由低掺杂浓度一侧决定,也就是说,p-well浓度和沟道长度l

ch

决定了传统mosfet的雪崩击穿电压bv

ds

。正因如此,ieee irds预测了:今后,摩尔定律前进的速度会越来越慢,单个晶体管的栅极长度l

ch

将缓慢缩小,直至2028年,l

ch

缩小到12nm,此后,l

ch

将不再能缩小。在28nm工艺节点以前,l

ch

一直可以随特征尺寸lf而减小,所以ic的集成度每18~24个月翻一倍。这是摩尔定律最核心内容。2028年,进入1.5纳米工艺节点后,l

ch

不能再缩小;这意味着摩尔定律届时寿终正寝。由于mosfet的工作频率fo~1/l

ch2

,这意味着现有的finfet和gaafet高频应用受限。

技术实现要素:

6.本发明旨在提供一种集成度优于finfet和gaafet、最短沟道长度l

ch

显著短于finfet和gaafet以及mosfet栅极宽长比调节的方便性明显优于finfet和gaafet的ic基本结构,我们称之为一种具有高集成度的纳米墙集成电路单元结构(nano-wall fet,简称nwafet)。

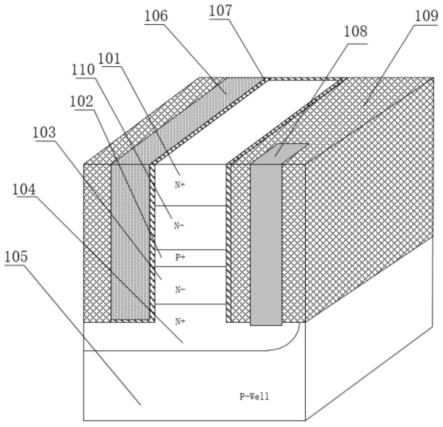

7.本发明技术方案1为一种高集成度纳米墙集成电路结构,如图1所示。在该结构最下方为一个p-well硅单晶半导体区域105,在该p-well半导体区域105上部形成有nwafet的硅单晶n+漏极区域104;在该n+漏极区域104上方有n-硅单晶或窄禁带赝晶漏极区域103;在该n-漏极区域103上方是p+型沟道半导体区102;在该p+型沟道半导体区上方是n+窄禁带多晶半导体源极区域101;所述n+漏极区域104包括上部和下部,下部宽于上部,下部的下表面和侧面被p-well 105包围,在上述n+漏极区域104上部、n-漏极区域103、p+型沟道半导体区102以及n+窄禁带多晶半导体源极区域101的侧面设置有沟槽,沟槽的下表面低于n-漏极区域103和n+漏极区域104的界面,高于n+漏极区域104的下表面;沟槽内填充栅电极106和绝缘栅介质107。栅电极106由重掺杂多晶或耐熔金属硅化物或耐熔金属或他们的组合体构成。绝缘栅介质107用于隔离栅电极106和其他半导体区。漏电极108设置于n+窄禁带多晶半导体源极区域101、p+型沟道半导体区102、n-漏极区域103以及n+漏极区域104的侧面。绝缘材料109使得漏电极108与n+窄禁带多晶半导体源极区域101、p+型沟道半导体区102以及n-漏极103区域隔离。漏电极108与n+漏极区域104接触,该接触面低于n-漏极区域103和n+漏极区域104的界面。

8.本发明技术方案2为一种高集成度纳米墙集成电路结构,如图2所示。在该结构最下方为一个p-well硅单晶半导体区域105,在该p-well半导体区域105上部形成有nwafet的硅单晶n+漏极区域104;在该n+漏极区域104上方有n-硅单晶或窄禁带赝晶漏极区域103;在该n-漏极区域103上方有p+型沟道半导体区102;在该p+型沟道半导体区102上方是n+窄禁带多晶半导体源极区域101;所述n+漏极区域104包括上部和下部,下部宽于上部,下部的下表面和侧面被p-well 105包围,在上述n+漏极区域104上部、n-漏极区域103、p+型沟道半导体区102以及n+源极区域101的侧面设置有沟槽,沟槽的下表面低于p+型沟道半导体区102和n-漏极区域103的界面,高于n-漏极区域103和n+漏极区域104的界面。沟槽内填充栅电极106和绝缘栅介质107。栅电极106由重掺杂多晶或耐熔金属硅化物或耐熔金属或他们的组合体构成。绝缘栅介质107用于隔离栅电极106和其他半导体区。漏电极108设置于n+源极区域101、p+型沟道半导体区102、n-漏极区域103以及n+漏极区域104的侧面。绝缘材料109使得漏电极108与n+源极区域101、p+型沟道半导体区102以及n-漏极103区域隔离。漏电极108与n+漏极区域104接触,该接触面低于n-漏极区域103和n+漏极区域104的界面。

9.本发明技术方案3为一种高集成度纳米墙集成电路结构,如图3所示。在该结构最下方为一个p-well硅单晶半导体区域105,在该p-well半导体区域105上部形成有nwafet的硅单晶n+漏极区域104;在该n+漏极区域104上方有n-硅单晶或窄禁带赝晶漏极区域103;在该n-漏极区域103上方是p+型沟道半导体区102;在该p+型沟道半导体区102上方是n-硅单晶或窄禁带赝晶源极区域110;在该n-源极区域110的上方是n+窄禁带多晶半导体源极区域101;所述n+漏极区域104包括上部和下部,下部宽于上部,下部的下表面和侧面被p-well 105包围,在上述n+漏极区域104上部、n-漏极区域103、p+型沟道半导体区102、n-源极区域

110以及n+源极区域101的侧面设置有沟槽,沟槽的下表面低于n-漏极区域103和n+漏极区域104的界面,高于n+漏极区域104的下表面。沟槽内填充栅电极106和绝缘栅介质107。栅电极106由重掺杂多晶或耐熔金属硅化物或耐熔金属或他们的组合体构成。绝缘栅介质107用于隔离栅电极106和其他半导体区。漏电极108设置于n+源极区域101、n-源极区域110、p+型沟道半导体区102、n-漏极区域103、以及硅单晶n+漏极区域104的侧面。绝缘材料109使得漏电极108与n+源极区域101、p+型沟道半导体区102以及n-漏极103区域隔离。漏电极108与n+漏极区域104接触,该接触面低于n-漏极区域103和n+漏极区域104的界面。所述n-源极区域110掺杂浓度低于n+源极区域101及p+型沟道半导体区102。

10.本发明技术方案4为一种高集成度纳米墙集成电路结构,如图4所示。在该结构最下方为一个p-well硅单晶半导体区域105,在该p-well半导体区域105上部形成有nwafet的硅单晶n+漏极区域104;在该n+漏极区域104上方有n-硅单晶或窄禁带赝晶漏极区域103;在该n-漏极区域103上方有p+型沟道半导体区102;在该p+型沟道半导体区102上方是n-源极区域110;在该n-源极区域110的上方是n+窄禁带多晶半导体源极区域101;所述n+漏极区域104包括上部和下部,下部宽于上部,下部的下表面和侧面被p-well 105包围,在上述n+漏极区域104上部、n-漏极区域103、p+型沟道半导体区102、n-源极区域110以及n+源极区域101的侧面设置有沟槽,沟槽的下表面低于p+型沟道半导体区102和n-漏极区域103的界面,高于n-漏极区域103和n+漏极区域104的界面。沟槽内填充栅电极106和绝缘栅介质107。栅电极106由重掺杂多晶或耐熔金属硅化物或耐熔金属或他们的组合体构成。绝缘栅介质107用于隔离栅电极106和其他半导体区。漏电极108设置于n+源极区域101、n-源极区域110、p+型沟道半导体区102、n-漏极区域103、以及n+漏极区域104的侧面。绝缘材料109使得漏电极108与n+源极区域101、p+型沟道半导体区102以及n-漏极103区域隔离。漏电极108与n+漏极区域104接触,该接触面低于n-漏极区域103和n+漏极区域104的界面。所述n-源极区域110掺杂浓度低于n+源极区域101及p+型沟道半导体区102。

11.本发明技术方案5为一种高集成度纳米墙集成电路结构,如图5所示。在该结构最下方为一个n-well硅单晶半导体区域115,在该n-well半导体区域115上部形成有nwafet的硅单晶p+漏极区域114;在该p+漏极区域114上方有p-硅单晶或窄禁带赝晶漏极区域113;在该p-漏极区域113上方是n+型沟道半导体区112;在该n+型沟道半导体区112上方是p+窄禁带多晶半导体源极区域111;所述p+漏极区域114包括上部和下部,下部宽于上部,下部的下表面和侧面被n-well 115包围,在上述p+漏极区域114上部、p-漏极区域113、n+型沟道半导体区112以及p+源极区域111的侧面设置有沟槽,沟槽的下表面低于p-漏极区域113和p+漏极区域114的界面,高于p+漏极区域114的下表面。沟槽内填充栅电极106和绝缘栅介质107。栅电极106由重掺杂多晶或耐熔金属硅化物或耐熔金属或他们的组合体构成。绝缘栅介质107用于隔离栅电极106和其他半导体区。漏电极108设置于p+窄禁带多晶半导体源极区域111、n+型沟道半导体区112、p-漏极区域113以及p+漏极区域114的侧面。绝缘材料109与p+源极区域111、n+型沟道半导体区112以及p-漏极113区域隔离。漏电极108与p+漏极区域114接触,该接触面低于p-漏极区域113和p+漏极区域114的界面。

12.本发明技术方案6为一种高集成度纳米墙集成电路结构,如图6所示。在该结构最下方为一个n-well硅单晶半导体区域115,在该n-well半导体区域115上部形成有nwafet的硅单晶p+漏极区域114;在该p+漏极区域114上方有p-硅单晶或窄禁带赝晶漏极区域113;在

该p-漏极区域113上方有n+型沟道半导体区112;在该n+型沟道半导体区112上方是p+窄禁带多晶半导体源极区域111;所述p+漏极区域114包括上部和下部,下部宽于上部,下部的下表面和侧面被n-well 115包围,在上述p+漏极区域114上部、p-漏极区域113、n+型沟道半导体区112以及p+源极区域111的侧面设置有沟槽,沟槽的下表面低于n+型沟道半导体区112和p-漏极区域113的界面,高于p-漏极区域113的下表面。沟槽内填充栅电极106和绝缘栅介质107。栅电极106由重掺杂多晶或耐熔金属硅化物或耐熔金属或他们的组合体构成。绝缘栅介质107用于隔离栅电极106和其他半导体区。漏电极108设置于p+窄禁带多晶半导体源极区域111、n+型沟道半导体区112、p-漏极区域113以及p+漏极区域114的侧面。绝缘材料109使得漏电极108与p+源极区域111、n+型沟道半导体区112以及p-漏极113区域隔离。漏电极108与p+漏极区域114接触,该接触面低于p-漏极区域113和p+漏极区域114的界面。

13.本发明技术方案7为一种高集成度纳米墙集成电路结构,如图7所示。在该结构最下方为一个n-well硅单晶半导体区域115,在该n-well半导体区域115上部形成有nwafet的硅单晶p+漏极区域114;在该p+漏极区域114上方有p-硅单晶或窄禁带赝晶漏极区域113;在该p-漏极区域113上方是n+型沟道半导体区112;在该n+型沟道半导体区112上方是p-硅单晶或窄禁带赝晶源极区域116;在该p-源极区域116上方的是p+窄禁带多晶半导体源极区域111;所述p+漏极区域114包括上部和下部,下部宽于上部,下部的下表面和侧面被n-well 115包围,在上述p+漏极区域114上部、p-漏极区域113、n+型沟道半导体区112、p-源极区域116以及p+源极区域111的侧面设置有沟槽,沟槽的下表面低于p-漏极区域113和p+漏极区域114的界面,高于p+漏极区域114的下表面。沟槽内填充栅电极106和绝缘栅介质107。栅电极106由重掺杂多晶或耐熔金属硅化物或耐熔金属或他们的组合体构成。绝缘栅介质107用于隔离栅电极106和其他半导体区。漏电极108设置于p+窄禁带多晶半导体源极区域111、p-源极区域116、n+型沟道半导体区112、p-漏极区域113以及p+漏极区域114的侧面。绝缘材料109使得漏电极108与p+源极区域111、p-源极区域116、n+型沟道半导体区112以及p-漏极113区域隔离。漏电极108与p+漏极区域114接触,该接触面低于p-漏极区域113和p+漏极区域114的界面。所述p-源极区域116掺杂浓度低于p+源极区域111及n+型沟道半导体区112。

14.本发明技术方案8为一种高集成度纳米墙集成电路结构,如图8所示。在该结构最下方为一个n-well硅单晶半导体区域115,在该n-well半导体区域115上部形成有nwafet的硅单晶p+漏极区域114;在该p+漏极区域114上方有p-硅单晶或窄禁带赝晶漏极区域113;在该p-漏极区域113上方有n+型沟道半导体区112;在该n+型沟道半导体区112上方是p-硅单晶或窄禁带赝晶源极区域116;在该p-源极区域116上方的是p+窄禁带多晶半导体源极区域111;所述p+漏极区域114包括上部和下部,下部宽于上部,下部的下表面和侧面被n-well 115包围,在上述p+漏极区域114上部、p-漏极区域113、n+型沟道半导体区112、p-源极区域116以及p+源极区域111的侧面设置有沟槽,沟槽的下表面低于n+型沟道半导体区112和p-漏极区域113的界面,高于p-漏极区域113的下表面。沟槽内填充栅电极106和绝缘栅介质107。栅电极106由重掺杂多晶或耐熔金属硅化物或耐熔金属或他们的组合体构成。绝缘栅介质107用于隔离栅电极106和其他半导体区。漏电极108设置于p+窄禁带多晶半导体源极区域111、p-源极区域116、n+型沟道半导体区112、p-漏极区域113以及p+漏极区域114的侧面。绝缘材料109使得漏电极108与p+源极区域111、p-源极区域116、n+型沟道半导体区112以及p-漏极113区域隔离。漏电极108与p+漏极区域114接触,该接触面低于p-漏极区域113

和p+漏极区域114的界面。所述p-源极区域116掺杂浓度低于p+源极区域111及n+型沟道半导体区112。

15.进一步的,所述p+型沟道半导体区102的厚度小于12nm。

16.进一步的,所述p+型沟道半导体区102的掺杂浓度比n-漏极区域103高2个数量级以上。

17.进一步的,所述n+型沟道半导体区112的厚度小于12nm。

18.进一步的,所述n+型沟道半导体区112的掺杂浓度比p-漏极区域113高2个数量级以上。

19.进一步的,所述栅电极106设置于半导体区的一个侧面的全部区域、或半导体区的一个侧面的局部区域,如图13(a)所示。

20.进一步的,所述栅电极106设置于半导体区的两个侧面的全部区域、或半导体区的一个侧面的全部区域及另一个侧面的局部区域,如图13(b)所示。

21.进一步的,所述栅电极106设置于半导体区的三个侧面全部区域的、或半导体区的两个侧面的全部区域及另一个侧面的局部区域,如图13(c)所示。

22.进一步的,所述栅电极106设置于半导体区的四个侧面的全部区域、或半导体区的三个侧面的全部区域及最后一个侧面的局部区域,如图13(d)所示。

23.进一步的,当沟道半导体区(102,112)、重掺杂漏区(104,114)、半导体衬底或阱(105,115)为单晶硅时,所述轻掺杂漏区(103,113)、轻掺杂源区(110,116)为窄禁带赝晶半导体材料(如sige赝晶);当沟道半导体区(102,112)、重掺杂漏区(104,114)、半导体衬底或阱(105,115)为宽禁带单晶半导体材料(如sic单晶或gan单晶)时,所述轻掺杂漏区(103,113)、轻掺杂源区(110,116)为赝晶si半导体材料。在轻掺杂漏区及轻掺杂源区使用赝晶可以在沟道半导体(102、112)中引入应力,增加载流子的迁移率。

24.进一步的,当沟道半导体区(102,112)、重掺杂漏区(104,114)、半导体衬底或阱(105,115)为单晶硅时,所述重掺杂源区(101,111)为多晶ge、多晶sige、多晶tws(碲镉汞)、多晶inp、多晶insb等窄禁带半导体多晶材料,或上述材料的组合;当沟道半导体区(102,112)、重掺杂漏区(104,114)、半导体衬底或阱(105,115)为宽禁带单晶半导体材料(如sic单晶或gan单晶)时,所述重掺杂源区(101,111)为多晶si半导体材料。若重掺杂源区(101、111)采用窄禁带赝晶半导体材料,由于晶格失配产生应力,致使其厚度必须很薄,源区金属合金时可能穿透赝晶源区,造成器件失效。重掺杂源区采用多晶材料,没有晶格失配的问题,故其厚度可以较厚,从而避免了赝晶带来的问题。

25.所述栅极深度可以根据不同使用要求进行选择。以nmosfet为例,在低频应用下,栅极可以较深,栅极深度低于n-漏极区域103和n+漏极区域104的界面,高于n+漏极区域104的下表面,这种深度下新增的寄生电容并不会显著影响低频应用,但可以带来更低的导通电阻r

on

,有利于增加导通电流,增加晶体管的驱动能力;高频应用下,过大的寄生电容会显著影响晶体管性能,因此栅极不能过深,栅极深度低于n-漏极区域103和n+漏极区域104的界面,高于n+漏极区域104的下表面。

26.本发明提出的nwafet采用了与finfet和gaafet的全耗尽原理抑制dibl效应完全不同的机理。nwafet的沟道区采用高掺杂,沟道区的浓度高于n-漏极区域浓度,器件的bv

ds

由n-漏极区域的长度和浓度决定,避免了上述沟道区的高场效应,所以l

ch

可以缩到很小。漏

极耗尽区近似于只在漂移区中延伸,沟道区势垒形状几乎不变。故nwafet可以很好的抑制dibl效应,同时栅极也不必包裹沟道区,可在硅墙的一个侧面形成不漏电的mosfet,这相比finfet和gaafet的三面或四面沟道节省芯片面积,因此显著提升了ic的晶体管的集成度。

27.本发明基于新的抑制dibl效应的原理,提出了可实现单面沟道的nwafet结构。相比finfet和gaafet,nwafet的单面沟道较三面或四面沟道节省芯片面积,另外其l

ch

可以比finfet和gaafet的l

ch

要短很多。与传统平面mosfet相比,nwafet是立体结构,因此集成度显著提高。在数字ic方面,nwafet集成度和速度上的优势将会使得数字ic芯片性能更优异,芯片面积更小。在模拟ic方面,nwafet可以灵活方便地调整宽长比,同时在较高工作电压v

dd

条件下,其沟道长度l

ch

可以进一步缩短,因此在高频领域有广泛的应用前景。

附图说明

28.图1为本发明一种高集成度纳米墙集成电路结构无n-源极区域深栅槽nmosfet单元的斜视剖视图。

29.图2为本发明一种高集成度纳米墙集成电路结构无n-源极区域浅栅槽nmosfet单元的斜视剖视图。

30.图3为本发明一种高集成度纳米墙集成电路结构有n-源极区域深栅槽nmosfet单元的斜视剖视图。

31.图4为本发明一种高集成度纳米墙集成电路结构有n-源极区域浅栅槽nmosfet单元的斜视剖视图。

32.图5为本发明一种高集成度纳米墙集成电路结构无p-源极区域深栅槽pmosfet单元的斜视剖视图。

33.图6为本发明一种高集成度纳米墙集成电路结构无p-源极区域浅栅槽pmosfet单元的斜视剖视图。

34.图7为本发明一种高集成度纳米墙集成电路结构有p-源极区域深栅槽pmosfet单元的斜视剖视图。

35.图8为本发明一种高集成度纳米墙集成电路结构有p-源极区域浅栅槽pmosfet单元的斜视剖视图。

36.图9为本发明一种高集成度纳米墙集成电路结构nmosfet单元俯视图。

37.图10为本发明一种高集成度纳米墙集成电路结构pmosfet单元俯视图。

38.图11为本发明一种高集成度纳米墙集成电路结构无n-源极区域深栅槽nmosfet剖面图。

39.图12为本发明一种高集成度纳米墙集成电路结构无p-源极区域深栅槽pmosfet剖面图。

40.图13为本发明一种高集成度纳米墙集成电路结构单元槽栅电极106形成不同栅宽(w

ch

)mosfet的俯视图。

41.图14为实施例1的仿真结构剖面图。

42.图15为实施例1仿真得到的瞬态响应曲线。

43.图16为实施例2的仿真结构剖面图。

44.图17为实施例2仿真得到的转移特性曲线。

45.图18为实施例2仿真得到的输出特性曲线。

46.图19为实施例2仿真得到的频率响应曲线。

47.图20为实施例3的仿真结构剖面图。

48.图21为实施例3仿真得到的转移特性曲线。

49.图22为实施例3仿真得到的输出特性曲线。

50.图23为实施例4仿真得到的dibl值随p+沟道区掺杂浓度变化的曲线

51.图24位实施例5的仿真结构剖面图

52.图25为实施例5仿真得到的转移特性曲线。

53.图26为实施例5仿真得到的输出特性曲线。

具体实施方式

54.实施例1:

55.对于使用本发明技术方案3和技术方案7构造的cmos反相器进行了计算机三维仿真,仿真结构参见图14。对于nmosfet,其n+源极为硅,深度为20nm,掺杂浓度为1

×

10

20

cm-3

;n-源极深度为20nm,掺杂浓度为1

×

10

16

cm-3

;p+沟道深度为10nm,掺杂浓度为1

×

10

18

cm-3

;n-漏极深度为20nm,掺杂浓度为1

×

10

16

cm-3

;n+漏极深度为20nm,掺杂浓度为1

×

10

20

cm-3

;对于pmosfet,其p+源极深度为20nm,掺杂浓度为1

×

10

20

cm-3

;p-源极深度为20nm,掺杂浓度为1

×

10

16

cm-3

;n+沟道深度为10nm,掺杂浓度为1

×

10

18

cm-3

;p-漏极深度为20nm,掺杂浓度为1

×

10

16

cm-3

;p+漏极深度为20nm,掺杂浓度为1

×

10

20

cm-3

;栅极为多晶硅材料,深度深入n-漏极下表面之下2nm;栅极介质为二氧化硅,厚度为1nm;nmosfet沟道宽度为20nm,宽长比为2:1;pmosfet沟道宽度为nmosfet沟道宽度的3倍,即60nm,宽长比为6:1;两个晶体管漏极引出金属为钛,深度深入n-漏极下表面之下10nm。瞬态仿真的输入电压为周期变化的方波信号,输入低电平为0v,输入高电平为1.5v,从高到低和从低到高的电平转换时间均为1

×

10-11

s。

56.仿真结果参见说明书附图,图15为仿真得到的瞬态响应曲线。从仿真结果中可以看出,nmosfet和pmosfet共用栅极可实现cmos倒相器ic功能。在未经仔细优化情况下用10nm沟道长度的nwafet器件实现了倒相器ic开关时间均小于10ps。

57.实施例2:

58.对于使用本发明技术方案4的一种nmosfet结构进行了计算机三维仿真,仿真结构剖面图如图16所示。其中其n+源极为硅,深度为10nm,掺杂浓度为1

×

10

20

cm-3

;n-源极深度为20nm,掺杂浓度为1

×

10

17

cm-3

;p+沟道深度为0.543nm,掺杂浓度为2

×

10

20

cm-3

;n-漏极深度为20nm,掺杂浓度为1

×

10

17

cm-3

;n+漏极深度为10nm,掺杂浓度为1

×

10

20

cm-3

;栅极为多晶硅材料,深度深入p+沟道区下表面之下2nm;栅极介质为二氧化硅,厚度为1.1nm;栅极设置在功能区的一个侧面,对应沟道宽度为5nm,宽长比约为9.2:1。

59.仿真结果参见说明书附图,图17为仿真得到的转移特性曲线,图18为仿真得到的输出特性曲线,从仿真结果中可以看出,使用本发明技术方案4的nmosfet结构在沟道长度为0.543nm情况下能如预期得到晶体管特性,在源漏电压v

ds

为0.05v时计算得到的阈值电压为0.36v;开关比可达到1e6。图19为仿真得到的频率响应曲线,从仿真结果中可以看出,器件的截止频率ft为2.33thz。

60.实施例3:

61.对于使用本发明技术方案2的一种nmosfet结构进行了计算机三维仿真,仿真结构剖面图如图20所示。其中其n+源极为锗硅,深度为10nm,掺杂浓度为1

×

10

20

cm-3

;p+沟道深度为7nm,掺杂浓度为5

×

10

19

cm-3

;n-漏极深度为10nm,掺杂浓度为1

×

10

15

cm-3

;n+漏极深度为10nm,掺杂浓度为1

×

10

20

cm-3

;栅极为多晶硅材料,深度与p+沟道区下表面齐平;栅极介质为二氧化硅,厚度为2nm;栅极设置在功能区的三个侧面,对应沟道宽度为21nm,宽长比为3:1。

62.仿真结果参见说明书附图,图21为仿真得到的转移特性曲线,图22为仿真得到的输出特性曲线,从仿真结果中可以看出,使用本发明技术方案2的nmosfet可以如预期得到晶体管特性,在源漏电压v

ds

为1.2v时计算得到的阈值电压为0.7v;开关比可达到1e8。

63.实施例4:

64.对于使用本发明技术方案4的一种nmosfet结构进行了计算机三维仿真,仿真结构剖面图如图16所示。其中其n+源极为硅,深度为10nm,掺杂浓度为1

×

10

20

cm-3

;n-源极深度为10nm,掺杂浓度为1

×

10

17

cm-3

;p+沟道深度为0.543nm;n-漏极深度为10nm,掺杂浓度为1

×

10

17

cm-3

;n+漏极深度为10nm,掺杂浓度为1

×

10

20

cm-3

;栅极为多晶硅材料,深度深入p+沟道区下表面之下2nm;栅极介质为二氧化硅,厚度为1.1nm;栅极设置在功能区的四个侧面,对应沟道宽度为20nm,宽长比约为36.8:1。

65.图23展示了p+沟道区掺杂浓度从1

×

10

19

cm-3

增加到3

×

10

20

cm-3

时dibl值的变化。当p+沟道区掺杂浓度增大时,可以观察到dibl值逐渐减小,说明nwafet结构的高掺杂沟道区能有效抑制dibl效应。

66.实施例5:

67.对于使用本发明技术方案8的一种pmosfet结构进行了计算机三维仿真,仿真结构剖面图如图24所示。其中其p+源极为硅,深度为10nm,掺杂浓度为1

×

10

20

cm-3

;p-源极深度为20nm,掺杂浓度为1

×

10

16

cm-3

;n+沟道深度为10nm;p-漏极深度为20nm,掺杂浓度为1

×

10

16

cm-3

;p+漏极深度为10nm,掺杂浓度为1

×

10

20

cm-3

;栅极为多晶硅材料,深度深入n+沟道区下表面之下5nm;栅极介质为二氧化硅,厚度为3nm;栅极设置在功能区的四个侧面,对应沟道宽度为40nm,宽长比约为4:1。

68.仿真结果参见说明书附图,图25为仿真得到的转移特性曲线,图26为仿真得到的输出特性曲线,从仿真结果中可以看出,使用本发明技术方案8的pmosfet可以如预期得到晶体管特性,在源漏电压v

ds

为-2v时计算得到的阈值电压为-0.9v;开关比可达到1e8。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1