半导体器件、半导体器件封装体、照明设备和背光单元的制作方法

1.本发明涉及半导体技术领域,具体而言,涉及一种半导体器件、半导体器件封装体、照明设备和背光单元。

背景技术:

2.发光二极管(led,liquid crystal display)芯片在封装时,需要在芯片的焊盘电极层上印刷锡膏形成锡球电极,经过回流、清洗、测试高度,然后进行研磨、划裂、分选出货。其中,在进行锡膏印刷以及回流工艺时,使得焊盘电极的上层金属与锡膏形成金属间化合物,金属间化合物形成过程中相变所产生的残余应力会导致金属间化合物与电极接触的相对易碎部分的裂纹,从而会使锡膏与焊盘电极分离而形成孔隙。

技术实现要素:

3.有鉴于此,本发明的目的在于提供半导体器件、半导体器件封装体、照明设备和背光单元,以降低锡球电极内的孔隙率。

4.第一方面,本发明实施例提供了具有锡球电极的发光二极管,包括:发光结构,其包括n型层、p型层以及位于所述n型层与所述p型层之间的有源层;以及互连凸块,其包括:焊盘电极,其位于n型层和p型层中的至少一个电极上,焊料凸块,其键合至所述焊盘电极;所述互连凸块的孔隙率≤5%。

5.结合第一方面,本发明实施例提供了第一方面的第一种可能的实施方式,其中,所述焊盘电极包括多层金属层,其最上层金属层为au层,所述焊料凸块与所述au层直接接触,所述au层厚度为

6.结合第一方面的第一种可能的实施方式,本发明实施例提供了第一方面的第二种可能的实施方式,其中,所述互连凸块的孔隙率≤3%,所述可能的实施方式,其中,所述互连凸块的孔隙率≤3%,所述

7.结合第一方面,本发明实施例提供了第一方面的第三种可能的实施方式,其中,所述焊盘电极包括凸块下冶金层,以及位于所述凸块下冶金层与所述焊料凸块之间的金属间化合物层,所述金属间化合物层与所述焊料凸块之间的孔隙率≤5%。

8.结合第一方面的第三种可能的实施方式,本发明实施例提供了第一方面的第四种可能的实施方式,其中,所述金属间化合物顺次包括ti层、ni层、au层,所述ti层厚度为所述ni层厚度为所述au层厚度为

9.结合第一方面的第四种可能的实施方式,本发明实施例提供了第一方面的第五种可能的实施方式,其中,所述金属间化合物层与所述焊料凸块之间的孔隙率≤3%,所述

10.结合第一方面的第三种可能的实施方式,本发明实施例提供了第一方面的第六种可能的实施方式,其中,所述凸块下冶金层包括粘结层、金属反射层以及包覆层,所述焊料凸块为sn。

11.第二方面,本发明实施例还提供了一种半导体器件,包括:

12.发光结构,具有多个电极;以及与所述多个电极电性连接的互连凸块,其中,所述互连凸块包括位于所述电极上的焊盘电极,键合至所述焊盘电极上的焊料凸块,所述互连凸块的孔隙率≤5%。

13.结合第二方面,本发明实施例提供了第二方面的第一种可能的实施方式,其中,所述发光结构包括n型层、p型层,以及位于所述n型层和所述p型层之间的有源层;所述多个电极在所述发光结构的同一侧,包括分别与所述n型层和所述p型层电性连接的多个第一n电极和多个第一p电极;

14.焊盘电极包括分别电性连接多个第一n电极和多个第一p电极的n电极焊盘和p电极焊盘。

15.第三方面,本技术实施例提供了一种半导体器件封装件,包括:

16.封装件主体;

17.封装件主体上的半导体器件;以及对所述半导体器件进行包封的包封部分,

18.其中所述半导体器件如上任意一项所示。

19.结合第三方面,本发明实施例提供了第三方面的第一种可能的实施方式,其中,所述包封部分至少包括一磷光体。

20.第四方面,本技术实施例提供了一种照明设备,包括:

21.壳体;以及如上所述的半导体器件封装件。

22.第五方面,本技术实施例提供了一种背光元件,包括背光板,以及如上所述的半导体器件封装件。

23.本发明实施例提供的半导体器件、半导体器件封装体、照明设备和背光单元,半导体器件包括:发光结构,其包括n型层、p型层以及位于所述n型层与所述p型层之间的有源层;以及互连凸块,其包括:焊盘电极,其位于n型层和p型层中的至少一个电极上,焊料凸块,其键合至所述焊盘电极;所述互连凸块的孔隙率≤5%。这样,通过控制互连凸块的孔隙率≤5%,从而降低锡内部形成的孔洞。

24.为使本发明的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

附图说明

25.为了更清楚地说明本发明实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本发明的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

26.图1示出了本发明实施例一所提供的半导体器件剖视结构示意图;

27.图2示出了本发明实施例一所提供的半导体器件俯视结构示意图;

28.图3示出了本发明实施例一所提供的互连凸块结构示意图;

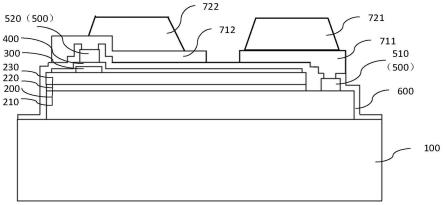

29.图4示出了本发明实施例二所提供的半导体器件剖视结构示意图;

30.图5示出了本发明实施例二所提供的半导体器件俯视结构示意图;

31.图6示出了本发明实施例二所提供的互连凸块700结构示意图;

32.图7示出了本发明实施例二所提供的互连凸块700另一结构示意图;

33.图8示出了本发明实施例所提供的半导体器件封装件结构示意图;

34.图9示出了本发明实施例所提供的背光单元结构示意图;

35.图10示出了本发明实施例所提供的背光单元另一结构示意图;

36.图11示出了本发明实施例所提供的照明设备分解结构示意图;

37.图12示出了本发明实施例所提供的照明设备另一分解结构示意图;

38.图13(a)为样品1(au厚度为)的焊盘电极经过抛销后内部孔洞图片;图13(b)为样品2(au厚度为)的焊盘电极经过抛销后内部孔洞图片;图13(c)为样品3(au厚度为)的焊盘电极经过抛销后内部孔洞图片;

39.附图标注:

40.100:衬底;200:发光结构;210:n型层;220:有源层;230:p型层;300:阻挡层;400:透明导电层;500:电极;510:第一n电极;520:第一p电极;530:第二n电极;540:第二p电极;600:绝缘层;700:互连凸块;701:au层;704:ti层;705:ni层;702:金属反射层;703:包覆层;710:焊盘电极;711:n型焊盘电极;712:p型焊盘电极;720:焊料凸块;721:n型焊料凸块;722:p型焊料凸块;800:保护层;810:通孔;7100:凸块下冶金层;7200:金属间化合物层;1000:半导体器件;2000:安装衬底;7000:包封部分;2100:第一电路图案;2200:第二电路图案;3000:第一背光单元;3001:第一光源;4000:第二背光单元;4002:衬底;4001:第二光源;4003:导光板;4004:反射层;5000:照明设备;5010:发光模块;5020:驱动单元;5030:连接单元;5040:外部壳体;5050:内部壳体;5060:盖体单元;5011:半导体器件;5012:电路衬底;5041:散热板;5042:散热片;6000:照明设备;6010:发光模块;6020:主体单元;6030:盖体单元;6040:端子单元;6012:衬底;6011:半导体器件;6021:凹进;6022:散热鳍片;6023:紧固凹槽;6031:突出部分;6041:电极销。

具体实施方式

41.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本发明实施例的组件可以以各种不同的配置来布置和设计。因此,以下对在附图中提供的本发明的实施例的详细描述并非旨在限制要求保护的本发明的范围,而是仅仅表示本发明的选定实施例。基于本发明的实施例,本领域技术人员在没有做出创造性劳动的前提下所获得的所有其他实施例,都属于本发明保护的范围。

42.本发明实施例提供了一种半导体器件、半导体器件封装体、照明设备和背光单元,下面通过实施例进行描述。

43.图1示出了本发明实施例一所提供的半导体器件剖视结构示意图;

44.图2示出了本发明实施例一所提供的半导体器件俯视结构示意图;

45.图3示出了本发明实施例一所提供的互连凸块结构示意图。

46.参见图1至图3,该半导体器件包括:发光结构200,其包括n型层210、p型层230以及位于n型层210与p型层230之间的有源层220;以及

47.互连凸块(图中未示出),其包括:焊盘电极710,其位于n型层210和p型层230中的至少一个电极500上,

48.焊料凸块720,其键合至焊盘电极710;

49.互连凸块的孔隙率≤5%。

50.本发明实施例中,作为一可选实施例,焊盘电极710包括多层金属层,其最上层金属层为au层,焊料凸块720与au层直接接触,au层厚度为

51.本发明实施例中,焊盘电极710最上层金属层为金(au),au和焊料凸块720形成ausn合金,通过控制金层的厚度来控制形成ausn合金的反应,从而对锡球电极内的孔隙率进行控制。本发明实施例中,设置au层的厚度为在该厚度范围内,能够有效减少金与锡的反应,从而降低在回流过程中锡内部形成的孔洞,减少空洞导致的漏电,优化led芯片的电性能,又能保障焊料凸块720与焊盘电极710的粘附力,避免焊料凸块720从焊盘电极710上脱落。

52.本发明实施例中,作为一可选实施例,互连凸块的孔隙率≤3%,本发明实施例中,作为一可选实施例,互连凸块的孔隙率≤3%,

53.本发明实施例中,作为一可选实施例,该半导体器件还包括:

54.阻挡层300,沉积在p型层230上;

55.透明导电层400,沉积在阻挡层300以及p型层230上;

56.第一n电极510,沉积在n型层210上;

57.第一p电极520,沉积在对应阻挡层300位置的透明导电层400上;

58.绝缘层600,沉积在n型层210、衬底100、第一n电极510、透明导电层400、第一p电极520上;

59.p型焊盘电极712,沉积在绝缘层600上,与第一p电极520电性连接;

60.n型焊盘电极711,沉积在绝缘层600上,与第一n电极510电性连接;

61.p型焊料凸块722,沉积在p型焊盘电极712上;以及,

62.n型焊料凸块721,沉积在n型焊盘电极711上。

63.图4示出了本发明实施例二所提供的半导体器件剖视结构示意图;

64.图5示出了本发明实施例二所提供的半导体器件俯视结构示意图;

65.图6示出了本发明实施例二所提供的互连凸块700结构示意图;

66.图7示出了本发明实施例二所提供的互连凸块700另一结构示意图。

67.如图4至图7所示,该实施例的半导体器件包括:

68.发光结构200,具有多个电极500;以及与多个电极500电性连接的互连凸块700,其中,互连凸块700包括位于电极500上的焊盘电极710,键合至焊盘电极710上的焊料凸块720,互连凸块700的孔隙率≤5%。

69.本发明实施例中,作为一可选实施例,发光结构200包括n型层210、p型层230,以及位于n型层210和p型层230之间的有源层220;多个电极500在发光结构200的同一侧,包括分别与n型层210和p型层230电性连接的多个第一n电极510和多个第一p电极520;

70.焊盘电极710包括分别电性连接多个第一n电极510和多个第一p电极520的n型焊盘电极711和p型焊盘电极712。

71.本发明实施例中,作为一可选实施例,该实施例的半导体器件还包括:

72.阻挡层300,沉积在p型层230上;

73.透明导电层400,沉积在阻挡层300以及p型层230上;

74.第二n电极530,位于第一n电极510上;

75.第二p电极540,位于第一p电极520上;

76.绝缘层600,沉积在n型层210、衬底100、第一n电极510、透明导电层400、第一p电极520上;

77.保护层800,沉积在第二p电极540以及第二n电极530上;

78.p型焊料凸块722,沉积在p型焊盘电极712上;以及,

79.n型焊料凸块721,沉积在n型焊盘电极711上。

80.本发明实施例中,作为一可选实施例,焊盘电极710包括凸块下冶金层7100,以及位于凸块下冶金层7100与焊料凸块720之间的金属间化合物层7200,金属间化合物层7200与焊料凸块720之间的孔隙率≤5%。

81.本发明实施例中,作为一可选实施例,金属间化合物层7200顺次包括ti层704、ni层705、au层701,ti层704厚度为ni层705厚度为au层701厚度为

82.本发明实施例中,作为一可选实施例,金属间化合物层7200与焊料凸块720之间的孔隙率≤3%,

83.本发明实施例中,作为一可选实施例,凸块下冶金层7100包括粘结层、金属反射层702以及包覆层703,焊料凸块720为sn。其中,作为一可选实施例,粘结层为au层701。

84.图8示出了本发明实施例所提供的半导体器件封装件结构示意图。如图8所示,该半导体器件封装件包括:

85.封装件主体(图中未示出);

86.封装件主体上的半导体器件1000;以及对半导体器件1000进行包封的包封部分7000,

87.其中半导体器件1000如上任意所示。

88.包封部分7000至少包括一磷光体。

89.本发明实施例中,半导体器件封装件包括:半导体器件1000、安装衬底2000和包封部分7000。其中,半导体器件1000可安装在安装衬底2000上,以电连接至第一电路图案2100和第二电路图案2200。半导体器件的n型焊盘电极711和p型焊盘电极712分别通过n型焊料凸块721和p型焊料凸块722电连接至第一电路图案2100和第二电路图案2200。

90.本发明实施例中,半导体器件可由包封部分7000包封,通过这种方式,可提供板上芯片(cob,chip on board)型封装件结构。作为一可选实施例,可将安装衬底2000提供为诸如印刷电路板(pcb,printed circuit board)、金属芯印刷电路板(mcpcb,metal core pcb)、多层印刷电路板(mpcb,mulitlayer printed circuit board)或柔性印刷电路板(fpcb,flexible printed circuit board)的衬底,并且可按照多种不同的方式对安装衬底2000的结构进行应用。

91.本发明实施例中,作为另一可选实施例,可在包封部分7000中包含波长转换材料。其中,波长转换材料可包含受到半导体器件所产生的光的激发而发光的磷光体中的至少一种,以发射具有与半导体器件所产生的光的波长不同的波长的光。因此,可对光的发射进行控制以使其具有包括白光在内的不同颜色。

92.图9示出了本发明实施例所提供的背光单元结构示意图;

93.图10示出了本发明实施例所提供的背光单元另一结构示意图。

94.如图9和图10所示,作为一可选实施例,第一背光单元3000中的第一光源3001可沿着设置液晶显示(lcd,liquid crystal display)器件的方向向上发射光。第二背光单元4000中,安装在衬底4002上的第二光源4001可在横向方向上发光,从而使发射的光可入射至导光板4003上,以将其转换为表面光源的形式。已穿过导光板4003的光可向上消散,并且反射层4004可设置在导光板4003下方以提高光提取效率。

95.图11示出了本发明实施例所提供的照明设备分解结构示意图。如图11所示,该实施例的照明设备包括:

96.壳体;以及如上所述的半导体器件封装件。

97.本发明实施例中,照明设备5000为灯泡型照明器,包括:发光模块5010、驱动单元5020和外部连接单元5030。作为另一可选实施例,照明设备5000还可包括:外部壳体5040、内部壳体5050和盖体单元5060的外部结构。

98.本发明实施例中,光模块5010可包括具有与半导体器件100相同或相似的结构的半导体器件5011以及其上安装有半导体器件5011的电路衬底5012。在示例实施例中,示例了单个半导体器件5011安装在电路衬底5012上的示例;然而,根据需要,可将多个半导体器件5011安装在电路衬底5012上。作为另一可选实施例,半导体器件5011可以不直接安装在电路衬底5012上,可在按照图8所示的封装件形式进行制造之后,将其安装在电路衬底5012上。

99.本发明实施例中,外部壳体5040可用作散热单元,并且可包括与发光模块5010直接接触以提高散热效果的散热板5041以及包围外部壳体5040的侧表面的散热片5042。

100.本发明实施例中,盖体单元5060可安装在发光模块5010上,并且可具有凸透镜形状。驱动单元5020可安装在内部壳体5050中,并且可连接至诸如插座结构的外部连接单元5030以从外部提供功率。作为一可选实施例,驱动单元5020可将功率转换为用于对发光模块5010的半导体器件5011进行驱动的合适的电流源,并且可提供经转换的电流源。例如,驱动单元5020可配置为交流-直流(ac-dc)转换器或整流器电路组件。

101.图12示出了本发明实施例所提供的照明设备另一分解结构示意图。如图12所示,该实施例的照明设备包括:

102.背光元件,包括背光板,以及如上所述的半导体器件封装件。

103.本发明实施例中,作为一可选实施例,照明设备6000为条型灯,并且可包括发光模块6010、主体单元6020、盖体单元6030、端子单元6040。其中,发光模块6010可包括衬底6012和安装在衬底6012上的多个半导体器件6011。半导体器件6011可为图5的半导体器件或者图8的半导体器件封装件,可利用凹进6021将发光模块6010安装并固定在主体单元6020的一个表面上,并且可向外消散发光模块6010所产生的热。作为一可选实施例,主体单元6020可包括作为一种支承结构的散热器,并且可包括用于散热的多个散热鳍片6022,其提供在主体单元6020的两个横向表面上同时从其上突出。

104.盖体单元6030可紧固至主体单元6020的紧固凹槽6023,并且可具有半圆形曲面,以允许光均匀地向外消散。与壳体6020的紧固凹槽6023接合的突出部分6031可沿着主体单元6020的长度方向形成在盖体单元6030的底表面上。

105.本发明实施例中,作为一可选实施例,可在主体单元6020的开口端部中沿着主体单元6020的长度方向提供端子单元6040,并且可以向发光模块6010提供功率。端子单元

6040可包括向外突出的电极销6041。

106.对比例:

107.本对比例中的3款样品的除焊盘电极中au层厚度不同外,其它的结构、制备方法均相同,3款样品经过x-ray机台试验验证,测试得到的孔隙率数据如表1所示。

108.表1

[0109][0110]

由表1可见,当表层au较厚(不小于)时,ausn互溶会增多,从而引起锡膏中气泡增多,孔隙率较高;在表层au较薄(小于)时,锡膏中的孔隙率较低。表层au厚度在可以使得孔隙率小于5%。这样,通过对锡球电极结构中金层厚度的配比,能有效降低锡球电极中,锡膏和au层接触界面的孔隙率。

[0111]

图13(a)为样品1(au厚度为)的焊盘电极经过抛销后内部孔洞图片;图13(b)为样品2(au厚度为)的焊盘电极经过抛销后内部孔洞图片;图13(c)为样品3(au厚度为)的焊盘电极经过抛销后内部孔洞图片;

[0112]

如图13(a)、13(b)、13(c)所示,au厚度为时,焊盘电极内部的孔洞(即黑色部分)最少,au厚度为时孔洞最多,直观的图片显示结果与通过x-ray机台试验验证的结果相互对应。

[0113]

在本技术所提供的实施例中,应该理解到,所揭露系统和方法,可以通过其它的方式实现。以上所描述的系统实施例仅仅是示意性的,例如,所述单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,又例如,多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些通信接口,系统或单元的间接耦合或通信连接,可以是电性,机械或其它的形式。

[0114]

所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目的。

[0115]

另外,在本技术提供的实施例中的各功能单元可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。

[0116]

所述功能如果以软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。基于这样的理解,本技术的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行本技术各个实施例所述方法的全部或部分步骤。而前述的存储介质包括:u盘、移动硬盘、只读存储器(read-only memory,rom)、随机存取存储器(random access memory,ram)、磁碟或者光盘等各种可以存储程序代码的介质。

[0117]

应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释,此外,术语“第一”、“第二”、“第三”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

[0118]

最后应说明的是:以上所述实施例,仅为本技术的具体实施方式,用以说明本技术的技术方案,而非对其限制,本技术的保护范围并不局限于此,尽管参照前述实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,其依然可以对前述实施例所记载的技术方案进行修改或可轻易想到变化,或者对其中部分技术特征进行等同替换;而这些修改、变化或者替换,并不使相应技术方案的本质脱离本技术实施例技术方案的精神和范围。都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应所述以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1