低复合隧穿氧化钝化层结构及应用的制作方法

1.本发明属于光伏电池技术领域,具体涉及一种低复合隧穿氧化钝化层结构及应用。

背景技术:

2.随着光伏电池研究的不断深入,各种不同结构的高效光伏电池结构应运而生,同时光伏电池转换效率逐渐接近理论极限。目前主流的商业化光伏电池为perc光伏电池,该电池结构对发射极及电池背面进行了钝化,采用局域背电极接触的方式降低了电极接触复合,对电池转换效率有一定的该改善。然而电极与晶硅的接触区域仍然存在较高的复合率,影响了电池转换效率的进一步提高。

3.为进一步提升硅表面及电极接触区域的钝化效果,隧穿氧化钝化光伏电池(topcon)在电极与硅之间增加一层超薄氧化层和掺杂的多晶硅作为钝化接触层。该结构可以同时对硅表面形成化学钝化和场钝化,降低表面缺陷密度的同时,增强了载流子的选择性接触,降低载流子复合。

4.目前常用的隧穿氧化钝化层为sio2/poly-si复合结构,根据隧穿钝化层所钝化的si表面掺杂类型对poly-si进行相应的掺杂。topcon结构是隧穿氧化层和掺杂多晶硅的复合结构,若多晶硅的掺杂种类为p型,则称为p型topcon,若多晶硅的掺杂种类为n型,则称为n型topcon。当被钝化的硅表面为n型时,对poly-si进行磷掺杂;当被钝化的硅表面为p型时,对poly-si进行硼掺杂。该结构中sio2对硅片表面的悬挂键进行钝化(化学钝化),掺杂poly-si与si形成高低结,阻挡少数载流子,起到场钝化的作用。在sio2/poly-si复合钝化层的作用下,topcon电池的实验室效率已突破25%。

5.但是利用磷或硼对poly-si进行掺杂时,杂质原子会通过氧化层扩散入体硅中,引起载流子的复合,削弱钝化效果。由于硼在sio2中的扩散系数大于磷在sio2中的扩散系数,且硼在sio2/si界面的分凝系数大于磷在sio2/si界面的分凝系数,因此,硼原子比磷原子更容易穿过氧化层进入体硅中。实验表明,poly-si/sio2/si结构中,通过氧化层扩散入体硅的硼原子浓度在同一深度处约为磷原子浓度的1.3倍,氧化层与硅的界面处积累的硼原子浓度约为磷原子浓度的20倍。所以,对于p型或n型topcon结构中的隧穿氧化层需要做出针对性的改进。

技术实现要素:

6.本发明要解决的技术问题是:提供一种低复合隧穿氧化钝化层结构,利用含氮二氧化硅代替topcon结构中的sio2作为隧穿氧化层,提高了隧穿氧化层对杂质原子的阻挡能力,降低由于多晶硅层中硼或磷原子的扩散而引起的载流子的复合,充分发挥了隧穿氧化钝化结构的钝化作用,提高了topcon结构的钝化效果;本发明还提供其应用。

7.本发明所述的低复合隧穿氧化钝化层结构,由厚度为1~1.2nm的氧化层和厚度为50~80nm的掺杂多晶硅层组成,所述氧化层为含氮二氧化硅;

所述低复合隧穿氧化钝化层结构用于p型topcon电池或n型topcon电池的背面,所述p型topcon电池或n型topcon电池的结构包括晶硅,和依次设置在晶硅正面的半导体区、重掺杂区、正面钝化层、正面电极,以及依次设置在晶硅背面的隧穿氧化层、多晶硅层、背面钝化层、背面电极。

8.优选的,正面钝化层为si3n4层;背面钝化层为al2o3/si3n4复合层。

9.优选的,所述含氮二氧化硅是以n2o为前驱体,采用低压化学气相沉积(lpcvd)或等离子体氧化法或等离子体增强化学气相沉积法(pecvd)制得,也可以由其他方法制备得到。

10.优选的,含氮二氧化硅化学式为sio

x

ny,其中0<x<2,0<y<2。

11.优选的,所述掺杂多晶硅层为硼或磷掺杂多晶硅。

12.优选的,所述掺杂多晶硅采用等离子体增强化学气相沉积法(pecvd)或低压气相淀积法(lpcvd)进行掺杂制得,也可以由其他方法制备得到;可以是原位掺杂,也可以是先沉积多晶硅层后进行掺杂。

13.所述低复合隧穿氧化钝化层结构用于p型topcon电池背面时,包括以下步骤:

①ꢀ

p型晶硅正面进行磷扩散,形成n型半导体区,通过激光进行选择性重掺杂,形成重掺杂区;

②ꢀ

去除背面和侧面的磷硅玻璃和pn结,并对背面进行抛光;

③ꢀ

p型晶硅的背面沉积隧穿氧化层,该隧穿氧化层为含氮的二氧化硅,厚度1~1.2nm;

④ꢀ

隧穿氧化层上沉积多晶硅层,并进行硼掺杂,厚度50~80nm;

⑤ꢀ

去除n型半导体区表面绕镀的多晶硅和磷硅玻璃,然后沉积正面钝化层;

⑥ꢀ

多晶硅层表面沉积背面钝化层;

⑦ꢀ

正面的选择性重掺杂区印刷正面电极,同时背面印刷背面电极,高温烧结。

14.所述低复合隧穿氧化钝化层结构用于n型topcon电池背面时,包括以下步骤:

①ꢀ

n型晶硅正面进行硼扩散,形成p型半导体区,通过激光进行选择性重掺杂,形成重掺杂区;

②

去除背面和侧面的硼硅玻璃和pn结,并对背面进行抛光;

③ꢀ

n型晶硅的背面沉积隧穿氧化层,该隧穿氧化层为含氮的二氧化硅,厚度1~1.2nm;

④ꢀ

隧穿氧化层上沉积多晶硅层,并进行磷掺杂,厚度50~80nm;

⑤ꢀ

去除p型半导体表面绕镀的多晶硅和硼硅玻璃,然后沉积正面钝化层;

⑥ꢀ

多晶硅层表面沉积背面钝化层;

⑦ꢀ

正面的选择性重掺杂区印刷正面电极,同时背面印刷背面电极,高温烧结。

15.在沉积隧穿氧化层时,以pecvd法为例,采用sih4和n2o为前驱体,n2o:sih4流量设为(2-3):1,沉积温度为300~400℃,沉积时间为1~10min。

16.现有技术以sio2作为隧穿氧化钝化结构中的隧穿氧化层,沉积掺杂多晶硅时杂质原子容易穿透sio2进入体硅中,造成一定的载流子复合损失,降低隧穿氧化钝化技术的钝化效果。以p型topcon结构为例,由于硼原子在si中扩散系数较大,且在si/sio2界面的分凝系数约为3/10,因此硼原子更容易穿过多晶硅层经超薄的氧化硅层进入体硅内部,且在si/

sio2界面的sio2表面形成大量的硼原子积累,引起载流子复合。

17.本发明针对p型或n型topcon结构,用含氮sio2(sio

x

ny)代替sio2作为隧穿氧化层,提高了隧穿氧化层对硼或磷杂质原子的阻挡作用,避免大量杂质原子进入体硅而引起载流子复合。

18.以p型topcon结构为例,硼原子在sin

x

中的扩散系数小于在sio2中扩散系数,在sio2中引入n原子可以与b原子形成结合能更大的b

+-n键,限制了b原子在sio2中的移动;同时硼原子在si/sio

x

ny界面的分凝系数大于其在si/sio2界面的分凝系数,避免了硼原子在隧穿氧化层/多晶硅界面处的隧穿氧化层中的积累。因此对sio2层进行氮化形成含氮的sio2(sio

x

ny)可以在一定程度上增强隧穿氧化层对硼原子的阻挡作用,减少扩散入体硅内部的硼原子及硼原子在隧穿氧化层/多晶硅界面处的积累,实现钝化效果的提升。

19.与现有技术相比,本发明的有益效果如下:本发明利用含氮二氧化硅(sio

x

ny)代替topcon结构中的sio2作为隧穿氧化层,提高了隧穿氧化层对硼或磷杂质原子的阻挡能力,降低由于多晶硅层中杂质原子的扩散而引起的载流子的复合,充分发挥了隧穿氧化钝化结构的钝化作用,提高了topcon结构的钝化效果。

附图说明

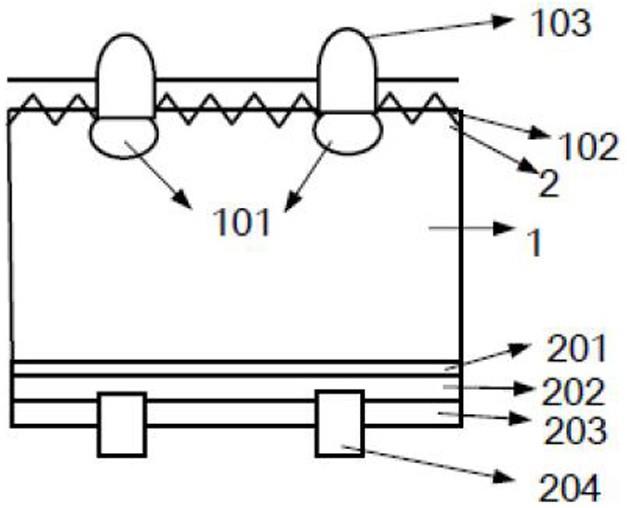

20.图1为本发明topcon电池的低复合隧穿氧化钝化层结构示意图;图中:1、晶硅;2、半导体区;101、重掺杂区;102、正面钝化层;103、正面电极;201、隧穿氧化层;202、多晶硅层;203、背面钝化层;204、背面电极。

具体实施方式

21.下面结合实施例对本发明做出进一步说明,但本发明的保护范围不仅限于此,该领域专业人员对本发明技术方案所作的改变,均应属于本发明的保护范围内。

22.实施例中所使用的原料,如无特别说明,均为市售常规原料;实施例中所使用的工艺方法,如无特别说明,均为本领域常规方法。

23.实施例1采用本发明的低复合隧穿氧化钝化层结构,由1nm的含氮二氧化硅层和80nm的硼掺杂多晶硅层组成。

24.将上述低复合隧穿氧化钝化层结构用于p型topcon电池,包括以下步骤:

①ꢀ

p型晶硅清洗、制绒,形成金字塔陷光结构;在p型晶硅正面进行磷扩散,在850℃下扩散80min,形成n型半导体区;用脉冲激光器对扩散后的n型半导体区表面进行选择性重掺杂处理,形成重掺杂区。

25.②ꢀ

p型晶硅正面在650℃温度下进行氧化,氧化时间2min,形成厚度约2nm的氧化层,然后经酸性刻蚀液去除p型晶硅背面的psg,再在碱性抛光液中对p型晶硅背面进行抛光,温度为70℃,时间为5min,清洗并烘干。

26.③ꢀ

p型硅片置于pecvd沉积腔室,先通入n2,对腔室进行清洗,抽真空后通入sih4和n2o,流量比设为1:2,设定温度为400℃,射频功率为50w,沉积2min得到厚度约为1nm的sion薄膜。

27.④ꢀ

排除腔室内残余气体,通入n2对腔室进行清洗,抽真空后通入sih4、h2和b2h6,射频功率为80w,温度为450℃,沉积得到厚度为80nm的硼掺杂多晶硅层;之后通入流量比为10:1的sih4和n2o气体,在50w射频功率和400℃温度下沉积10min得到厚度为8nm的sio2薄膜作为掩蔽层。

28.⑤ꢀ

硅片置于碱性刻蚀剂中,去除正面绕镀的多晶硅层,然后用hf和hno3的混合溶液去除样片正面的氧化层及psg层,清水清洗后烘干;硅片正面用pecvd方式沉积正面钝化层,源气体为sih4和nh3,流量比为1:3,沉积功率50w,沉积时间10min,得到厚度为80nm的si3n4薄膜。

29.⑥ꢀ

硅片背面用pecvd沉积背面钝化层,腔室升温至300℃后,通入n2o和tma气体,流量比为10:1,20w射频功率下沉积3min,然后升温至400℃在nh3和n2o气氛下保持2min;清洗腔室后通入sih4和nh3,流量比为1:4,在50w射频共下沉积4min后逐渐改变流量比为1:10,沉积8min,形成厚度为120nm的al2o3/si3n4复合钝化膜。

30.⑦ꢀ

激光处理背面钝化层,在印刷电极区域开窗,分别印刷背面和正面的电极栅线,并于800℃烧结,形成良好的欧姆接触。

31.对比例1采用二氧化硅作为隧穿氧化层,用于p型topcon电池,包括以下步骤:

①ꢀ

p型晶硅清洗、制绒,形成金字塔陷光结构;在p型晶硅正面进行磷扩散,在850℃下扩散80min,形成n型半导体区。

32.②ꢀ

经酸性刻蚀液去除p型晶硅背面的psg,再在碱性抛光液中对p型晶硅背面进行抛光,温度为70℃,时间为5min,清洗并烘干。

33.③ꢀ

p型硅片置于lpcvd沉积腔室,降低腔室气压至130pa,并升温至650℃,后通入n2o、nh3、sih4,在700℃保持1min,使p型硅片两面均形成厚度约为1.3nm的sio2薄膜;排除腔室内残余气体,用n2对腔室进行清洗后升温至625℃,后通入sih4和n2,沉积50min,使p型硅片两面均形成厚度约为80nm的多晶硅薄层。

34.④ꢀ

通过热扩散方式,在背面的多晶硅中进行硼扩散并退火,正面的多晶硅中进行磷扩散并退火;之后用hf和hno3的混合溶液去除硅片两面的bsg层及psg层,清水清洗后烘干。

35.⑤ꢀ

硅片背面用pecvd沉积背面钝化层,腔室升温至300℃后,通入n2o和tma气体,流量比约为10:1,20w射频功率下沉积3min,然后升温至400℃在nh3和n2o气氛下保持2min;清洗腔室后通入sih4和nh3,流量比约为1:4,在50w射频下沉积4min后逐渐改变流量比为1:10,沉积8min。形成厚度约为120nm的al2o3/si3n4复合钝化膜。

36.⑥ꢀ

硅片正面用pecvd方式沉积正面钝化层,源气体为sih4和nh3,流量比约为1:3,沉积功率约为50w,沉积时间10min得到厚度约为80nm的si3n4薄膜。

37.⑦ꢀ

分别印刷背面和正面的电极栅线,并于800℃烧结,形成良好的欧姆接触。

38.与对比例1相比,实施例1采用含氮二氧化硅(sio

x

ny)代替topcon结构中的sio2作为隧穿氧化层,提高了隧穿氧化层对硼或磷杂质原子的阻挡能力,降低由于多晶硅层中杂质原子的扩散而引起的载流子的复合,充分发挥了隧穿氧化钝化结构的钝化作用,提高了topcon结构的钝化效果,可以使光伏电池背面复合电流从20~50 fa/cm2降低至5~10 fa/cm2,大大提升了电池的性能。

39.实施例2采用本发明的低复合隧穿氧化钝化层结构,由1.2nm的含氮二氧化硅层和50nm的磷掺杂多晶硅层组成。

40.将上述低复合隧穿氧化钝化层结构用于n型topcon电池,包括以下步骤:

①ꢀ

n型晶硅清洗、制绒,形成金字塔陷光结构;在n型晶硅正面进行硼扩散,在1050℃下扩散120min,形成p型半导体区;用脉冲激光器对扩散后的p型半导体区表面进行选择性重掺杂处理,形成重掺杂区。

41.②ꢀ

经酸性刻蚀液去除n型晶硅背面的psg,再在碱性抛光液中对n型晶硅背面进行抛光,温度为70℃,时间为5min,清洗并烘干。

42.③ꢀ

n型硅片置于pecvd沉积腔室,先通入n2,对腔室进行清洗,抽真空后通入sih4和n2o,流量比设为1:3,设定温度为400℃,射频功率为50w,沉积8min得到厚度为1.2nm的sion薄膜。

43.④ꢀ

排除腔室内残余气体,通入n2对腔室进行清洗,抽真空后通入sih4、h2和b2h6,射频功率为50w,温度为400℃,沉积得到厚度为50nm的磷掺杂多晶硅层;之后通入流量比为10:1的sih4和n2o气体,在50w射频功率和400℃温度下沉积10min得到厚度为8nm的sio2薄膜作为掩蔽层。

44.⑤ꢀ

硅片置于碱性刻蚀剂中,去除正面绕镀的多晶硅层,然后用hf和hno3的混合溶液去除样片正面的氧化层及psg层,清水清洗后烘干;硅片正面用pecvd方式沉积正面钝化层,腔室升温至320℃后,通入n2o和tma气体,流量比为9:1,25w射频功率下沉积2min,然后升温至420℃在nh3和n2o气氛下保持3min;清洗腔室后通入sih4和nh3,流量比为1:5,在50w射频共下沉积4min后逐渐改变流量比为1:10,沉积8min,形成厚度约为120nm的al2o3/si3n4复合钝化膜。

45.⑥ꢀ

硅片背面用pecvd沉积背面钝化层,源气体为sih4和nh3,流量比1:4,沉积功率55w,沉积时间15min,得到厚度为100nm的si3n4薄膜。

46.⑦ꢀ

激光处理正面重掺杂区域的钝化层,分别印刷正面和背面的电极栅线,并于700℃烧结,形成良好的欧姆接触。

47.对比例2采用二氧化硅作为隧穿氧化层,用于n型topcon电池,包括以下步骤:

①ꢀ

n型晶硅清洗、制绒,形成金字塔陷光结构;n型晶硅正面进行硼扩散,在1050℃下扩散120min,用脉冲激光器对扩散后的p型表面进行处理,形成局域重掺杂区。

48.②ꢀ

经酸性刻蚀液去除n型晶硅背面的bsg,然后在碱性抛光液中对n型晶硅背面进行抛光,温度为70℃,时间为5min,清洗并烘干。

49.③ꢀ

n型硅片置于lpcvd沉积腔室,降低腔室气压至130pa,并升温至600℃,后通入o2,在680℃保持10min,使n型硅片背面形成厚度约为1.2nm的sio2薄膜。排除腔室内残余气体,用n2对腔室进行清洗后升温至625℃,后通入sih4和n2,沉积50min,使p型硅片背面形成厚度为50nm的多晶硅薄层。

50.④ꢀ

通过热扩散的方式,在n型硅片背面的多晶硅层中进行磷扩散,并退火,之后在腔室内通入o2,使多晶硅层表面形成掩蔽层;硅片置于碱性刻蚀剂中,去除正面绕镀的多晶硅层,然后用hf和hno3的混合溶液去除样片正面的bsg及背面的氧化层和psg,清水清洗后

烘干;在650℃下在n型硅片生长厚度约为3nm的氧化层。

51.⑤ꢀ

硅片正面用pecvd方式沉积正面钝化层,腔室升温至280℃后,通入n2o和tma气体,流量比为10:1,20w射频功率下沉积3min,然后升温至400℃在nh3和n2o气氛下保持2min;清洗腔室后通入sih4和nh3,流量比为1:4,在50w射频共下沉积4min后逐渐改变流量比为1:10,沉积8min,形成厚度约为120nm的al2o3/si3n4复合钝化膜。

52.⑥ꢀ

硅片背面用pecvd沉积背面钝化层,源气体为sih4和nh3,流量比为1:3,沉积功率为50w,沉积时间10min,得到厚度约为80nm的si3n4薄膜。

53.⑦ꢀ

激光处理正面重掺杂区域的钝化层,分别印刷正面和背面的电极栅线,并于700℃烧结,形成良好的欧姆接触。

54.与对比例2相比,实施例2采用含氮二氧化硅(sio

x

ny)代替topcon结构中的sio2作为隧穿氧化层,提高了隧穿氧化层对硼或磷杂质原子的阻挡能力,降低由于多晶硅层中杂质原子的扩散而引起的载流子的复合,充分发挥了隧穿氧化钝化结构的钝化作用,提高了topcon结构的钝化效果,可以使光伏电池背面复合电流从20~50 fa/cm2降低至5~10 fa/cm2,大大提升了电池的性能。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1