一种半导体功率器件的边缘终端和半导体功率器件的制作方法

1.本实用新型属于半导体器件领域,涉及一种半导体功率器件的边缘终端和半导体功率器件。

背景技术:

2.半导体功率器件最基本的要求是在关断状态下以最小的漏电流承受较大端电压的能力,其中半导体功率器件所能承受的最大端电压称为阻断电压。阻断电压通常由材料特性和器件设计共同决定。通过切割晶圆片做成芯片的功率器件,阻断电压由于器件边缘二维电场集中而下降,通常通过采用特殊的边缘终端得到缓减。浮空场限环终端包含一系列环绕在主结区的同心p+环(即为浮空场限环),它是在沿着表面的横向上将电势分布展宽,减少横向电场强度,避免在主结区发生雪崩击穿,是边缘终端的一种技术。然而,现有常规的浮空场限环终端中,由于浮空场限环具有相同的结深,使得电场在漂移区的分布均匀性较差,且电场的分布面积较小,结果是终端效率和阻断电压仍然偏低。另外,有研究人员提出了其他结构的边缘终端,该边缘终端中沿着远离主结区(功能区)方向,场限环的结深逐渐减少。然而,该结深逐渐减少的场限环的仿真结果显示,随着场限环结深的逐渐降低,阻断电压呈下降趋势,结果是终端效率和阻断电压比相同结深的浮空场限环更低。因此,如何提高终端效率和阻断电压,是现阶段本领域技术人员仍然需要解决的技术问题,这对于促进半导体功率器件的广泛应用具有非常重要的意义。

技术实现要素:

3.本实用新型要解决的技术问题是克服现有技术的不足,提供一种半导体功率器件的边缘终端,通过优化浮空场限环的结深和掺杂分布,使得电场在漂移区的分布均匀性更好,且电场分布面积更大,进而有利于提高终端效率和阻断电压,而且还提供了一种半导体功率器件。

4.为解决上述技术问题,本实用新型采用以下技术方案:

5.一种半导体功率器件的边缘终端,包括:

6.n个浮空场限环,浮空场限环环绕半导体功率器件的主结区;

7.第1个至第n个浮空场限环的结深与主结区的结深相同,第n+i个浮空场限环的结深大于第n个浮空场限环的结深,且从第n+1个浮空场限环开始,浮空场限环的结深逐渐增大, n、n、i为正整数,且2≤n<n+i≤n。

8.上述的半导体功率器件的边缘终端,进一步改进的,第1个浮空场限环环绕半导体功率器件的主结区,第n个浮空场限环环绕第n-1个浮空场限环,且第n+i个浮空场限环环绕第n+i-1个浮空场限环。

9.上述的半导体功率器件的边缘终端,进一步改进的,所述第n+i个浮空场限环的结深为第n个浮空场限环的结深+i

×

步长,单位为μm;所述步长为0.1μm~30μm。

10.上述的半导体功率器件的边缘终端,进一步改进的,所述第n个浮空场限环的结深

为0.8 μm~1.3μm。

11.上述的半导体功率器件的边缘终端,进一步改进的,所述第1个至第n个浮空场限环的掺杂分布与主结区相同;所述浮空场限环的峰值掺杂浓度为5e17cm-3

~5e20cm-3

。

12.本技术中,上述的半导体功率器件的边缘终端的制造方法,包括以下步骤:在半导体衬底的漂移区形成主结区和依次环绕主结区的浮空场限环。

13.上述的制造方法,进一步改进的,采用光刻和离子注入工艺,在半导体衬底的漂移区制备主结区和依次环绕主结区的浮空场限环。

14.上述的制造方法,进一步改进的,在利用光刻和离子注入工艺进行制备之前,还包括以下处理:采用光刻和刻蚀工艺,对浮空场限环所在的漂移区表面进行开槽处理。

15.上述的制造方法,进一步改进的,采用外延工艺,在半导体衬底上制备漂移区。

16.作为一个总的技术构思,本实用新型还提供了一种半导体功率器件,包括上述的半导体功率器件的边缘终端。

17.上述的半导体功率器件,进一步改进的,所述半导体功率器件还包括半导体衬底、漂移区、源极金属和漏极金属;所述半导体衬底包括硅、锗硅、砷化镓、碳化硅、氮化镓、三氧化二镓或金刚石。

18.与现有技术相比,本实用新型的优点在于:

19.本实用新型半导体功率器件的边缘终端,包括靠近主结区且与主结区结深相同的浮空场限环,以及远离主结区且结深比主结区深并逐渐增大的另一部分浮空场限环,通过优化浮空场限环的结深及掺杂分布,浮空场限环的曲率半径增大,提升了终端区的电场分布均匀性和面积,进而提升了终端效率和阻断电压。

附图说明

20.为使本实用新型实施例的目的、技术方案和优点更加清楚,下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整的描述。

21.图1为现有半导体功率器件的边缘终端的剖面结构示意图。

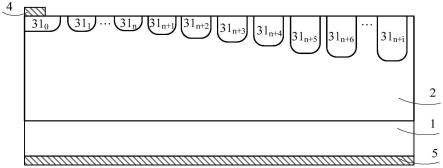

22.图2为本实用新型实施例1中半导体功率器件的边缘终端的剖面结构示意图。

23.图3(a)~3(e)为本实用新型实施例1中半导体功率器件的边缘终端的制备工艺流程图。

24.图4为现有半导体功率器件的边缘终端的电场分布仿真图。

25.图5为本实用新型实施例1中半导体功率器件的边缘终端的电场分布仿真图。

26.图6为本实用新型实施例2中半导体功率器件的边缘终端的电场分布仿真图。

27.图7为本实用新型实施例3中半导体功率器件的边缘终端的电场分布仿真图。

28.图8为本实用新型实施例4中半导体功率器件的边缘终端的电场分布仿真图。

29.图9为本实用新型实施例1-4中半导体功率器件的边缘终端现有边缘终端对应的阻断电压对比图。

30.图10为对比例1中半导体功率器件的边缘终端的电场分布仿真图。

31.图11为对比例2中半导体功率器件的边缘终端的电场分布仿真图。

32.图12为对比例1、对比例2中半导体功率器件的边缘终端的电场曲线分布图。

33.图13为对比例1、对比例2中半导体功率器件的边缘终端的电势曲线分布图。

34.图14为本实用新型实施例5中半导体功率器件的边缘终端的剖面结构示意图。

35.图例说明:

36.1、碳化硅n型衬底;2、n型漂移区;310、p型主结区;311、第1个浮空场限环;312、第2个浮空场限环;31n、第n个浮空场限环;31

n+i

、第n+i个浮空场限环;32

n+i

、第n+i个沟槽;4、源极金属;5、漏极金属。

具体实施方式

37.以下结合说明书附图和具体优选的实施例对本实用新型作进一步描述,但并不因此而限制本实用新型的保护范围。

38.如图1所示,现有半导体功率器件的边缘终端,主要包括主结区310和一系列环绕在主结区的同心p+环(即为浮空场限环311~31n,n为正整数且≥2),且这些浮空场限环311~31n的结深及掺杂分布与主结区310均相同,该边缘终端存在的缺陷是电场在漂移区的分布均匀性较差,且电场的分布面积较小,结果是终端效率和阻断电压仍然偏低。

39.针对现有半导体功率器件的边缘终端中存在的缺陷,本技术旨在提供一种漂移区电场分布均匀性好且电场分布面积大的边缘终端,以提升终端效率和阻断电压,具体来说:本技术中改进了浮空场限环,通过优化浮空场限环的结深及掺杂分布,来优化电场在漂移区的分布均匀性和分布面积,进而有利于提高终端效率和阻断电压。如图2所示,本技术中提出了一种改进的半导体功率器件的边缘终端,包括:n个浮空场限环,其中第1个浮空场限环311环绕半导体功率器件的主结区310,第n个浮空场限环31n环绕第n-1个浮空场限环31n-1

(如第6个浮空场限环316环绕第5个浮空场限环315),且第n+i个浮空场限环环绕第n+i-1个浮空场限环(如第13个浮空场限环31

6+7

环绕第12个浮空场限环31

6+6

),n、n、i为正整数(如n可以为17,n可以为1~6,i可以为1~11,n、n、i的取值根据实际情况择优选择,此处并不会对n、n、i的取值产生限定,任何能够用于提升电场分布均匀性和分布面积的取值都用于本技术),且2≤n<n+i≤n,与此同时,第1个至第n个浮空场限环的结深与主结区的结深相同,第n+i个浮空场限环的结深大于第n个浮空场限环的结深,且从第n+1个浮空场限环开始,浮空场限环的结深逐渐增大。本技术中,浮空场限环311~31n与主结310的结深及掺杂分布相同,从31

n+1

(漂移区的空间电荷区倾斜的位置附近,如图4所示)起,浮空场限环的结深逐渐加深,这使得相应的曲率半径增加,改变了终端区的电场分布,提升了终端效率和阻断电压。

40.作为进一步改进的技术方案,本技术中进一步优化了浮空场限环的结深,具体来说,第 n+i个浮空场限环的结深为第n个浮空场限环的结深+i

×

步长,单位为μm,其中步长为0.1 μm~30μm,具体来说,浮空场限环31

n+1

的结深xj

(31n+1)

=浮空场限环31n的结深xj

(31n)

+1

×

步长,浮空场限环31

n+2

的结深xj

(31n+2)

=浮空场限环31n的结深xj

(31n)

+2

×

步长

…

以此类推,浮空场限环31

n+i

的结深xj

(31n+i)

=浮空场限环31n的结深xj

(31n)

+i

×

步长。本技术中,从第n+1 个浮空场限环31

n+1

开始,浮空场限环的结深按相应的比例逐渐增加,由此获得的浮空场限环的排列方式,更有利于在漂移区形成均匀性更好且面积更大的电场,从而能够更加显著的提升阻断电压。

41.本技术中,第1个至第n个浮空场限环的结深为0.8μm~1.3μm;第1个至第n个浮空场限环的结深及掺杂分布与主结区相同;浮空场限环的峰值掺杂浓度为5e17cm-3

~5e20cm

‑3。

42.本技术中,还提供了一种半导体功率器件的边缘终端的制造方法,包括以下步骤:在半导体衬底的漂移区形成主结区和依次环绕主结区的浮空场限环。

43.本技术中,采用光刻和离子注入工艺,在半导体衬底的漂移区制备主结区和依次环绕主结区的浮空场限环;同时,采用外延工艺,在半导体衬底上制备漂移区。

44.本技术中,为了更好的实现对浮空场限环所在区域的掺杂处理,即在利用光刻和离子注入工艺进行制备(掺杂)之前,还包括以下处理:采用光刻和刻蚀工艺,对浮空场限环所在的漂移区表面进行开槽处理。例如,采用的离子注入设备的掺杂深度为3μm时,为了更好的制备结深为3.2μm的浮空场限环,需要先采用光刻和刻蚀工艺,对浮空场限环所在的漂移区表面进行开槽处理,其中开槽的深度为0.2μm,而且开槽的宽度与对应的浮空场限环相同。本技术中,仅以上述案例进行说明,并不会对本技术的工艺产生限定。如果采用的离子注入设备的掺杂深度,能够实现离子注入/掺杂的目的,则无需额外进行开槽处理。

45.本技术中,还提供了一种半导体功率器件,包括上述的边缘终端,而且还包括半导体衬底、漂移区、源极金属和漏极金属,其中半导体衬底包括硅、锗硅、砷化镓、碳化硅、氮化镓、三氧化二镓或金刚石。

46.以下结合具体实施例对本实用新型做进一步说明:

47.实施例1

48.如图2所示,一种半导体功率器件的边缘终端,包括:n个浮空场限环,其中第1个浮空场限环环绕半导体功率器件的主结区,第n个浮空场限环环绕第n-1个浮空场限环,且第 n+i个浮空场限环环绕第n+i-1个浮空场限环,其中n可以为17,n为6,i为11,具体来说:第1个浮空场限环311环绕半导体功率器件的主结区310,第2个浮空场限环312环绕第1个浮空场限环311,第3个浮空场限环313环绕第2个浮空场限环312,以此类推,第6个浮空场限环316环绕第5个浮空场限环315,且第7个浮空场限环31

6+1

环绕第6个浮空场限环316,第8个浮空场限环31

6+2

环绕第7个浮空场限环31

6+1

,以此类推,第17个浮空场限环31

6+11

环绕第16个浮空场限环31

6+10

。与此同时,第1个至第n个浮空场限环的结深与主结区的结深相同,第n+i个浮空场限环的结深大于第n个浮空场限环的结深,且从第n+1个浮空场限环开始,浮空场限环的结深逐渐增大(即沿着远离主结区的方向上,浮空场限环的结深逐渐增大),具体来说:第1个至第6个浮空场限环(浮空场限环311~浮空场限环316)的结深与主结区的结深310相同,均为1.2μm,第7个浮空场限环31

6+1

的结深大于第6个浮空场限环的结深,且第7个浮空场限环31

6+1

的结深为第6个浮空场限环316的结深xj

(316)+1

×

步长,其中第6个浮空场限环316的结深xj

(316)

为1.2μm,步长为0.1μm,即第7个浮空场限环31

6+1

的结深xj

(316+1)

=1.2μm+1

×

0.1μm=1.3μm,同理,第8个至第17个浮空场限环的结深 (xj

(316+2)

~xj

(316+11)

)依次为1.4μm、1.5μm、1.6μm、1.7μm、1.8μm、1.9μm、2.0μm、 2.1μm、2.2μm、2.3μm,即从第7个浮空场限环起,它们的结深逐渐增大。

49.本实施例中,浮空场限环311~316的掺杂分布与主结区310相同,浮空场限环、主结区的峰值掺杂浓度均为2e18cm-3

。本技术中,由于浮空场限环311~316与主结310的结深及掺杂分布相同,且从31

6+1

起,浮空场限环的结深逐渐加深,通过优化浮空场限环的结深及掺杂分布,使得电场在漂移区的分布均匀性更好,且电场分布面积更大,进而提升了终端效率和阻断电压。

50.为了更清晰的阐述本实用新型,本技术中提出了一种上述实施例中的半导体功率器件的边缘终端的制造方法,仅描述浮空场限环的制造方法,其制备工艺流程图如图3(a)~3(e)所示,包括以下步骤:

51.第1步:采用外延工艺,在碳化硅n型衬底1上形成n型漂移区2,其中n型衬底1的电阻率为0.025ω

·

cm,厚度为350μm,n型漂移区2的结深和掺杂浓度分别为11μm和 8e15cm-3

,如图3(a)所示。

52.第2步:采用光刻和离子注入工艺,在n型漂移区2形成p型主结区310和p型浮空场限环311~316,它们的结深均为1.2μm,峰值掺杂浓度为2e18cm-3

,如图3(b)所示。

53.第3步:采用光刻和离子注入工艺,在n型漂移区2形成p型浮空场限环31

6+1

,其结深为1.3μm,峰值掺杂浓度为2e18cm-3

,如图3(c)所示。

54.第4步:采用光刻和离子注入工艺,在n型漂移区2形成p型浮空场限环31

6+2

,其结深为1.4μm,峰值掺杂浓度为2e18cm-3

,如图3(d)所示。

55.依此类推,采用光刻和离子注入工艺,在n型漂移区2形成p型浮空场限环31

6+3

~31

6+11

,它们的结深依次为1.5μm、1.6μm、1.7μm、1.8μm、1.9μm、2.0μm、2.1μm、2.2μm、 2.3μm,且峰值掺杂浓度为2e18cm-3

,如图3(e)所示,得到半导体功率器件的边缘终端。

56.一种包括上述本实施例的边缘终端的半导体功率器件,包括半导体衬底、在半导体衬底正面形成的漂移区,以及漂移区上形成的边缘终端,还包括在主结区上形成的源极金属(阳极)和在半导体衬底背面形成的漏极金属(阴极),漂移区上还形成有截止环。

57.本实施例中,半导体衬底为碳化硅,n型漂移区的厚度为11μm,掺杂浓度为和8e15cm-3

。

58.本技术中,图中的尺寸(包括横向尺寸、版图尺寸、介质厚度、金属厚度、结深等)不代表实际尺寸,仅用于形成边缘终端(浮空场限环)结构的方法示例,不构成对本技术技术方案的限定,包括但不限于肖特基二极管、pin二极管、平面mosfet、平面igbt、沟槽 mosfet、沟槽igbt;同时,半导体衬底包含但不限于sic,例如si、锗硅、砷化镓、氮化镓、三氧化二镓或金刚石等,根据需要都可以用于本技术。

59.实施例2

60.一种半导体功率器件的边缘终端,与实施例1中的边缘终端基本相同,区别仅在于:实施例2中采用的步长为0.2μm,具体来说,区别是:第7个至第17个浮空场限环的结深 (xj

(316+1)

~xj

(316+11)

)依次为1.4μm、1.6μm、1.8μm、2.0m、2.2μm、2.4μm、2.6μm、 2.8μm、3.0μm、3.2μm、3.4μm。

61.实施例3

62.一种半导体功率器件的边缘终端,与实施例1中的边缘终端基本相同,区别仅在于:实施例2中采用的步长为0.3μm,具体来说,区别是:第7个至第17个浮空场限环的结深 (xj

(316+1)

~xj

(316+11)

)依次为1.5μm、1..8μm、2.1μm、2.4m、2.7μm、3.0μm、3.3μm、 3.6μm、3.9μm、4.2μm、4.5μm。

63.实施例4

64.一种半导体功率器件的边缘终端,与实施例1中的边缘终端基本相同,区别仅在于:实施例2中采用的步长为0.4μm,具体来说,区别是:第7个至第17个浮空场限环的结深(xj

(316+1)

~xj

(316+11)

)依次为1.6μm、2.0μm、2.4μm、2.8m、3.2μm、3.6μm、4.0μm、 4.4μm、4.8μ

m、5.2μm、5.6μm。

65.对比例1

66.一种半导体功率器件的边缘终端,主要包括主结区310和一系列环绕在主结区的同心p+ 环(即为浮空场限环311~31

17

),这些浮空场限环311~31

17

的结深及掺杂分布与主结区310均相同,结深1μm,峰值浓度为2e18cm-3

。

67.对比例2

68.一种半导体功率器件的边缘终端,主要包括主结区310和一系列环绕在主结区的同心p+ 环(即为浮空场限环311~31

17

),这些浮空场限环311~31

17

的结深逐渐减少,其中第一根场限环的结深为1μm,第二根场限环的结深为0.95μm,第三根场限环的结深为0.9μm,依次类推,以0.05μm的步长递减,第十七根场限环的结深为0.2μm。同时,这些浮空场限环311~ 31

17

的峰值浓度与主结区310均相同,为2e18cm-3

。对比例1与对比例2中,浮空场限环311~ 31

17

的环间距和环宽完全相同。

69.对实施例1-4中制备的半导体功率器件的边缘终端以及对比例1-2中的现有常规边缘终端进行电场分布和阻断电压仿真模拟,并测试它们的阻断电压,结果如图4-13所示。

70.现有浮空场限环310~31

17

的结深均为1.2μm的边缘终端的电场分布仿真结果,如图4所示;实施例1-4中制备的半导体功率器件的边缘终端的电场分布仿真结果,如图5-8所示。由图4-8可知,现有常规边缘终端中,从第7个浮空场限环31

6+1

附近开始,漂移区2的空间电荷区倾斜。实施例1-4中制备的半导体功率器件的边缘终端中,浮空场限环的漂移区2、 310~316的结构参数及环间距与图4相同,然而,在改变第7个浮空场限环31

6+1

及之后的浮空场限环的结深后,随着浮空场限环的步长增加,空间电荷区逐渐填满场限环下方的漂移区,电场分布充分利用了漂移区面积。同时,由图9可知,随着步长的增加,实施例1-4中制备的半导体功率器件的边缘终端中,第7个浮空场限环开始,浮空场限环的结深逐渐增大,由此带来的好处是阻断电压显著增加。因此,本技术中,通过优化浮空场限环的结深及掺杂分布,能够显著改善电场在漂移区的分布均匀性以及增加电场的分布面积,进而有利于提高终端效率和阻断电压。

71.对比例1中浮空场限环310~31

17

的结深均为1.0μm的边缘终端、对比例2中浮空场限环 310~31

17

的结深由1.0μm逐渐减少为0.2μm的边缘终端的电场分布仿真结果,如图10-13 所示。由图10-13可知,对比例1的边缘终端中,结深均匀的浮空场限环的阻断电压为1546v,而对比例2的边缘终端中,结深逐渐减少的浮空场限环的阻断电压为1125v,可见,随着场限环结深的逐渐降低,阻断电压呈下降趋势,其中第一根浮空场限环至第十七根浮空场限环的阻断电压由1546v降低至1125v,显然,浮空场限环的结深逐渐减少边缘终端的终端效率和阻断电压更低。

72.实施例5

73.进一步需要说明的是,若离子注入工艺中采用的设备仅能实现结深为1.5μm的离子注入 (掺杂)时,上述本实施例中空场限环的制造方法,可以为:

74.第1步:采用外延工艺,在碳化硅n型衬底1上形成n型漂移区2,其中n型衬底1的电阻率为0.025ω

·

cm,厚度为350μm,n型漂移区2的结深和掺杂浓度分别为11μm和 8e15cm-3

。

75.第2步:采用光刻和离子注入工艺,在n型漂移区2形成p型主结区310和p型浮空场限环311~316,它们的结深均为1.2μm,峰值掺杂浓度为2e18cm-3

。

76.第3步:采用光刻和离子注入工艺,在n型漂移区2形成p型浮空场限环31

6+1

,其结深为1.3μm,峰值掺杂浓度为2e18cm-3

。

77.第4步:采用光刻和离子注入工艺,在n型漂移区2形成p型浮空场限环31

6+2

,其结深为1.4μm,峰值掺杂浓度为2e18cm-3

。

78.第5步:采用光刻和离子注入工艺,在n型漂移区2形成p型浮空场限环31

6+3

,其结深为1.5μm,峰值掺杂浓度为2e18cm-3

。

79.第6步:采用光刻和刻蚀工艺,在n型漂移区2表面进行开槽处理,深度为0.1μm,形成沟槽32

6+4

,进而采用光刻和离子注入工艺,在n型漂移区2表面沟槽32

6+4

所在位置形成 p型浮空场限环31

6+4

,其结深为1.6μm,峰值掺杂浓度为2e18cm-3

。

80.第7步:采用光刻和刻蚀工艺,在n型漂移区2表面进行开槽处理,深度为0.2μm,形成沟槽32

6+5

,进而采用光刻和离子注入工艺,在n型漂移区2表面沟槽32

6+5

所在位置形成 p型浮空场限环31

6+5

,结深为1.7μm,峰值掺杂浓度为2e18cm-3

。

81.依此类推,采用光刻和刻蚀工艺,在n型漂移区2进行开槽处理,深度依次为0.3μm、 0.4μm、0.5μm、0.6μm、0.7μm、0.8μm,形成沟槽32

6+6

~32

6+11

,进而采用光刻和离子注入工艺,在n型漂移区2表面沟槽32

6+6

~32

6+11

所在位置分别形成p型浮空场限环31

6+3

~31

6+11

,它们的结深依次为1.8μm、1.9μm、2.0μm、2.1μm、2.2μm、2.3μm,且峰值掺杂浓度均为2e18cm-3

,所得半导体功率器件的边缘终端,如图14所示。本技术中,可根据需要选择是否需要对漂移区表面进行开槽处理,这使得本技术制备浮空场限环的制造工艺具有更好的适应性,能够根际实际需要制备满足要求的浮空场限环。

82.综上可知,本实用新型半导体功率器件的边缘终端,通过优化浮空场限环的结深及掺杂分布,浮空场限环的曲率半径增大,提升了终端区的电场分布均匀性和面积,进而提升了终端效率和阻断电压。

83.以上实施例仅是本实用新型的优选实施方式,本实用新型的保护范围并不仅局限于上述实施例。凡属于本实用新型思路下的技术方案均属于本实用新型的保护范围。应该指出,对于本技术领域的普通技术人员来说,在不脱离本实用新型原理的前提下的改进和润饰,这些改进和润饰也应视为本实用新型的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1