一种周期变化范围限制及过采样结合的同步信号抗干扰方法与流程

[0001]

本发明属于电力变换领域,具体为一种周期变化范围限制及过采样结合的同步信号抗干扰方法。

背景技术:

[0002]

如图1所示,三相全控整流桥的输入电压和输出电压的关系可以表示为

[0003]

u

out

=1.35u

in

cosα

[0004]

其中α是整流桥控制角,uin是输入的阳极电压有效值。

[0005]

三相整流桥控制需要同步信号确定每个周期的起始时刻,保证触发脉冲的上升沿时刻与控制角α匹配。

[0006]

输入的阳极电压同步变压器降幅隔离后,一般通过同步整形电路整形为方波信号作为控制器cpu接入的同步信号。以同步信号突变点(上升沿)对应全控整流桥输入电压的上升沿过零点,以此时刻作为本周期起点,得到阳极电压、同步信号与触发脉冲的相位关系如图2所示。

[0007]

同步信号2个相邻上升沿的时间差就是正弦波周期t,触发脉冲与本周期同步信号上升沿的时间差为dt,控制器通过设置触发脉冲的延时dt来保证触发脉冲与控制角α匹配。dt与整流桥控制角可以表示为

[0008]

dt=t

×

α/360

[0009]

同步信号一般是占空比约50%的方波信号,如图3a所示。而串入的尖峰干扰随机出现,可能出现在高电平部分,如图3b的第一尖峰干扰,也可能出现在低电平部分,如图3b中的第二尖峰干扰。

[0010]

同步信号一般接入全控整流桥控制器cpu的定时器,使用同步信号的上升沿触发中断,在同步中断设置对应触发角α的dt延时中断,随后依次输出本周期内的触发脉冲。如果使用干扰尖峰产生的上升沿启动dt延时中断,那么输出触发脉冲的时刻相对于阳极电压过零点的延时将无法匹配控制器设置的触发角α,将导致输出失控。

[0011]

当前同步信号一般由隔离整形电路的硬件消除干扰和毛刺,在同步中断响应的程序中没有做干扰信号容错屏蔽。但在实际工程应用中同步信号的干扰也曾因为某些特殊原因无法硬件滤除,例如强电电路的干扰直接耦合到弱电信号电路,在同步方波中产生随机出现的尖峰干扰,这就需要在软件中增强抗干扰措施。

技术实现要素:

[0012]

本发明的目的在于解决上述问题,提供一种周期变化范围限制及过采样结合的同步信号抗干扰方法,通过周期变化范围限制屏蔽同步方波高电平阶段出现的尖峰干扰,在同步方波低电平阶段出现的上升沿则对同步信号电平多次采样以屏蔽尖峰干扰。

[0013]

本发明的技术方案:

[0014]

一种周期变化范围限制及过采样结合的同步信号抗干扰方法,包括以下具体步

骤:

[0015]

s1.首先将隔离整形后的同步信号接入整流桥控制器cpu的定时器,设置同步信号上升沿触发定时器中断;

[0016]

s2.在同步中断中记录中断时刻,并计算当前时刻与上一次同步中断的时间差,如果时间差小于同步信号周期的90%则认为当前中断源于外部干扰,不记录中断时刻,不计算周期,也不启动过采样中断对同步信号进一步验证;

[0017]

s3.如果时间差大于同步信号周期的90%,则记录中断时刻和时间差,启动定时采样,读取连续3次同步信号对应的引脚电平,对同步信号进行第二阶段的验证;

[0018]

s4.如果连续3次得到的同步信号对应的引脚电平全部是高电平则确认同步信号上升沿有效,以此同步信号上升沿时刻作为全控整流桥控制角α对应的延时起点。

[0019]

所述步骤s2中,中断时刻与上一次同步中断的时间差中出现任何中断信号都认为是干扰,完全屏蔽了同步信号高电平阶段的尖峰干扰实现同步范围限制过滤。

[0020]

所述步骤s3中定时采样的采样周期为40μs,过采样时间为120μs。

[0021]

与现有技术相比,本发明的有益效果是:通过周期变化范围限制屏蔽同步方波高电平阶段出现的尖峰干扰,在同步方波低电平阶段出现的上升沿则对同步信号电平多次采样以屏蔽尖峰干扰,增强全控整流桥控制器对于同步信号的抗干扰能力。

附图说明

[0022]

图1是本发明的全控整流桥结构示意图。

[0023]

图2是理论上输入电压、同步信号与触发脉冲的相位关系。

[0024]

图3a是正常同步信号图。

[0025]

图3b是被干扰同步信号图。

[0026]

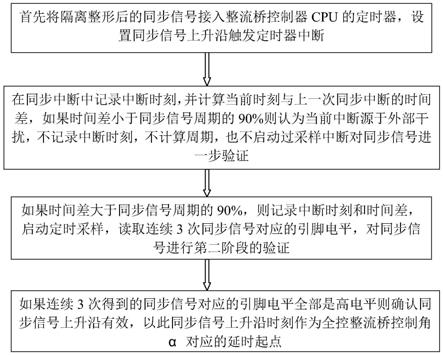

图4是本发明同步中断流程图。

[0027]

图5是本发明周期范围限制产生的不应区域图。

[0028]

图6是本发明过采样结果异常屏蔽尖峰干扰图。

[0029]

图7是本发明过采样具体实现流程图。

[0030]

图8是本发明的方法流程图。

具体实施方式

[0031]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0032]

如图8所示,一种周期变化范围限制及过采样结合的同步信号抗干扰方法,包括以下具体步骤:

[0033]

s1.将隔离整形后的同步信号接入整流桥控制器cpu的定时器,设置同步信号上升沿触发定时器中断;

[0034]

s2.在同步中断中记录中断时刻,并计算当前时刻与上一次同步中断的时间差,如果时间差小于同步信号周期的90%则认为当前中断源于外部干扰,不记录中断时刻,不计

算周期,也不启动过采样中断对同步信号进一步验证;

[0035]

s3.如果时间差大于同步信号周期的90%,则记录中断时刻和时间差,启动定时采样,读取连续3次同步信号对应的引脚电平,对同步信号进行第二阶段的验证;

[0036]

s4.如果连续3次得到的同步信号对应的引脚电平全部是高电平则确认同步信号上升沿有效,以此同步信号上升沿时刻作为全控整流桥控制角α对应的延时起点。

[0037]

如图4所示,在同步中断中记录中断时刻,并计算当前时刻与上一次同步中断的时间差,如果时间差小于周期的90%则认为当前中断源于外部干扰,不记录中断时刻,不计算周期,也不启动过采样中断对同步信号进一步验证。如图5所示,相当于在接收到一次有效同步中断后开启了一段不应期,在此不应期中出现任何中断信号都认为是干扰。

[0038]

如果时间差满足要求,则记录中断时刻(用于下一次同步中断时间差计算)和时间差,启动40μs定时中断对同步信号进行第二阶段的验证。

[0039]

因为同步方波占空比约50%,本次同步中断与上一次同步中断的时间差大于周期的90%,如图5所示,完全屏蔽了同步信号高电平阶段的尖峰干扰,所以经过同步范围限制过滤之后,如果同步中断源于干扰,肯定发生在同步信号低电平阶段,如图6所示的尖峰干扰。如果尖峰干扰宽度低于120μs,那么3次过采样中断肯定会捕捉到同步输入的低电平信号,并据此屏蔽周期刷新、控制角延时中断设置等同步中断响应。

[0040]

尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1