一种无时钟待机的低功耗感测芯片的制作方法

1.本发明涉及芯片领域,尤其是一种无时钟待机的低功耗感测芯片。

背景技术:

2.诸如红外接近及环境光亮度感测芯片之类的感测芯片已经逐渐普及地设置在移动电话、电视或便携式设备中,而随着芯片功能的不断扩充,高性能芯片的功耗较大,会导致整个设备出现续航能力弱、发热严重的问题,因此如何降低感测芯片的整体功耗、延长系统使用时间是感测芯片设计过程中的一项重点。

技术实现要素:

3.本发明人针对上述问题及技术需求,提出了一种无时钟待机的低功耗感测芯片,本发明的技术方案如下:

4.一种无时钟待机的低功耗感测芯片,该低功耗感测芯片包括:电源管理电路、通信寄存电路、感测模拟电路、数字控制电路、时钟电路和熔丝电路,通信寄存电路连接通信引脚,通信寄存电路连接电源管理电路、数字控制电路和熔丝电路,数字控制电路连接感测模拟电路,时钟电路用于提供片上时钟;

5.电源管理电路和通信寄存电路由常开电源域的常开电源常供电,感测模拟电路、数字控制电路、时钟电路和熔丝电路由可控电源域的电源供电,可控电源域的电源的通断受控于电源管理电路;

6.当低功耗感测芯片处于待机模式下时,电源管理电路控制可控电源域的电源断开,低功耗感测芯片在无片上时钟的基础上与通过通信寄存电路利用通信引脚进行外部通信和/或进行寄存器配置。

7.其进一步的技术方案为,可控电源域包括熔丝电源域和主电源域,熔丝电路由熔丝电源域的熔丝电源供电,感测模拟电路、数字控制电路和时钟电路由主电源域的主电源供电,电源管理电路分别控制熔丝电源和主电源的通断,当低功耗感测芯片处于待机模式下时,电源管理电路控制熔丝电源和主电源都断开。

8.其进一步的技术方案为,当低功耗感测芯片处于熔丝模式下时,电源管理电路控制熔丝电源和主电源都导通,时钟电路给熔丝电路提供片上时钟,熔丝电路烧录或读取熔丝数据;

9.当低功耗感测芯片处于感测模式下时,电源管理电路控制熔丝电源断开、主电源导通,低功耗感测芯片执行感测操作。

10.其进一步的技术方案为,低功耗感测芯片上电后进入熔丝模式读取熔丝数据,熔丝数据读取完毕后根据通过通信寄存电路接收到的外部切换指令在待机模式和感测模式之间切换。

11.其进一步的技术方案为,熔丝电源的电压与常开电源相等,熔丝电路包括熔丝控制器和熔丝器件,熔丝控制器分别连接通信寄存电路和熔丝器件。

12.其进一步的技术方案为,主电源域的主电源包括通断状态相同的第一电源和第二电源,第一电源的电压与常开电源相等,第二电源的电压低于常开电源,则低功耗感测芯片还包括工作于主电源域的线性稳压器,线性稳压器用于将第一电源转换为第二电源;

13.感测模拟电路包括相连接的高压模拟电路和低压模拟电路,高压模拟电路由主电源域的第一电源供电,低压模拟电路、数字控制电路和时钟电路由主电源域的第二电源供电。

14.其进一步的技术方案为,低功耗感测芯片还包括由主电源域的第二电源供电的中断控制电路,中断控制电路连接通信寄存电路和数字控制电路,中断控制电路还连接中断引脚。

15.其进一步的技术方案为,通信寄存电路基于高阈值晶体管构建。

16.其进一步的技术方案为,通信寄存电路包括相连接的i2c接口和寄存器,i2c接口连接通信引脚,通信引脚包括i2c总线的scl引脚和sda引脚,当低功耗感测芯片处于待机模式下时,电源管理电路和通信寄存电路依靠i2c总线的scl时钟工作。

17.本发明的有益技术效果是:

18.本技术公开了一种无时钟待机的低功耗感测芯片,该低功耗感测芯片内部做了电源域划分,将电源管理电路和通信寄存电路放在常开电源域,包括时钟电路在内的其他电路放在受电源管理电路控制的可控电源域,从而使得该低功耗感测芯片可以在待机模式下无需请求任何片上时钟就能实现外部通信和寄存器配置,有效降低功耗。

19.同时区别于传统芯片将所有数字逻辑都放在低电压域的做法,将包括电源管理电路和通信寄存电路的一部分数字逻辑放在高电压域,所以这部分数字逻辑不需要使用到稳压器,也就不会产生稳压器的漏电功耗。由于该部分逻辑的翻转率很低,所以动态功耗只占总功耗的很小一部分,动态功耗的提升小于节省的稳压器漏电功耗,所以最终总功耗得到减少。

20.进一步的,采用hvt晶体管来实现高电压域的数字逻辑,可以在不影响芯片运行的基础上减少漏电功耗,最终使得高电压域的数字逻辑的功耗得以进一步减小。

21.可控电源域可以进一步划分为熔丝电源域和主电源域,熔丝电源域在熔丝电路访问结束后可以完全断电以达到0功耗的效果。主电源域上电进入感测模式时,熔丝电路保持断电,而且可以及时从感测模式切换回待机模式,相比于传统芯片可以有效降低功耗。

附图说明

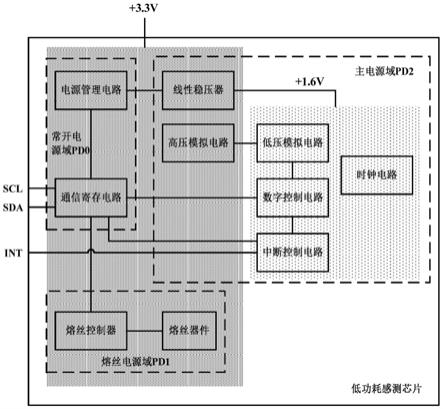

22.图1是本技术的低功耗感测芯片的内部结构示意图。

具体实施方式

23.下面结合附图对本发明的具体实施方式做进一步说明。

24.本技术公开了一种无时钟待机的低功耗感测芯片,请参考图1,该低功耗感测芯片包括:电源管理电路、通信寄存电路、感测模拟电路、数字控制电路、时钟电路和熔丝电路。通信寄存电路连接通信引脚,通信寄存电路连接电源管理电路、数字控制电路和熔丝电路,数字控制电路连接感测模拟电路。低功耗感测芯片还包括中断控制电路,中断控制电路连接通信寄存电路和数字控制电路,中断控制电路还连接中断引脚int。其中:

25.(1)通信寄存电路包括相连接的i2c接口和寄存器,i2c接口连接通信引脚,通信引脚包括i2c总线的scl引脚和sda引脚。i2c接口用于对外通信,寄存器用于存放配置及状态信息。

26.(2)感测模拟电路主要包括光电二极管、模数转换器和led驱动器,使得该感测芯片实现为红外接近及环境光亮度感测芯片。感测模拟电路包括相连接的高压模拟电路和低压模拟电路,其中,高压模拟电路主要包括led驱动器,实际可能还包括io引脚和带隙基准电源等,低压模拟电路主要包括光电二极管和模数转换器。

27.(3)数字控制电路包括状态机及相应的控制逻辑,用于管理感测模拟电路以及控制数据回传等。

28.(4)时钟电路用于提供片上时钟,时钟电路主要包括振荡器和时钟控制器,振荡器用于生成片上时钟,时钟控制器负责片上时钟的分支、开启/关停、分频以及复位信号的产生。

29.(5)熔丝电路包括熔丝控制器和熔丝器件,熔丝控制器分别连接通信寄存电路和熔丝器件。熔丝器件只可写入一次,用以存储矫正数据,熔丝控制器生成熔丝的接口读写信号时序。

30.(6)中断控制电路用于适时生成中断信号并通过中断引脚int通知外部的微控制器做相应处理。

31.电源管理电路和通信寄存电路由常开电源域pd0的常开电源常供电,感测模拟电路、数字控制电路、时钟电路和熔丝电路由可控电源域的电源供电,可控电源域的电源的通断受控于电源管理电路。

32.当低功耗感测芯片完全断电时,常开电源域pd0的常开电源和可控电源域的电源都断电,常开电源域pd0为高压电域,比较典型的为3.3v电源域。当低功耗感测芯片正常供电时,常开电源域pd0的常开电源始终开启,电源管理电路控制可控电源域的电源断开使得低功耗感测芯片处于待机模式下,此时除了通信寄存电路和电源管理电路之外,其他电路结构都断电,所有逻辑静止无翻转,时钟静止,降低功耗。但是低功耗感测芯片在无片上时钟的基础上与通过通信寄存电路利用通信引脚进行外部通信和/或进行寄存器配置。也即低功耗感测芯片在待机模式下可以正常接收外部指令以及寄存器配置过程,而无需请求任何片上时钟,电源管理电路和通信寄存电路依靠i2c总线的scl时钟工作。

33.进一步的,通信寄存电路基于高阈值(hvt)晶体管构建,由于通信寄存电路都是运行在非常低的频率(<10mhz),所以hvt晶体管相对较慢的速度并不能对本芯片产生影响,而采用hvt晶体管可以减少漏电功耗。另外由于通信寄存电路和电源管理电路无需使用稳压器,因此不会产生稳压器的漏电功耗,由于通信寄存电路和电源管理电路的翻转率很低,所以动态功耗只占总功耗的很小一部分,动态功耗的提升小于节省的稳压器漏电功耗,所以最终总功耗得到减少。由此该低功耗感测芯片在待机模式下,若无外部访问时,则基本可以实现0动态功耗,以及最小的漏电功耗,和传统的运行模式相比功耗得到极大的减小,经实测可以减少90%以上。

34.进一步的,可控电源域包括熔丝电源域pd1和主电源域pd2,熔丝电路由熔丝电源域pd1的熔丝电源供电,感测模拟电路、数字控制电路、时钟电路和中断控制电路由主电源域pd2的主电源供电。其中,熔丝电源的电压与常开电源相等也为高压电域,也即上述3.3v

电源域。主电源域的主电源包括通断状态相同的第一电源和第二电源,第一电源的电压与常开电源相等也为高压电域,第二电源的电压低于常开电源为低压电域,则该低功耗感测芯片还包括工作于主电源域的线性稳压器,线性稳压器用于将第一电源转换为第二电源,比如较为典型的,常开电源、熔丝电源和第一电源均为3.3v,而第二电源为1.6v。高压模拟电路由主电源域的第一电源供电,低压模拟电路、数字控制电路、时钟电路和中断控制电路由主电源域的第二电源供电。

35.电源管理电路分别控制熔丝电源和主电源的通断,从而可以对熔丝电路与其他电路的工作状态也单独控制。当低功耗感测芯片处于待机模式下时,电源管理电路控制熔丝电源和主电源都断开,使得可控电源域断开。由于熔丝电源域pd1和主电源域pd2可以独立受控工作,因此进一步的,该低功耗感测芯片还包括熔丝模式和感测模式:

36.当低功耗感测芯片处于熔丝模式下时,电源管理电路控制熔丝电源和主电源都导通,此时工作于主电源的时钟电路给熔丝电路提供片上时钟,熔丝电路烧录或读取熔丝数据。烧录熔丝数据一般在生产过程中,只可写入一次,用于存储熔丝数据、写入的是矫正数据。读取熔丝数据一般在芯片上电时、读取到的是校准数据。对熔丝电路的访问结束后,熔丝电源可以完全断电以达到0功耗的效果。

37.当低功耗感测芯片处于感测模式下时,电源管理电路控制熔丝电源断开、主电源导通,工作于主电源域pd2的各部分电路正常工作,低功耗感测芯片执行感测操作,也即进入正常工作状态。

38.由此,该低功耗感测芯片共包括四种工作模式:关闭模式、熔丝模式、待机模式和感测模式:在关闭模式下,外部供电断开,常开电源域pd0、熔丝电源域pd1和主电源域pd2都关闭。在熔丝模式下,外部供电开启,常开电源域pd0、熔丝电源域pd1和主电源域pd2都开启。在待机模式下,外部供电开启,常开电源域pd0开启,熔丝电源域pd1和主电源域pd2都关闭。在感测模式下,外部供电开启,常开电源域pd0和主电源域pd2开启,熔丝电源域pd1保持关闭。请参考如下表格。

[0039][0040][0041]

该低功耗感测芯片实际工作时,当低功耗感测芯片完全断电时处于关闭模式,正常上电后,一般首先进入熔丝模式读取熔丝数据。熔丝数据读取完毕后根据通过通信寄存电路接收到的外部切换指令在待机模式和感测模式之间切换。一般情况下,熔丝数据读取完毕后首先进入待机模式。当通过通信寄存电路接收到的外部切换指令指示开始感测时进入感测模式。当通过通信寄存电路接收到的外部切换指令指示结束感测时重新及时进入待机模式以降低功耗,以此循环。直到该低功耗感测芯片下电时回到关闭模式。

[0042]

以上所述的仅是本技术的优选实施方式,本发明不限于以上实施例。可以理解,本领域技术人员在不脱离本发明的精神和构思的前提下直接导出或联想到的其他改进和变

化,均应认为包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1