一种基于健全相的电源快切装置快速合闸方法与流程

1.本发明涉及一种基于健全相的电源快切装置快速合闸方法,属于电力系统继电保护技术领域。

背景技术:

2.电源快切装置适用于发电厂厂用电切换,或其它工业用户,如化工、冶金、煤炭等有较多高低压电动机负荷场合的电源切换。备用开关合闸时,必须考虑母线反馈电压与备用电源电压间的频差相差引起的电流冲击问题,以避免造成设备跳闸、设备损坏或寿命缩短等后果。

3.dl/t 1073《电厂厂用电源快速切换装置通用技术条件》规定,电源快切装置应具有快速合闸功能,其基本判据,如图1所示。

4.快速合闸是速度最快、效果最优的合闸方式。然而工程中也发现,快速合闸容易出现误动和拒动的现象。造成这个现象的主要原因是,传统的快速合闸方法一般固定采用某相电压的频差相差数据进行逻辑判断。若此相就是短路故障相,那么波形畸变将使得频差相差测量误差很大,结果造成快速合闸误动或拒动。

技术实现要素:

5.发明目的:为了克服现有技术中存在的不足,本发明提供一种基于健全相的电源快切装置快速合闸方法,该方法原理符合dl/t 1073标准对快速合闸的要求,且可以有效地降低快速合闸误动和拒动的概率。

6.技术方案:为实现上述目的,本发明采用的技术方案为:

7.一种基于健全相的电源快切装置快速合闸方法,包括以下步骤:

8.步骤1,对母线三相电压测频测相:分别存储t0、t1、t2三个时刻所对应的频差、相差。其中,t0为工作开关跳开时刻,t1为工作开关跳开时刻向前推的时刻一,t2为工作开关跳开时刻向前推的时刻二。

9.步骤2,健全相的选择:从母线ua、ub、uc三相电压中选择幅值最大的相作为健全相,其中,健全相记为x,a、b、c表示母线三相的相别。

10.步骤3,基于健全相的“3取2”快速合闸决策:取健全相x通道在t0、t1、t2三个时刻所对应的频差、相差,分别记为x相电压在t0时刻频差df_x_t0、x相电压在t0时刻相差dq_x_t0、x相电压在t1时刻频差df_x_t1、x相电压在t1时刻相差dq_x_t1、x相电压在t2时刻频差df_x_t2、x相电压在t2时刻相差dq_x_t2,其中,df表示频差,dq表示相差,x=a相或b相或c相。

[0011][0012]

其中,df_set为快速合闸频差定值,dq_set为快速合闸相差定值,&表示逻辑“与”。

[0013]

将健全相x通道在t0、t1、t2三个时刻所对应的频差、相差代入式子(1)、式子(2)、式子(3),若式子(1)、式子(2)、式子(3)至少有两个式子成立,则表示健全相x满足合闸条件,执行合闸。

[0014]

优选的:工作开关跳开时刻为0时刻。

[0015]

优选的:工作开关跳开时刻向前推的时刻一为10ms。

[0016]

优选的:工作开关跳开时刻向前推的时刻二为15ms。

[0017]

本发明相比现有技术,具有以下有益效果:

[0018]

(1)、选择未受短路故障影响的相或者受影响最小的相作为健全相,能从源头减少频差和相差的测量误差。

[0019]

(2)、健全相算法简单高效,对快速合闸整体时间特性影响不大。算法本身以大小比较为主要计算类型,其计算量非常小。

[0020]

(3)、基于“3取2”原则的快速合闸决策采用健全相3个时刻频差相差进行快速合闸判别,可以有效地避免因为一个点计算误差而造成误动和拒动。

附图说明

[0021]

图1为现有基本判据。图中,df为当前时刻母线和备用电源之间的频差,dq为当前时刻母线和备用电源之间的相差;df_set为快速合闸频差定值;dq_set为快速合闸相差定值。

[0022]

图2为三相电压频差相差存储示意图,其中,虚线部分代表频差相差存储的时刻点,以工作开关跳开为0ms时刻。具体的测频和测相算法可以自由选择,无特殊的约束。

[0023]

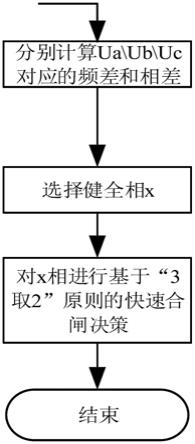

图3为健全相的选择。

[0024]

图4为基于健全相的“3取2”快速合闸决策,其中,x为健全相对应的相别,x=a相或b相或c相。df_x_0\dq_x_0表示0ms时刻所对应的频差相差;df_x_10\dq_x_10表示10ms时刻所对应的频差相差;df_x_15\dq_x_15表示15ms时刻所对应的频差相差。df_set为快速合闸频差定值;dq_set为快速合闸相差定值。“&”表示逻辑“与”。“≥2”表示“3个条件中有2个为真”。

[0025]

图5为本发明的总体流程图。

具体实施方式

[0026]

下面结合附图和具体实施例,进一步阐明本发明,应理解这些实例仅用于说明本发明而不用于限制本发明的范围,在阅读了本发明之后,本领域技术人员对本发明的各种等价形式的修改均落于本技术所附权利要求所限定的范围。

[0027]

一种基于健全相的电源快切装置快速合闸方法,如图2-5所示,包括以下步骤:

[0028]

步骤1,对母线三相电压测频测相:分别存储t0、t1、t2三个时刻所对应的频差、相差。其中,t0为工作开关跳开时刻,t1为工作开关跳开时刻向前推的时刻一,t2为工作开关跳开时刻向前推的时刻二。

[0029]

步骤2,健全相的选择:从母线ua、ub、uc三相电压中选择幅值最大的相作为健全相,其中,健全相记为x,a、b、c表示母线三相的相别。

[0030]

步骤3,基于健全相的“3取2”快速合闸决策:取健全相x通道在t0、t1、t2三个时刻所对应的频差、相差,分别记为x相电压在t0时刻频差df_x_t0、x相电压在t0时刻相差dq_x_t0、x相电压在t1时刻频差df_x_t1、x相电压在t1时刻相差dq_x_t1、x相电压在t2时刻频差df_x_t2、x相电压在t2时刻相差dq_x_t2,其中,df表示频差,dq表示相差,x=a相或b相或c相。

[0031][0032]

其中,df_set为快速合闸频差定值,dq_set为快速合闸相差定值,&表示逻辑“与”。

[0033]

将健全相x通道在t0、t1、t2三个时刻所对应的频差、相差代入式子(1)、式子(2)、式子(3),若式子(1)、式子(2)、式子(3)至少有两个式子成立,则表示健全相x满足合闸条件,执行合闸。

[0034]

如图2所示,对母线三相电压测频测相,其主要内容是连续地存储母线三相电压的0ms、10ms、15ms三个时刻所对应的频差、相差值(以工作开关跳开时刻为0ms时刻并向前推10ms和15ms)。三相电压计算出的频差相差名称见下表1。其中“df、dq”表示频差和相差;“0、10、15”表示时刻点;“a、b、c”表示相别。例如“df_a_10”表示a相电压在10ms时刻的频差。

[0035]

表1三相电压计算出的频差相差名称

[0036] 0ms时刻频差相差10ms时刻频差相差15ms时刻频差相差a相数据df_a_0\dq_a_0df_a_10\dq_a_10df_a_15\dq_a_15b相数据df_b_0\dq_b_0df_b_10\dq_b_10df_b_15\dq_b_15c相数据df_c_0\dq_c_0df_c_10\dq_c_10df_c_15\dq_c_15

[0037]

健全相的选择,其主要内容是从母线ua、ub、uc三相电压中选择幅值最大的那相作为健全相,假定健全相为x,其中x=a相或b相或c相,健全相的选择逻辑见图3。

[0038]

基于健全相的“3取2”快速合闸决策,按照如下逻辑判断:

[0039]

取健全相x对应的频差相差,分别记为df_x_0、dq_x_0、df_x_10、dq_x_10、df_x_15、dq_x_15,其中x=a相或b相或c相。

[0040]

对于3个时刻点分别进行基本的快速合闸逻辑判断,若3个结果中有两个满足条件即判断最终的快速合闸逻辑满足。具体判断逻辑见图4,即取健全相通道上的0ms、10ms、15ms频差相差数据,分别进行基本的快速合闸逻辑判断,若3个结果中有两个满足条件即判断最终的快速合闸逻辑满足。

[0041]

本发明以健全相的电压为基础,取其通道上3个不同时刻的频差相差为数据集,并

在数据集上对3个时刻的数据进行基本的快速合闸逻辑判断,最后对3个结果采取“3取2”的决策机制来决定最终的快速合闸逻辑是否满足,用于电源快切装置,主要解决快切装置的快速合闸方法成功率低,且容易误判的问题。本发明能最大程度地避免短路时电压波形畸变对快切装置快速合闸成功率的影响,提高了电源切换的成功率。

[0042]

以上所述仅是本发明的优选实施方式,应当指出:对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1