具有过电压保护的发射器的制作方法

1.本技术涉及发射器,具体涉及一种具有过电压保护的发射器,其可由具有相对较低耐压的晶体管来实现。

背景技术:

2.由于制程进步,晶体管的尺寸越来越小,使得晶体管的耐压也越来越低。然而,在现有的应用中,发射器仍需要传输具有较高位准的信号。若直接使用具有低耐压的晶体管来实现现有的发射器,该些晶体管需承受过大的电压而出现损坏,造成发射器的可靠度降低。

技术实现要素:

3.在一些实施例中,本技术提供一种具有过电压保护的发射器,其可由具有相对较低耐压的晶体管实施。

4.在一些实施例中,发射器包括位准转换电路、边缘调整电路以及驱动器。位准转换电路基于一输入信号产生多个第一信号与多个第二信号,其中所述输入信号的电压范围、多个第一信号的电压范围与多个第二信号的电压范围彼此不同。边缘调整电路根据多个第一信号与多个第二信号调整一第一节点的位准以及一第二节点的位准,并在调整所述第一节点的位准与所述第二节点的位准的过程中提供过电压保护。驱动器根据所述第一节点的位准与所述第二节点的位准产生一输出信号。

5.本技术一些实施例中的发射器可使用具有低耐压的晶体管来发射具有高位准的输出信号,并利用过电压保护与短路电流保护来确保该些晶体管不会损坏,以提高发射器的可靠度。

6.有关本技术的特征、实作与功效,兹配合图式作较佳实施例详细说明如下。

附图说明

7.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

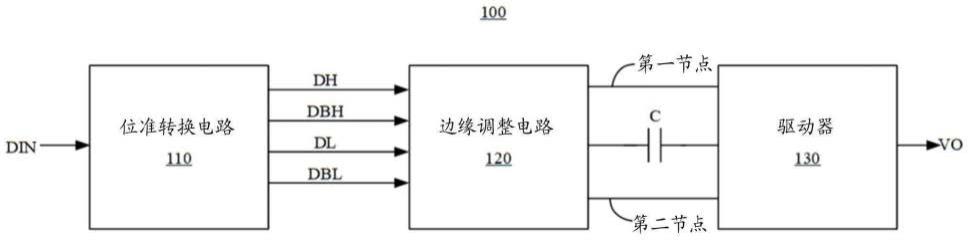

8.图1为根据本技术一些实施例绘制的一种发射器的示意图;

9.图2为根据本技术一些实施例绘制图1的位准转换电路的示意图;

10.图3a为根据本技术一些实施例绘制图1的边缘调整电路中的电路的示意图;

11.图3b为根据本技术一些实施例绘制图1的边缘调整电路中的另一电路的示意图;

12.图4为根据本技术一些实施例绘制图1中的驱动器的示意图;

13.图5a为根据本技术一些实施例绘制图3a的电路在输入信号由低位准切换至高位准且控制节点的位准仍未改变时的操作示意图;

14.图5b为根据本技术一些实施例绘制图3b的电路在输入信号由低位准切换至高位准且控制节点的位准仍未改变时的操作示意图;

15.图6a为根据本技术一些实施例绘制图3a的电路在输入信号由低位准切换至高位准且控制节点的位准改变时的操作示意图;以及

16.图6b为根据本技术一些实施例绘制图3b的电路在输入信号由低位准切换至高位准且控制节点位准改变时的操作示意图。

17.【符号说明】

18.100:发射器

19.110:位准转换电路

20.120:边缘调整电路

21.130:驱动器

22.210,220:比较电路

23.230,240,250,260:反相器

24.300a,300b:电路

25.310:下拉电路

26.315,335:电流源电路

27.320,340:保护电路

28.330:上拉电路

29.340:保护电路

30.avddh,avddl,avssh,avss:电压

31.c:电容

32.d1,d2:数据信号

33.dbh,dh,dbl,dl:信号

34.din:输入信号

35.do:输出信号

36.d1~d10:节点

37.dc:控制节点

38.do:输出节点

39.r:电阻

40.t3~t4,n1~n13:n型晶体管

41.t1~t,p1~p13:p型晶体管

42.vo:输出信号

具体实施方式

43.本文所使用的所有词汇具有其通常的意涵。上述词汇在普遍常用的字典中的定义,在本技术的内容中包括任一在此讨论的词汇的使用例子仅为示例,不应限制到本技术的范围与意涵。同样地,本技术亦不仅以此说明书所示出的各种实施例为限。

44.关于本文中所使用的“耦接”或“连接”,均可指二或多个组件相互直接作实体或电性接触,或是相互间接作实体或电性接触,亦可指二或多个组件相互操作或动作。如本文所

用,用语“电路”可为由至少一个晶体管和/或至少一个主被动组件按一定方式连接以处理信号的装置。

45.图1为根据本技术一些实施例绘制的一种发射器100的示意图。在一些实施例中,发射器100可由具有低耐压的晶体管来实施,并设置以具有过电压保护以可用来输出具有高电压位准的信号。

46.发射器100包括位准转换电路110、边缘调整电路120、驱动器130与电容c。位准转换电路110基于输入信号din产生信号dh、信号dbh、信号dl以及信号dbl。在一些实施例中,信号dh与信号dbh具有相反的位准,且信号dl与信号dbl具有相反的位准。例如,当信号dh具有高位准时,信号dbh具有低位准;反之亦然。

47.在一些实施例中,输入信号din的电压范围、信号dh与信号dbh的电压范围与信号dl与信号dbl的电压范围彼此不同。在此例中,输入信号din的电压范围大于信号dh与信号dbh的电压范围,并大于信号dl与信号dbl的电压范围。例如,输入信号din的电压范围可由图2中的电压avss以及电压avddh而定,其中电压avss为输入信号din的电压范围的下限,且电压avddh为输入信号din的电压范围的上限。信号dh与信号dbh的电压范围可由图2中的电压avssh以及电压avddh而定,其中电压avssh为信号dh与信号dbh的电压范围的下限,且电压avddh为信号dh与信号dbh的电压范围的上限。信号dl与信号dbl的电压范围可由图2中的电压avss以及电压avddl而定,其中电压avss为信号dl与信号dbl的电压范围的下限,且电压avddl为信号dl与信号dbl的电压范围的上限。其中,电压avddh高于电压avddl,电压avddl高于电压avssh,且电压avssh高于电压avss。

48.例如,电压avddh可约为3.3伏特,电压avddl可约为1.8伏特,电压avssh可约为1.5伏特,且电压avss可约为0伏特。据此,应当理解,信号dh与信号dbh的电压范围的上限(即电压avddh)高于信号dl与信号dbl的电压范围的上限(即电压avssh),且信号dh与信号dbh的电压范围的下限(即电压avssh)高于信号dl与信号dbl的电压范围的下限(即电压avss)。上述关于各电压的数值仅用于示例,且本技术并不以此为限。在其它的实施例中,电压avddl与电压avssh可设置为电压avddh的一半。

49.边缘调整电路120根据信号dh、信号dbh、信号dl以及信号dbl调整第一节点(例如为图3a的节点d1)的位准以及第二节点(例如为图3a的节点d3)的位准,并在调整第一节点与第二节点两者的位准的过程中提供一过电压保护。在一些实施例中,位准转换电路110、边缘调整电路120与驱动器130中每一者可由多个晶体管实施,其中该多个晶体管的耐压低于输入信号din的电压范围的上限(例如为电压avddh)。例如,如前所述,电压avddh可约为3.3伏特,而上述的多个晶体管的耐压可约为1.8伏特。为了避免边缘调整电路120中的晶体管在位准调整的过程中损坏,边缘调整电路120可对其内部晶体管提供过电压保护。另一方面,位准转换电路110与驱动器130可通过电路连接关系来避免损坏。

50.驱动器130经由电容c耦接至边缘调整电路120的一节点(例如为图3a中的控制节点),并根据第一节点的位准以及第二节点的位准产生输出信号vo。在一些实施例中,通过边缘调整电路120,驱动器130不会产生过大的短路电路(或称串通电流),以避免驱动器130出现损坏。在一些实施例中,通过调整边缘调整电路120中的偏压电流,可调整输出信号vo的上升边缘以及下降边缘。关于上述各电路的详细设置方式与操作将于后参照各图式说明。

51.图2为根据本技术一些实施例绘制图1的位准转换电路110的示意图。位准转换电路110包括比较电路210、比较电路220、多个反相器230、240、250与260。比较电路210将输入信号din与电压avssh中具有较高的位准的一者输出为数据信号d1。比较电路220将输入信号din与电压avddl中具有较低的位准的一者输出为数据信号d2。反相器230以及反相器240串联耦接,以根据数据信号d1依序产生信号dbh以及信号dh,其中反相器230与反相器240操作于信号dbh与信号dh的电压范围,亦即反相器230与反相器240是操作于电压avddh与电压avssh之间。反相器250以及反相器260串联耦接,以根据数据信号d2依序产生信号dbl以及信号dl,其中反相器250与反相器260操作于信号dbl与信号dl的电压范围,亦即反相器250与反相器260是操作于电压avddl与电压avss之间。

52.详细而言,比较电路210包括多个p型晶体管t1与t2。p型晶体管t1的第一端(例如为源极)接收输入信号din,p型晶体管t1的第二端(例如为汲极)输出数据信号d1,p型晶体管t1的控制端(例如为闸极)接收电压avssh,且p型晶体管t1的第四端(例如为基极)接收电压avddh。p型晶体管t2的第一端接收电压avssh,p型晶体管t2的第二端耦接至p型晶体管t1的第二端,p型晶体管t2的控制端接收输入信号din,且p型晶体管t2的第四端接收电压avddh。p型晶体管t1可根据电压avssh与输入信号din选择性导通,以输出电压avssh为数据信号d1。p型晶体管t2可根据电压avssh与输入信号din选择性导通,以输出数据信号din为数据信号d1。例如,若电压avssh高于输入信号din,p型晶体管t1导通且p型晶体管t2不导通。在此条件下,p型晶体管t1可将电压avssh输出为数据信号d1。或者,若输入信号din高于电压avssh,p型晶体管t2导通且p型晶体管t1不导通。在此条件下,p型晶体管t2可将输入信号din输出为数据信号d1。再者,通过上述连接方式,可使p型晶体管t1与t2中每一者的任意两端之间的跨压都不超过前述的耐压(例如为1.8伏特)。

53.类似地,比较电路220包括多个n型晶体管t3与t4。n型晶体管t3的第一端(例如为汲极)接收输入信号din,n型晶体管t3的第二端(例如为源极)输出数据信号d2,n型晶体管t3的控制端(例如为闸极)接收电压avddl,且n型晶体管t3的第四端(例如为基极)接收电压avss。n型晶体管t4的第一端接收电压avddl,n型晶体管t4的第二端耦接至n型晶体管t3的第二端,n型晶体管t4的控制端接收输入信号din,且n型晶体管t4的第四端接收电压avss。n型晶体管t3可根据电压avddl与输入信号din选择性导通,以将输入信号din输出为数据信号d2。n型晶体管t4可根据电压avddl与输入信号din选择性导通,以将电压avddl输出为数据信号d2。例如,若电压avddl高于输入信号din,n型晶体管t3导通且n型晶体管t4不导通。在此条件下,n型晶体管t3可将输入信号din输出为数据信号d1。或者,若输入信号din高于电压avddl,n型晶体管t4导通且n型晶体管t3不导通。在此条件下,n型晶体管t4可将电压avddl输出为数据信号d2。通过上述连接方式,可使n型晶体管t3与t4中每一者的任意两端之间的跨压都不超过前述的耐压。

54.在一些实施例中,图1的边缘调整电路120包括图3a的电路300a以及图3b的电路300b。电路300a可根据信号dl(即信号dl与信号dbl中的对应者)、信号dh与信号dbh调整第一节点的位准,以调整输出信号vo的上升边缘。电路300b可根据信号dh(即信号dh与信号dbh中的对应者)、信号dl与信号dbl调整第二节点的位准,以调整输出信号vo的下降边缘。为易于理解,以下将参照图3a与图3b依序说明上述各电路的设置方式。

55.图3a为根据本技术一些实施例绘制图1的边缘调整电路120中的电路300a的示意

图。电路300a包括下拉电路310以及保护电路320。下拉电路310根据信号dl、信号dh与信号dbh下拉节点d1的位准并调整控制节点dc的位准。保护电路320根据控制节点dc的位准、电压avssh与电压avddl对下拉电路310提供过电压保护。

56.详细而言,下拉电路310包括多个p型晶体管p1~p3、多个n型晶体管n1~n2以及电流源电路315。p型晶体管p1的第一端接收电压avddh,p型晶体管p1的第二端耦接至节点d1,且p型晶体管p1的控制端接收信号dh。p型晶体管p1根据信号dh选择性导通,以传输电压avddh至节点d1。换言之,当p型晶体管p1导通时,节点d1的位准可上拉至电压avddh。p型晶体管p2的第一端耦接至节点d1,p型晶体管p2的第二端耦接至节点d3,且p型晶体管p2的控制端接收信号dbh。p型晶体管p2根据信号dbh选择性导通,以将节点d1耦接至节点d3。p型晶体管p3的第一端耦接至节点d3,p型晶体管p3的第二端耦接至控制节点dc,且p型晶体管p3的控制端接收电压avssh。p型晶体管p3根据电压avssh与节点d3的位准选择性导通,以将节点d3耦接至控制节点dc。

57.n型晶体管n1的第一端耦接至控制节点dc,n型晶体管n1的第二端耦接至节点d4,且n型晶体管n1的控制端接收电压avddl。n型晶体管n1根据电压avddl与节点d4的位准选择性导通,以将控制节点dc耦接至节点d4。n型晶体管n2的第一端耦接至节点d4,n型晶体管n2的第二端经由电流源电路315耦接至提供电压avss的电压源,且n型晶体管n2的控制端接收信号dl。n型晶体管n2根据信号dl的位准选择性导通,以经由电流源电路315将节点d4的位准下拉至电压avss。通过上述设置方式,应可理解,在下拉电路310中,若p型晶体管p1不导通且剩余的多个晶体管皆为导通时,节点d1可经由电流源电路315下拉至电压avss。在一些实施例中,电流源电路315为可变电流源。若电流源电路315的电流越大,下拉能力就越高,使得节点d1可更快地被下拉到电压avss。如此,可加快输出信号vo从低位准拉升到高位准的上升时间(即调整输出信号vo的上升边缘)。

58.保护电路320包括多个n型晶体管n3~n5以及多个p型晶体管p4~p6。n型晶体管n3的第一端耦接至节点d1,n型晶体管n3的第二端耦接至节点d5,且n型晶体管n3的控制端接收信号dh。n型晶体管n3根据信号dh选择性导通,以耦接节点d1至节点d5。n型晶体管n4的第一端接收电压avssh,n型晶体管n4的第二端耦接至节点d5,且n型晶体管n4的控制端接收信号dbh。n型晶体管n4根据信号dbh选择性导通,以将电压avssh传输至节点d5。p型晶体管p4的第一端接收电压avssh,p型晶体管p4的第二端耦接至节点d5,且p型晶体管p4的控制端耦接至控制节点dc。p型晶体管p4根据控制节点dc的位准选择性导通,以将电压avssh传输至节点d5。p型晶体管p5的第一端耦接至节点d3,p型晶体管p5的第二端接收电压avssh,且p型晶体管p5的控制端耦接至控制节点dc。p型晶体管p5根据控制节点dc的位准选择性导通,以将电压avssh传输至节点d3。n型晶体管n5的第一端耦接至节点d6,n型晶体管n5的第二端接收电压avddl,且n型晶体管n5的控制端耦接至控制节点dc。n型晶体管n5根据控制节点dc的位准选择性导通,以将电压avddh传输到节点d6。p型晶体管p6的第一端耦接至节点d4,p型晶体管p6的第二端耦接至节点d6,且p型晶体管p6的控制端接收信号dl。p型晶体管p6根据信号dl选择性导通,以将节点d6耦接至节点d4。关于保护电路320的操作将于后参照图5a与图6a说明。

59.图3b为根据本技术一些实施例绘制图1的边缘调整电路120中的电路300b的示意图。电路300b包括上拉电路330以及保护电路340。上拉电路330根据信号dh、信号dl与信号

dbl上拉节点d2的位准并调整控制节点dc的位准。保护电路340根据控制节点dc的位准、电压avssh与电压avddl对上拉电路330提供过电压保护。

60.详细而言,上拉电路330包括电流源电路335、多个p型晶体管p7~p8以及多个n型晶体管n6~n8。p型晶体管p7的第一端经由电流源电路335接收电压avddh,p型晶体管p7的第二端耦接至节点d7,且p型晶体管p7的控制端接收信号dh。p型晶体管p7根据信号dh选择性导通,以从电流源电路335传输电压avddh至节点d7。p型晶体管p8的第一端耦接至节点d7,p型晶体管p8的第二端耦接至控制节点dc,且p型晶体管p8的控制端接收电压avssh。p型晶体管p8根据电压avssh与节点d7的位准选择性导通,以耦接节点d7至控制节点dc。

61.n型晶体管n6的第一端耦接至控制节点dc,n型晶体管n6的第二端耦接至节点d8,且n型晶体管n6的控制端接收电压avddl。n型晶体管n6根据电压avddl以及节点d8的位准选择性导通,以耦接控制节点dc至节点d8。n型晶体管n7的第一端耦接至节点d8,n型晶体管n7的第二端耦接至节点d2,且n型晶体管n7的控制端接收信号dbl。n型晶体管n7根据信号dbl选择性导通,以将节点d8耦接至节点d2。n型晶体管n8的第一端耦接至节点d2,n型晶体管n8的第二端接收电压avss,且n型晶体管n8的控制端接收信号dl。n型晶体管n8根据信号dl选择性导通,以将电压avss传输给节点d2。通过上述设置方式,应可理解,在上拉电路330中,若n型晶体管n8不导通且剩余的多个晶体管皆为导通时,节点d2可经由电流源电路335上拉至电压avddh。在一些实施例中,电流源电路335为可变电流源。若电流源电路335的电流越大,上拉能力就越高,使得节点d2可更快地被上拉到电压avddh。如此,可加快输出信号vo从高位准下降到低位准的下降时间(即调整输出信号vo的下降边缘)。

62.保护电路340包括多个n型晶体管n9~n11以及多个p型晶体管p9~p11。p型晶体管p9的第一端耦接至节点d9,p型晶体管p9的第二端耦接至节点d2,且p型晶体管p9的控制端接收信号dl。p型晶体管p9根据信号dl选择性导通,以耦接节点d9至节点d2。p型晶体管p10的第一端耦接至节点d9,p型晶体管p10的第二端接收电压avddl,且p型晶体管p10的控制端接收信号dbl。p型晶体管p10根据信号dbl选择性导通,以将电压avddl传输至节点d9。n型晶体管n9的第一端耦接至节点d9,n型晶体管n9的第二端电压avddl,且n型晶体管n9的控制端耦接至控制节点dc。n型晶体管n9根据控制节点dc的位准选择性导通,以将电压avddl传输至节点d9。n型晶体管n10的第一端接收电压avddl,n型晶体管n10的第二端耦接至节点d8,且n型晶体管n10的控制端耦接至控制节点dc。n型晶体管n10根据控制节点dc的位准选择性导通,以将电压avddl传输至节点d8。p型晶体管p11的第一端接收电压avssh,p型晶体管p11的第二端耦接至节点d10,且p型晶体管p11的控制端耦接至控制节点dc。p型晶体管p11根据控制节点dc的位准选择性导通,以将电压avssh传输至节点d10。n型晶体管n11的第一端耦接至节点d10,n型晶体管n11的第二端耦接至节点d7,且n型晶体管n11的控制端接收信号dh。n型晶体管n11根据信号dh选择性导通,以将节点d10耦接至节点d7。关于保护电路340的操作将于后参照图5b与图6b说明。

63.图4为根据本技术一些实施例绘制图1中的驱动器130的示意图。驱动器130包括多个p型晶体管p12~p13以及多个n型晶体管n12~n13。p型晶体管p12的第一端接收电压avddh,p型晶体管p12的第二端耦接至p型晶体管p13的第一端,且p型晶体管p12的控制端耦接至图3a中的节点d1。p型晶体管p12根据节点d1的位准选择性导通,以传输电压avddh给p型晶体管p13的第一端。p型晶体管p13的第二端耦接至输出节点do,且p型晶体管p13的控制

端接收电压avssh。

64.n型晶体管n12的第一端耦接至输出节点do,n型晶体管n12的第二端耦接至n型晶体管n13的第一端,且n型晶体管n12的控制端接收电压avddh。n型晶体管n13的第二端接收电压avss,且n型晶体管n13的控制端耦接至图3b中的节点d2。n型晶体管n13根据节点d2的位准选择性导通,以下拉输出节点do的位准到电压avss。输出节点do经由图1的电容c耦接至图3a与图3b中的控制节点dc,并经由电阻r耦接至输出端(未示出)以发射输出信号vo。

65.当节点d1的位准变低时,p型晶体管p12可导通以上拉输出节点do的位准。如此,可使输出信号vo切换至高位准。或者,当节点d2的位准变高时,n型晶体管n13可导通以下拉输出节点do的位准。如此,可使输出信号vo切换至低位准。另一方面,通过边缘调整电路120,可使得p型晶体管p12的导通期间不重叠于n型晶体管n13的导通期间(即上述两个晶体管不会同时导通)。如此,可确保驱动器130不会产生短路电流,以提高发射器100的可靠度。

66.图5a为根据本技术一些实施例绘制图3a的电路300a在输入信号din由低位准切换至高位准且控制节点dc的位准仍未改变时的操作示意图。参照图2可理解。当输入信号din由低位准切换到高位准时,信号dh的位准相同于电压avddh,信号dbh的位准相同于电压avssh,且信号dl的位准相同于电压avddl。如此一来,p型晶体管p1与p6以及n型晶体管n4不导通,且p型晶体管p2~p3以及晶体管n1~n3为导通。另外,由于输入信号din在前一周期位于低位准,使得控制节点dc的位准位于高位准(相当于电压avddh)。如此,当输入信号din刚切换到高位准的初始期间内,控制节点dc的位准仍位于高位准,使得p型晶体管p4与p5不导通且n型晶体管n5为导通。基于上述条件,节点d1的位准经由晶体管p2与p3、n型晶体管n1与n2以及电流源电路315开始下拉至信号dbh与晶体管p2的临界电压的总和,且控制节点dc的位准将经由多个n型晶体管n1与n2以及电流源电路315开始下拉。

67.在上述的过程中,n型晶体管n7可耦接节点d1至节点d5。如前所述,节点d1的位准会调整为信号dbh与晶体管p2的临界电压的总和。如此,可确保n型晶体管n4、p型晶体管p4与p型晶体管p5中任一者的两端之间的跨压不会超过其耐压值。再者,n型晶体管n5可传输电压avddl至节点d6,以确保p型晶体管p6的两端之间的跨压不超过其耐压值。此外,当节点d1的位准下降时,图4的p型晶体管p12会开始导通而上拉输出节点do的位准,以开始产生具有高位准的输出信号vo。

68.图5b为根据本技术一些实施例绘制图3b的电路300b在输入信号din由低位准切换至高位准且控制节点dc的位准仍未改变时的操作示意图。参照图2可理解。当输入信号din由低位准切换到高位准时,信号dbl的位准相同于电压avss。如前所述,当输入信号din刚切换到高位准的初始期间内,控制节点dc的位准仍位于高位准。在此条件下,p型晶体管p7、p9以及p11不导通且n型晶体管n8导通。如此,n型晶体管n8可快速地下拉节点d2的位准到电压avss。如此,图4的n型晶体管n13将快速关断,以避免产生短路电流。另一方面,n型晶体管n9~n10与p型晶体管p10导通,使得节点d9与节点d8的位准皆为电压avddl,且n型晶体管n11与p型晶体管p8导通,使得节点d7与节点d10的位准接近于控制节点dc的位准。通过上述设置方式,可以确保电路300b中的任一晶体管的两端之间的跨压不超过其耐压值。

69.图6a为根据本技术一些实施例绘制图3a的电路300a在输入信号din由低位准切换至高位准且控制节点dc的位准改变时的操作示意图。延续图5a的操作,当控制节点dc的位准经由n型晶体管n1与n2以及电流源电路315下拉到低位准(例如为电压avss)时,p型晶体

管p4与p5导通且n型晶体管n5不导通。在此条件下,节点d5与节点d3的位准皆为电压avssh,使得p型晶体管p2与p3为不导通。如此,n型晶体管n3可使节点d1的位准完全下拉至电压avssh。如此一来,图4的p型晶体管p12可完全导通。通过上述设置方式,电路300a的内部节点的位准皆可固定在一特定电压,以确保电路300a中任一晶体管的任两端之间的跨压都不会超过其耐压值。

70.图6b为根据本技术一些实施例绘制图3b的电路300b在输入信号din由低位准切换到高位准且控制节点dc的位准改变时的操作示意图。延续图5b的操作,当控制节点dc的位准经由图6a的n型晶体管n1与n2以及电流源电路315下拉到低位准(例如为电压avss)时,p型晶体管p11导通且n型晶体管n9与n10不导通。在此条件下,节点d10与节点d7的位准皆为电压avssh,使得p型晶体管p8不导通。由于p型晶体管p10仍为导通,节点d9的位准不会改变(维持在电压avddl)。由于多个n型晶体管n6与n7仍为不导通,节点d8的位准亦不改变。如此,电路300b的内部节点的位准皆可固定在一特定电压,以确保电路300b中任一晶体管的任两端跨压都不会超过其耐压值。

71.通过图5a、图5b、图6a与图6b的说明可理解,在输入信号din从低位准切换到高位准的过程中,电路300a在图5a以及图6a的操作中逐步地将节点d1的位准拉低到电压avssh,以逐步导通图4的p型晶体管p12。相对的,电路300b可在图5b的操作中快速拉低节点d2的位准到电压avssh,以快速关闭图4的n型晶体管n13。如此,可确保图4中的p型晶体管p12与n型晶体管n13不会同时完全导通,以确保驱动器130不会产生过大的短路电流。

72.类似地,在输入信号din从高位准切换到低位准时,若控制节点dc的位准仍未改变(维持在前一周期的低位准),根据信号dh、dbl、dl的位准,上拉电路330可将节点d2的位准上拉至信号dbl减去n型晶体管n7的临界电压后的位准。同时,下拉电路310中的p型晶体管p1导通而将节点d1的位准快速上拉到电压avddh,以确保图4的p型晶体管p12可快速关断。接着,当控制节点dc的位准上拉到电压avddh时,上拉电路330可将节点d2的位准完全上拉到电压avddh,以确保图4的n型晶体管n13可完全导通。如此,可确保在输入信号din从高位准切换到低位准的过程中,图4中的p型晶体管p12与n型晶体管n13不会同时完全导通,以确保驱动器130不会产生过大的短路电流。

73.由于电路300a与电路300b具有类似的镜像对称结构,电路300a与电路300b的操作之间亦具有相对应的关系。因此,可根据图5a、图5b、图6a与图6b的操作过程理解电路300a与电路300b在输入信号din从高位准切换到低位准的过程中执行的相关操作,故于此不再重复赘述。通过上述说明,应可理解,在输入信号din的位准发生切换的过程中,保护电路320与保护电路340可固定下拉电路310与上拉电路330中的多个内部节点的位准,以提供上述两者过电压保护来确保上述两者的任一晶体管的两端跨压不会过高。

74.需要说明的是,本技术实施例中,“多个”指代“两个及两个以上”75.综上所述,本技术一些实施例中的发射器可使用具有低耐压的晶体管来发射具有高位准的输出信号,并利用过电压保护与短路电流保护来确保该些晶体管不会损坏,以提高发射器的可靠度。

76.以上对本技术实施例所提供的具有过电压保护的发射器进行了详细介绍。本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的方法及其核心思想;同时,对于本领域的技术人员,依据本技术的思想,在具

体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本技术的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1