一种降压与推挽级联式DC-DC变换器及其控制芯片的制作方法

一种降压与推挽级联式dc-dc变换器及其控制芯片

技术领域

1.本发明属于电源变换技术领域,具体涉及降压与推挽级联式dc-dc变换器及其控制芯片。

背景技术:

2.随着现代工业及国防技术的发展,对高压大功率dc-dc模块电源的功率等级、电压等级、效率以及体积与重量等技术要求也在不断提高,这对电源模块的设计者们提出了新的挑战。双端拓扑结构因其对变压器磁芯的充分利用,不需要额外的磁芯复位电路,从而减小了电源体积,是高功率密度应用的最佳拓扑选择。单级的隔离型变换器很难同时兼顾高压输入、低压大电流输出和高功率密度的要求,级联式拓扑则能很好的兼顾各方面的需求。

技术实现要素:

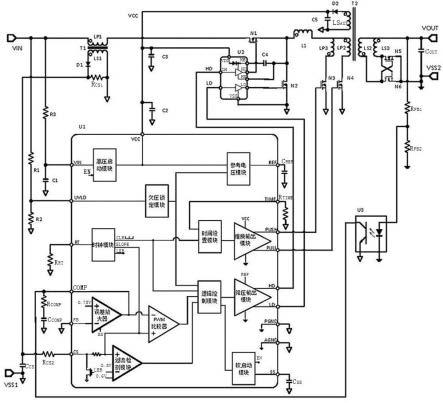

3.为达到上述目的,本发明提供了一种宽输入范围、高功率密度、便于多路输出的降压与推挽级联式电流模dc-dc变换器,本发明的技术方案如下:一种降压与推挽级联式电流模dc-dc变换器控制芯片,所述芯片包括高压启动模块、参考电压模块、欠压锁定模块、时钟模块、误差放大器、pwm比较器、过流检测模块及逻辑控制模块,所述芯片还包括时间设置模块,时间设置模块包括:压流转换器,压流转换器包括放大器amp01、nmos管n01、nmos管n02、nmos管n03、pmos管p01、pmos管p02、pmos管p03和电阻r

time

,实现外置电阻r

time

对内部充放电电流的调节;时间设置电路,时间设置电路包括反相器inv01、反相器inv02、反相器inv03、反相器inv04、反相器inv05、放大器amp02、放大器amp03、电容c_push、电容c_pull、pmos管p04、pmos管p05、nmos管n04和nmos管n05,组成对死区时间或交叠时间的设置;time管脚对外连接电阻r

time

,通过内部时间设置模块和电阻r

time

来兼容电压和电流两种环路控制模式。

4.作为本发明的一种改进,所述压流转换器中,放大器amp01的反相输入端连接time管脚和其输出端,其输出端连接pmos管p01和nmos管n01的漏端,pmos管p01的源端连接pmos管p02的源端和pmos管p03的源端,pmos管p01的栅端连接pmos管p02的栅端和pmos管p03的栅端,pmos管p01的栅端和漏端连接,nmos管n01的栅端连接nmos管n02的栅端和nmos管n03的栅端,nmos管n01的源端连接nmos管n02的源端和nmos管n03的源端,nmos管n01的栅端和漏端相连,pmos管p02的漏端生成电流i_ot1,nmos管n02的漏端生成电流i_dt1,pmos管p03的漏端生成电流i_ot2,nmos管n03的漏端生成电流i_dt2。

5.作为本发明的一种改进,时间设置电路中,反相器inv02的输入端接信号clk、nmos管n04的栅端及pmos管p04的栅端,反相器inv02的输出端接pmos管p05和nmos管n05的栅端,pmos管p04的漏端连接nmos管n04的漏端、反相器inv01的输出端及放大器amp02的反相输入端,pmos管p04的源端接电流i_ot1,nmos管n04的源端连接电流i_dt1, pmos管p05的源端接电流i_ot2,pmos管p05的漏端接nmos管n05的漏端、反相器inv03的输出端及放大器amp03的反相输入端,nmos管n05的源端接电流i_dt2,放大器amp02的同相输入端接vref,其反相输入端连接电容c_push的一端,电容c_push另一端接地,放大器amp03的同相输入端接vref,

其反相输入端连接电容c_pull,电容c_pull另一端接地,放大器amp02的输出端连接反相器inv04的输入端,放大器amp03的输出端连接反相器inv05的输入端。

6.作为本发明的一种改进,nmos管n01、nmos管n02、nmos管n03、pmos管p01、pmos管p02、pmos管p03组成的电流镜比例系数均为1:1,其中,i_ot1=i_ot2=i_dt1=i_dt2=(vref/2)/r

time

,死区时间δt1=[c_push*(v

ref

/2)]/i_dt1,交叠时间δt2=[c_push*(v

ref

/2)]/i_ot1。

[0007]

以交叠时间设置为例,电阻r

time

一端接地,另一端接time管脚,运算放大器amp01构成的电压跟随器的输出信号会在电阻r

time

上形成恒定的对地下拉电流,该电流信号再由pmos管p01、p02和p03组成的电流镜传导至p04和p05的漏端,与电容c_push和c_pull组成延时电路,并产生一组有固定交叠时间的脉冲信号push_in和pull_in。

[0008]

一种降压与推挽级联式dc-dc变换器,所述变换器主控电路,主控电路包括上述所述芯片u1、电阻r1、电阻r2、电阻r

rt

、电阻r

time

、电容c

ss

和电容c

ref

,芯片u1的hd管脚连接芯片u2的ih管脚,芯片u1的ld管脚连接芯片u2的il管脚,芯片u1的push管脚连接nmos管n3的栅端,电阻r1一端连接变压器t1原边绕组lp1的同名端,另一端连接电阻r2和芯片u1的uvlo管脚,电阻r

rt

连接芯片u1的rt管脚,电阻r

time

连接芯片u1的time管脚,电容c

ss

连接芯片u1的ss管脚,电容c

ref

连接芯片u1的ref管脚。

[0009]

作为本发明的一种改进,控制芯片u1产生降压驱动信号hd和ld、推挽输出信号push和pull,降压驱动信号hd和ld的波形完全互补,相位差为180

°

,频率与内部时钟信号一致,推挽输出信号push和pull为50%的占空比pwm信号,频率为内部时钟信号的一半,在不同的控制模式下两者保持固定的死区时间或交叠时间。

[0010]

基于上述技术方案,电阻r1和电阻r2组成的分压器将提供线电压的欠压保护输入信号;r

rt

可以设置内置振荡器的频率;r

time

可以通过对地或者对r

ef

脚连接来设置交叠或者死区时间的长短,保证变换器在各种控制模式下的稳定工作;c

ss

可以设置系统软起动的时间长短;c

ref

可以为r

ef

稳定瞬态电压,减小其纹波。

[0011]

作为本发明的一种改进,所述变换器还包括:降压输出驱动电路,包括芯片u2、电容c3、电容c4、电感l1、nmos管n1及nmos管n2,芯片u2的vcc管脚接vdd,电容c3连接芯片u2的vdd管脚,电容c4的一端连接芯片u2的hb管脚,另一端连接芯片u2的hs管脚与nmos管n2的漏端和电感l1之间,nmos管n1的栅端连接芯片u2的ho管脚,其源端连接nmos管n2的漏端和电感l1的一端,其漏端连接变压器t1的原边绕组lp1同名端,nmos管n2的栅端连接芯片u2的lo管脚,其源端接芯片u2的vss管脚和地;控制芯片u1产生的pwm信号hd和ld输入到芯片u2中,然后nmos管n1和nmos管n2(驱动功率管)的翻转,通过电感l1后产生的电压为后级推挽拓扑供电,其电压v_l1=vin*d,d为hd的占空比。电容c3作为去耦电容,滤除vcc的杂波,电容c4为高压电容为芯片u2供电。

[0012]

推挽输出电路,包括变压器t2、nmos管n3、nmos管n4、nmos管n5、nmos管n6和电容c

out

,变压器t2的原边绕组lp2同名端连接原边绕组lp3的异名端,原边绕组lp2的异名端连接nmos管n4的漏端,nmos管n4的源端接地,nmos管n4的栅端连接芯片u1的pull管脚,nmos管n4的栅端的控制信号由push管脚产生,变压器t2的原边绕组lp3的异名端连接电感l1的一侧,原边绕组lp3的同名端连接nmos管n3的漏端,nmos管n3的源端接地,变压器t2的副边绕

组ls2的同名端连接nmos管n6的漏端和nmos管n5的栅端,副边绕组ls2的异名端连接副边绕组ls3的同名端,变压器t2的副边绕组ls3的同名端连接vout端,副边绕组ls3的异名端连接nmos管n5的漏端和nmos管n6的栅端,电容c

out

一端连接在副边绕组ls3的同名端另一端副边接地。原边绕组lp2和副边绕组ls2组成一个变压器,原边绕组lp3和副边绕组ls3组成一个变压器,两个变压器共用一个磁芯。

[0013]

芯片u1的推挽信号将直接驱动nmos管n3和nmos管n4,正极变压器t2由五个绕组组成,其中原边绕组lp2、原边绕组lp3、副边绕组ls2和副边绕组ls3参与输入电压到输出电压的功率变换,ls

aux

为辅助绕组,专门为控制芯片供电。变压器的输出由nmos管n5和nmos管n6构成的整流电路整流后,将对c

out

进行充电同时输出电压信号vout。

[0014]

基于上述技术方案,启动阶段芯片u1的vcc脚产生电源信号vcc,通过u2的vdd脚来给u2供电;而启动后,辅助绕组ls

aux

出来的电压经过二极管d2整流后产生电源vcc,给芯片u1和芯片u2供电。

[0015]

作为本发明的一种改进,所述变换器还包括启动电路,包括电阻r3、电容c1、电容c2、电容c5、二极管d2及辅助绕组ls

aux

,电阻r3一端连接变压器t1的原边绕组lp1的同名端,另一端连接电容c1和芯片u1的vin管脚,二极管d2的正极接辅助绕组ls

aux

同名端,电容c5连接于二极管d2的负极和辅助绕组ls

aux

异名端之间,辅助绕组ls

aux

异名端接地。

[0016]

基于上述技术方案,因为控制芯片集成了高压启动电路,所以输入电压vin可直接通过启动限流电阻r3对启动电容c1进行充电,随着vin电压的升高,控制芯片u1将产生vcc电压信号给电容c2充电,9v的vcc电压稳定后系统将开始软启动,并且开始由辅助绕组ls

aux

通过整流二极管d2对电容c5进行充电,直到的电压高于一定值后,它将完全取代内部的启动模块为控制芯片u1供电,同时也为半桥驱动芯片u2供电。集成的高压启动模块最大充电电流可达25ma,使得系统的启动时间从数百毫秒降低到几十毫秒,同时也提高了变换器的效率。

[0017]

作为本发明的一种改进,所述变换器还包括过流采样电路,包括变压器t1、二极管d1、电阻r

cs1

、电阻r

cs2

和电容c

cs

,变压器的副边绕组ls1同名端连接二极管d1的正极,副边绕组ls1异名端接地,副边绕组lp1的同名端接vin端,电阻r

cs1

连接于二极管d1的负极和副边绕组ls1异名端之间,电阻r

cs1

和二极管d1的负极之间还连接电容c

cs

和电阻r

cs2

,电阻r

cs2

另一端连接芯片u1的cs管脚。

[0018]

基于上述技术方案,电流采样变压器t1将对输入电流进行采样,通过整流二极管d1后在r

cs1

上产生过流采样的输入信号,并通过电阻r

cs2

和电容c

cs

组成低通滤波器后输入至控制芯片,实时监控系统的电流,防止磁饱和或者短路等异常情况下对变换器的损害。

[0019]

作为本发明的一种改进,所述变换器还包括反馈调节电路,包括电阻r

fb1

、电阻r

fb2

、光耦u3、电阻r

comp

和电容c

comp

组成,电阻r

fb1

一端连接副边绕组ls3同名端,另一端连接电阻r

fb2

,阻r

fb2

的另一端接地,光耦u3的输入端连接于电阻r

fb1

和电阻r

fb2

之间,其输出端连接芯片u1的comp管脚,电阻r

comp

一端连接芯片u1的comp管脚一端连接电容c

comp

。

[0020]

基于上述技术方案,电阻r

fb1

和电阻r

fb2

组成的分压器将对输出电压v

out

进行采样,经过光耦u3完成隔离信号的传输,再通过comp脚来调控pwm信号的占空比,实现对输出电压的反馈调节,而电阻r

comp

和电容c

comp

则构成一个零点来实现对系统环路的频率补偿。

[0021]

相对于现有技术,本发明的有益效果为:

1)采用级联式双端拓扑结构,兼顾了宽范围输入和低压大电流输出的限制,精简了外围电路,缩小了系统体积,提升了系统的功率密度。

[0022]

2)控制芯片可兼电压模式和电流模式两种环路控制模式,适用于全桥、半桥、推挽等拓扑结构,同时具有较宽的入电压范围,对于各种应用环境和多路输出都有良好的适应性。

[0023]

3)控制芯片集成了高压启动模块,启动电流小,功耗低,转化效率高(在成品测试得到启动电流仅150μa, 正常工作时功耗小于4ma,系统效率可达90%以上)。

附图说明

[0024]

图1为本发明时间设置模块的电路结构示意图。

[0025]

图2为本发明关键信号的波形示意图。

[0026]

图3为本发明降压与推挽级联式电流模dc-dc变换器电路结构示意图。

[0027]

图4为本发明降压与推挽级联拓扑示意图。

具体实施方式

[0028]

下面结合附图和具体实施方式,进一步阐明本发明,应理解下述具体实施方式仅用于说明本发明而不用于限制本发明的范围。

[0029]

实施例:如图1所示,一种降压与推挽级联式电流模dc-dc变换器控制芯片,所述芯片包括高压启动模块、参考电压模块、欠压锁定模块、时钟模块、误差放大器、pwm比较器、过流检测模块及逻辑控制模块,所述芯片还包括时间设置模块,时间设置模块包括:压流转换器,压流转换器包括放大器amp01、nmos管n01、nmos管n02、nmos管n03、pmos管p01、pmos管p02、pmos管p03和电阻r

time

,time管脚对外连接电阻r

time

,通过内部时间设置模块和电阻r

time

来兼容电压和电流两种环路控制模式,实现外置电阻r

time

对内部充放电电流的调节,nmos管n01、nmos管n02、nmos管n03和pmos管p01、pmos管p02、pmos管p03都是相同宽长比的mos管,它们组成的电流镜的比例系数均为1:1,则有i_ot1=i_ot2=i_dt1=i_dt2=(v

ref

/2)/ r

time

;时间设置电路,时间设置电路包括反相器inv01、反相器inv02、反相器inv03、反相器inv04、反相器inv05、放大器amp02、放大器amp03、电容c_push、电容c_pull、pmos管p04、pmos管p05、nmos管n04和nmos管n05,组成对死区时间或交叠时间的设置(其中c_push=c_pull);死区时间δt1=[c_push*(v

ref

/2)]/i_dt1,交叠时间δt2=[c_push*(v

ref

/2)]/i_ot1。

[0030]

以交叠时间设置为例,电阻r

time

一端接地,另一端接time管脚,运算放大器amp01构成的电压跟随器的输出信号会在电阻r

time

上形成恒定的对地下拉电流,该电流信号再由pmos管p01、p02和p03组成的电流镜传导至p04和p05的漏端,与电容c_push和c_pull组成延时电路,并产生一组有固定交叠时间的脉冲信号push_in和pull_in。

[0031]

以电流控制模式为例,其主要信号的波形如图2所示,其中t1=0.22μs,为内部时钟信号clk的脉宽;时钟信号的周期t=t1+t2,t2为clk的低电平时间;另一个时钟信号clk2的频率为clk的一半;δt为推挽信号的交叠时间。

[0032]

所述压流转换器中,放大器amp01的反相输入端连接time管脚和其输出端,其输出

端连接pmos管p01和nmos管n01的漏端,pmos管p01的源端连接pmos管p02的源端和pmos管p03的源端,pmos管p01的栅端连接pmos管p02的栅端和pmos管p03的栅端,pmos管p01的栅端和漏端连接,nmos管n01的栅端连接nmos管n02的栅端和nmos管n03的栅端,nmos管n01的源端连接nmos管n02的源端和nmos管n03的源端,nmos管n01的栅端和漏端相连,pmos管p02的漏端生成电流i_ot1,nmos管n02的漏端生成电流i_dt1,pmos管p03的漏端接i_ot2,nmos管n03的漏端生成电流i_dt2。

[0033]

时间设置电路中,反相器inv02的输入端接信号clk、nmos管n04的栅端及pmos管p04的栅端,反相器inv02的输出端接pmos管p05和nmos管n05的栅端,pmos管p04的漏端连接nmos管n04的漏端、反相器inv01的输出端及放大器amp02的反相输入端,pmos管p04的源端接电流i_ot1,nmos管n04的源端连接电流i_dt1, pmos管p05的源端接电流i_ot2,pmos管p05的漏端接nmos管n05的漏端、反相器inv03的输出端及放大器amp03的反相输入端,nmos管n05的源端接电流i_dt2,放大器amp02的同相输入端接vref,其反相输入端连接电容c_push的一端,电容c_push另一端接地,放大器amp03的同相输入端接vref,其反相输入端连接电容c_pull,电容c_pull另一端接地,放大器amp02的输出端连接反相器inv04的输入端,放大器amp03的输出端连接反相器inv05的输入端。

[0034]

如图3所示,一种降压与推挽级联式dc-dc变换器,所述变换器主控电路,主控电路包括上述所述的芯片u1、电阻r1、电阻r2、电阻r

rt

、电阻r

time

、电容c

ss

和电容c

ref

,芯片u1的hd管脚连接芯片u2的ih管脚,芯片u1的ld管脚连接芯片u2的il管脚,芯片u1的push管脚连接nmos管n3的栅端,电阻r1一端连接变压器t1原边绕组lp1的同名端,另一端连接电阻r2和芯片u1的uvlo管脚,电阻r

rt

连接芯片u1的rt管脚,电阻r

time

连接芯片u1的time管脚,电容c

ss

连接芯片u1的ss管脚,电容c

ref

连接芯片u1的ref管脚。

[0035]

控制芯片u1产生降压驱动信号hd和ld、推挽输出信号push和pull,降压驱动信号hd和ld的波形完全互补,相位差为180

°

,频率与内部时钟信号一致,推挽输出信号push和pull为50%的占空比pwm信号,频率为内部时钟信号的一半,在不同的控制模式下两者保持固定的死区时间或交叠时间。电阻r1和电阻r2组成的分压器将提供线电压的欠压保护输入信号;r

rt

可以设置内置振荡器的频率;r

time

可以通过对地或者对r

ef

脚连接来设置交叠或者死区时间的长短,保证变换器在各种控制模式下的稳定工作;c

ss

可以设置系统软起动的时间长短;c

ref

可以为r

ef

稳定瞬态电压,减小其纹波。

[0036]

所述变换器还包括:降压输出驱动电路和推挽输出电路,降压与推挽的级联式拓补如图4所示,前级为降压拓补结构,后级为推挽拓补结构,降压电路对输入电压进行降压变换,得到的输出将作为推挽电路的电源输入,即共用的电感l1对于推挽电路来说相当于一个电流源。而与单级的推挽拓扑相比,省掉了初级电容和次级电感,有效的提高了功率密度。此外,因为电压调节由降压电路完成,推挽级的开关管电压应力较小,且与输入电压无关,输入电压范围可以做到很宽。

[0037]

降压输出驱动电路,包括芯片u2、电容c3、电容c4、电感l1、nmos管n1及nmos管n2,芯片u2的vcc管脚接vdd,电容c3连接芯片u2的vdd管脚,电容c4的一端连接芯片u2的hb管脚,另一端连接芯片u2的hs管脚与nmos管n2的漏端和电感l1之间,nmos管n1的栅端连接芯片u2的ho管脚,其源端连接nmos管n2的漏端和电感l1的一端,其漏端连接变压器t1的原边绕组lp1同名端,nmos管n2的栅端连接芯片u2的lo管脚,其源端接芯片u2的vss管脚和地;

控制芯片u1产生的pwm信号hd和ld输入到芯片u2中,然后nmos管n1和nmos管n2(驱动功率管)的翻转,通过电感l1后产生的电压为后级推挽拓扑供电,其电压v_l1=vin*d,d为hd的占空比。电容c3作为去耦电容,滤除vcc的杂波,电容c4为高压电容为芯片u2供电。

[0038]

推挽输出电路,包括变压器t2、nmos管n3、nmos管n4、nmos管n5、nmos管n6和电容c

out

,变压器t2的原边绕组lp2同名端连接原边绕组lp3的异名端,原边绕组lp2的异名端连接nmos管n4的漏端,nmos管n4的源端接地,nmos管n4的栅端连接芯片u1的pull管脚,nmos管n4的栅端的控制信号由push管脚产生,变压器t2的原边绕组lp3的异名端连接电感l1的一侧,原边绕组lp3的同名端连接nmos管n3的漏端,nmos管n3的源端接地,变压器t2的副边绕组ls2的同名端连接nmos管n6的漏端和nmos管n5的栅端,副边绕组ls2的异名端连接副边绕组ls3的同名端,变压器t2的副边绕组ls3的同名端连接vout端,副边绕组ls3的异名端连接nmos管n5的漏端和nmos管n6的栅端,电容c

out

一端连接在副边绕组ls3的同名端另一端副边接地。原边绕组lp2和副边绕组ls2组成一个变压器,原边绕组lp3和副边绕组ls3组成一个变压器,两个变压器共用一个磁芯。

[0039]

芯片u1的推挽信号将直接驱动nmos管n3和nmos管n4,正极变压器t2由五个绕组组成,其中原边绕组lp2、原边绕组lp3、副边绕组ls2和副边绕组ls3参与输入电压到输出电压的功率变换,ls

aux

为辅助绕组,专门为控制芯片供电。变压器的输出由nmos管n5和nmos管n6构成的整流电路整流后,将对c

out

进行充电同时输出电压信号vout,启动阶段芯片u1的vcc脚产生电源信号vcc,通过u2的vdd脚来给u2供电;而启动后,辅助绕组ls

aux

出来的电压经过二极管d2整流后产生电源vcc,给芯片u1和芯片u2供电。

[0040]

所述变换器还包括启动电路,包括电阻r3、电容c1、电容c2、电容c5、二极管d2及辅助绕组ls

aux

,电阻r3一端连接变压器t1的原边绕组lp1的同名端,另一端连接电容c1和芯片u1的vin管脚,二极管d2的正极接辅助绕组ls

aux

同名端,电容c5连接于二极管d2的负极和辅助绕组ls

aux

异名端之间,辅助绕组ls

aux

异名端接地。因为控制芯片集成了高压启动电路,所以输入电压vin可直接通过启动限流电阻r3对启动电容c1进行充电,随着vin电压的升高,控制芯片将产生9v的vcc电压给电容c2充电,9v的vcc电压稳定后系统将开始软启动,并且开始由辅助绕组ls

aux

通过整流二极管d2对电容c5进行充电,直到的电压高于9.3v后,它将完全取代内部的启动模块为控制芯片供电。集成的高压启动模块最大充电电流可达25ma,使得系统的启动时间从数百毫秒降低到几十毫秒,同时也提高了变换器的效率。

[0041]

所述变换器还包括过流采样电路,包括变压器t1、二极管d1、电阻r

cs1

、电阻r

cs2

和电容c

cs

,变压器的副边绕组ls1同名端连接二极管d1的正极,副边绕组ls1异名端接地,lp1的同名端接vin端,电阻r

cs1

连接于二极管d1的负极和副边绕组ls1异名端之间,电阻r

cs1

和二极管d1的负极之间还连接电容c

cs

和电阻r

cs2

,电阻r

cs2

另一端连接芯片u1的cs管脚。电流采样变压器t1将对输入电流进行采样,通过整流二极管d1后在r

cs1

上产生过流采样的输入信号,并通过电阻r

cs2

和电容c

cs

组成低通滤波器后输入至控制芯片,实时监控系统的电流,防止磁饱和或者短路等异常情况下对变换器的损害。

[0042]

所述变换器还包括反馈调节电路,包括电阻r

fb1

、电阻r

fb2

、光耦u3、电阻r

comp

和电容c

comp

组成,电阻r

fb1

一端连接副边绕组ls3同名端,另一端连接电阻r

fb2

,阻r

fb2

的另一端接地,光耦u3的输入端连接于电阻r

fb1

和电阻r

fb2

之间,其输出端连接芯片u1的comp管脚,电阻r

comp

一端连接芯片u1的comp管脚一端连接电容c

comp

。电阻r

fb1

和电阻r

fb2

组成的分压器将对

输出电压v

out

进行采样,经过光耦u3完成隔离信号的传输,再通过comp脚来调控pwm信号的占空比,实现对输出电压的反馈调节,而电阻r

comp

和电容c

comp

则是作为一个零点来实现对系统环路的频率补偿。

[0043]

工作原理:上电后,随着vin电压的升高,启动电路开始给控制芯片u1供电;当芯片u1开始工作后,将产生一组相位相差180

°

的pwm信号hd和ld,这组pwm信号经过半桥驱动芯片u2放大驱动能力后直接驱动降压级的功率管n1和n2;同时产生的推挽信号将直接驱动推挽级的功率管n3和n4,通过变压器t2完成功率变换;同时二极管d2将开启,代替集成的高压启动模块开始对芯片的正常供电,过流采样模块也会在此期间开始工作,以保证变换器的安全工作,反馈调节电路也会实时的调控pwm信号的占空比,保持输出电压的稳定。

[0044]

需要说明的是,以上内容仅仅说明了本发明的技术思想,不能以此限定本发明的保护范围,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰均落入本发明权利要求书的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1