用于在数模转换器中降低功率消耗和提高操作频率的方法和装置与流程

1.本公开的各种方面概括而言涉及用于带有效载荷数据的发送波束扫描(transmit beamsweeping)的方法和装置。

背景技术:

2.可以使用射频数模转换器(radio frequency digital-to-analog converter,rfdac)来生成射频(radio frequency,rf)输出信号。rfdac本身是作为通常的射频发送链的替代物存在的,通常的射频发送链包括数模转换器、基带滤波器、上变频混频器和功率放大器。rfdac体系结构使用小型单位单元功率放大器的阵列,这些功率放大器根据数字代码有条件地并联连接。线和列解码器确保正确数目的单位单元(unit-cell)被激活并且其输出功率被组合到匹配网络中。例如,rfdac可以使用极性体系结构或同相和正交(in-phase and quadrature,iq)体系结构。极性rfdac可以使用所有单元来生成输出信号。与iq体系结构相比,极性rfdac可能要求更宽的带宽来传输相同的数据速率。iq发送器阵容具有两个dac,一个用于同相i路径,一个用于正交q路径。iq体系结构可能存在效率更低和输出功率更低的问题。希望提高发送器效率。

附图说明

3.在附图中,相似的附图标记一般在不同的视图中始终指代相同的部件。附图不一定是按比例的,而重点一般是放在图示本发明的原理。在接下来的描述中,参考以下附图描述了本公开的各种方面,其中:

4.图1根据一些方面示出了示例性无线电通信网络。

5.图2根据一些方面示出了终端设备的示例性内部配置。

6.图3根据一些方面示出了被配置用于载波聚合中的动态资源指派的终端设备的示例性内部配置。

7.图4a-4c根据一些方面示出了rfdac的示例性框图。

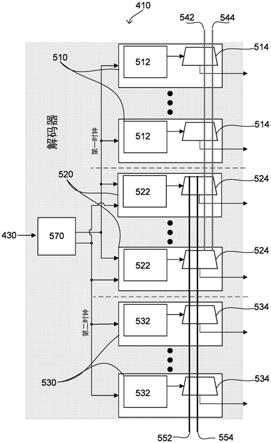

8.图5a-5c根据一些方面示出了解码器的示例性框图。

9.图6a-6b根据一些方面示出了rfdac的示例性可实现值。

10.图7a-7c根据一些方面示出了仿真结果。

11.图8a-8d根据一些方面示出了iq rfdac中的示例性符号切换。

12.图9根据一些方面示出了用于rfdac的方法的示例性流程图。

具体实施方式

13.接下来的详细描述参考了附图,附图以图示方式示出了可实现本发明的具体细节和方面。

[0014]“示例性”一词在本文中用来意指“充当示例、实例或例示”。说明书和权利要求中

rates for gsm evolution,edge)、高速封包接入(high speed packet access,hspa;包括高速下行链路封包接入(high speed downlink packet access,hsdpa)、高速上行链路封包接入(high speed uplink packet access,hsupa)、hsdpa加强版(hsdpa+)、以及hsupa加强版(hsupa+))、微波接入全球互通(worldwide interoperability for microwave access,wimax)、5g新无线电(new radio,nr),以及其他类似的无线电通信技术。蜂窝广域无线电通信技术也包括这种技术的“小型小区”,例如微小区、毫微微小区和微微小区。蜂窝广域无线电通信技术在本文中可被概括称为“蜂窝”通信技术。

[0019]

除非明确指明,否则术语“发送”既涵盖直接发送(点到点)也涵盖间接发送(经由一个或多个中间点)。类似地,术语“接收”既涵盖直接接收也涵盖间接接收。此外,术语“发送”、“接收”、“通信”和其他类似的术语既涵盖物理传输(例如,无线电信号的传输)也涵盖逻辑传输(例如,通过逻辑软件级连接的数字数据的传输)。例如,处理器或控制器可通过软件级连接与另一处理器或控制器以无线电信号的形式发送或接收数据,其中物理发送和接收是由诸如rf收发器和天线之类的无线电层组件处理的,并且通过软件级连接的逻辑发送和接收是由处理器或控制器执行的。

[0020]

图1和图2描绘了用于无线通信的示例性网络和设备体系结构。从图1开始,图1根据一些方面示出了示例性无线电通信网络100,其可包括终端设备102和104以及网络接入节点110和120。无线电通信网络100可经由网络接入节点110和120通过无线电接入网络与终端设备102和104进行通信。虽然本文描述的某些示例可涉及特定的无线电接入网络情境(例如,lte、umts、gsm、其他第3代合作伙伴计划(3rd generation partnership project,3gpp)网络、wlan/wifi、蓝牙、5g nr、mmwave,等等),但这些示例可被应用到任何其他类型或配置的无线电接入网络。无线电通信网络100中的网络接入节点和终端设备的数目是示例性并且可缩放到任何数量。

[0021]

在示例性的蜂窝情境中,网络接入节点110和120可以是基站(例如,enodeb、nodeb、基地收发信台(base transceiver station,bts)、或者任何其他类型的基站),而终端设备102和104可以是蜂窝终端设备(例如,移动台(ms)、用户设备(ue)、或者任何类型的蜂窝终端设备)。网络接入节点110和120因此可与诸如演进型封包核心(epc,用于lte)、核心网络(cn,用于umts)或其他蜂窝核心网络之类的蜂窝核心网络相对接(例如,经由回程接口)。蜂窝核心网络也可被认为是无线电通信网络100的一部分。蜂窝核心网络可与一个或多个外部数据网络相对接。在示例性短程情境中,网络接入节点110和120可以是接入点(ap,例如wlan或wifi ap),而终端设备102和104可以是短程终端设备(例如,台站(sta))。网络接入节点110和120可与一个或多个外部数据网络相对接(例如,经由内部或外部路由器)。

[0022]

网络接入节点110和120可相应地向终端设备102和104(以及可选地,图1中没有明确示出的无线电通信网络100的其他终端设备)提供无线电接入网络。在示例性蜂窝情境中,由网络接入节点110和120提供的无线电接入网络可使得终端设备102和104能够经由无线电通信来无线地接入核心网络。核心网络可以为与终端设备102和104相关的流量数据提供交换、路由和传输。核心网络也可提供对各种内部数据网络(例如,控制节点、在无线电通信网络100上的其他终端设备之间传送信息的路由节点,等等)和外部数据网络(例如,提供语音、文本、多媒体(音频、视频、图像)和其他互联网和应用数据的数据网络)的接入。在示

例性短程情境中,由网络接入节点110和120提供的无线电接入网络可提供对内部数据网络(例如,用于在连接到无线电通信网络100的终端设备之间传送数据)和外部数据网络(例如,提供语音、文本、多媒体(音频、视频、图像)和其他互联网和应用数据的数据网络)的接入。

[0023]

无线电通信网络100的无线电接入网络和核心网络(如果适用的话)可以受通信协议的支配,该通信协议可依据无线电通信网络100的细节而变化。这种通信协议可定义通过无线电通信网络100的用户数据流量和控制数据流量两者的调度、格式化和路由,这包括通过无线电通信网络100的无线电接入网络域和核心网络域两者对这种数据的发送和接收。终端设备102和104以及网络接入节点110和120因此可以遵循定义的通信协议,以通过无线电通信网络100的无线电接入网络发送和接收数据。核心网络可以遵循定义的通信协议,以在核心网络之内和之外路由数据。示例性通信协议包括lte、umts、gsm、wimax、蓝牙、wifi、mmwave等等,其中任何一者都可适用于无线电通信网络100。

[0024]

图2根据一些方面示出了终端设备102的内部配置。如图2所示,终端设备102可包括天线系统202、射频(rf)收发器204、基带调制解调器206(包括数字信号处理器208和协议控制器210)、应用处理器212、以及存储器214。虽然在图2中没有明确示出,但在一些方面中,终端设备102可包括一个或多个额外的硬件和/或软件组件,例如处理器/微处理器、控制器/微控制器、其他专用或通用硬件/处理器/电路、(一个或多个)外围设备、存储器、电力供应源、(一个或多个)外部设备接口、(一个或多个)订户身份模块(subscriber identity module,sim)、用户输入/输出设备((一个或多个)显示器、(一个或多个)小键盘、(一个或多个)触摸屏、(一个或多个)扬声器、(一个或多个)外部按钮、(一个或多个)相机、(一个或多个)麦克风,等等),或者其他相关组件。

[0025]

终端设备102可在一个或多个无线电接入网络上发送和接收无线电信号。基带调制解调器206可以根据与每个无线电接入网络相关联的通信协议来指导终端设备102的这种通信功能。基带调制解调器206从而可以控制天线系统202和rf收发器204根据通信协议的格式化和调度参数来发送和接收无线电信号。在一些方面中,终端设备102被配置为在多种无线电通信技术上操作,终端设备102可包括用于每种支持的无线电通信技术的单独的通信组件(例如,单独的天线、rf收发器、数字信号处理器、以及控制器)。

[0026]

终端设备102可利用天线系统202来发送和接收无线信号,该天线系统202可以是单个天线或者包括多个天线的天线阵列。在一些方面中,天线系统202可额外地包括模拟天线组合和/或波束成形电路。在接收(rx)路径中,rf收发器204可从天线系统202接收模拟射频信号并且对模拟射频信号执行模拟和数字rf前端处理以为基带调制解调器206产生数字基带样本(例如,同相/正交(iq)样本)。rf收发器204可包括模拟和数字接收组件,包括放大器(例如,低噪声放大器(low noise amplifier,lna))、滤波器、rf解调器(例如,rf iq解调器))、以及模数转换器(analog-to-digital converter,adc),rf收发器204可利用其来将接收到的射频信号转换成数字基带样本。在发送(tx)路径中,rf收发器204可从基带调制解调器206接收数字基带样本并且对数字基带样本执行模拟和数字rf前端处理以产生模拟射频信号来供天线系统202无线地发送。rf收发器204可包括射频数模转换器(rfdac),以产生用于无线传输的模拟射频信号,如下文进一步详细描述。或者,rf收发器204可包括模拟和数字发送组件,包括放大器(例如,功率放大器(pa))、滤波器、rf调制器(例如,rf iq调制

器)、以及数模转换器(digital-to-analog converter,dac),rf收发器204可利用其来混合从基带调制解调器206接收的数字基带样本并且产生模拟射频信号以供天线系统202无线发送。在一些方面中,基带调制器206可以控制rf收发器204的无线发送和接收。这可包括指定rf收发器204用来发送或接收的无线电频率。

[0027]

如图2所示,基带调制解调器206可包括数字信号处理器208,它可以执行物理层(phy;层1)发送和接收处理。在发送路径中,数字信号处理器208可以准备传出发送数据(来自协议控制器210)来经由rf收发器204进行发送。在接收路径中,数字信号处理器208可以准备传入接收数据(来自rf收发器204)来由协议控制器210处理。数字信号处理器208可被配置为执行以下各项中的一个或多个:差错检测、前向纠错编码/解码、信道编码和交织、信道调制/解调、物理信道映射、无线电测量和搜索、频率和时间同步、天线分集处理、功率控制和加权、速率匹配/解除匹配、重发处理、干扰消除、以及任何其他物理层处理功能。数字信号处理器208在结构上可实现为硬件组件(例如,实现为一个或多个数字配置的硬件电路或fpga),实现为软件定义的组件(例如,被配置为执行存储在非暂态计算机可读存储介质中的、定义运算、控制和i/o指令(例如,软件和/或固件)的程序代码的一个或多个处理器),或者实现为硬件和软件组件的组合。在一些方面中,数字信号处理器208可包括一个或多个处理器,该一个或多个处理器被配置为取回和执行定义用于物理层处理操作的控制和处理逻辑的程序代码。在一些方面中,数字信号处理器208可经由对可执行指令的执行来利用软件执行处理功能。在一些方面中,数字信号处理器208可包括一个或多个专用硬件电路(例如,asic、fpga和其他硬件),该一个或多个专用硬件电路被数字地配置为具体执行处理功能。数字信号处理器208的一个或多个处理器可将某些处理任务负载转移到这些专用硬件电路,这些专用硬件电路被称为硬件加速器。示例性硬件加速器可包括快速傅立叶变换(fast fourier transform,fft)电路和编码器/解码器电路。在一些方面中,数字信号处理器208的处理器和硬件加速器组件可被实现为耦合的集成电路。

[0028]

终端设备102可被配置为根据一个或多个无线电通信技术来进行操作。数字信号处理器208可负责无线电通信技术的下层处理功能(例如,层1/phy),而协议控制器210可负责上层协议栈功能(例如,数据链路层/层2和/或网络层/层3)。协议控制器210从而可负责根据每种支持的无线电通信技术的通信协议来控制终端设备102的无线电通信组件(天线系统202、rf收发器204以及数字信号处理器208)。在一些方面中,协议控制器210可以代表每种支持的无线电通信技术的接入层面和非接入层面(non-access stratum,nas)(也涵盖层2和层3)。协议控制器210在结构上可实现为协议处理器,该协议处理器被配置为执行协议栈软件(从控制器存储器取回)并且随后控制终端设备102的无线电通信组件来根据协议软件中的协议栈控制逻辑来发送和接收通信信号。协议控制器210可包括被配置为取回和执行程序代码的一个或多个处理器,所述程序代码为一个或多个无线电通信技术定义上层协议栈逻辑,这可包括数据链路层/层2和网络层/层3功能。协议控制器210可被配置为执行用户平面功能和控制平面功能两者来利用支持的无线电通信技术的特定协议向和从无线电终端设备102传送应用层数据。用户平面功能可包括头部压缩和封装、安全性、差错检查和校正、信道复用、调度和优先级,而控制平面功能可包括无线电承载的建立和维护。由协议控制器210取回和执行的程序代码可包括定义这种功能的逻辑的可执行指令。

[0029]

终端设备102还可包括应用处理器212和存储器214。应用处理器212可以是cpu,该

cpu被配置为处理高于协议栈的层,包括传输层和应用层。应用处理器212可被配置为在终端设备102的应用层执行终端设备102的各种应用和/或程序。这些应用和/或程序可包括操作系统(operating system,os)、用于支持用户与终端设备102的交互的用户界面(user interface,ui)、和/或各种用户应用。应用处理器可与基带调制解调器206相对接并且充当诸如语音数据、音频/视频/图像数据、消息传递数据、应用数据、基本互联网/web访问数据等等之类的用户数据的信源(在发送路径中)和信宿(在接收路径中)。在发送路径中,协议控制器210可根据协议栈的层特定功能来接收和处理由应用处理器212提供的传出数据,并且将得到的数据提供给数字信号处理器208。数字信号处理器208随后可对接收到的数据执行物理层处理以产生数字基带样本,数字信号处理器可将这些数字基带样本提供给rf收发器204。rf收发器204随后可处理数字基带样本以将数字基带样本转换成模拟rf信号,rf收发器204可经由天线系统202无线地发送这些模拟rf信号。在接收路径中,rf收发器204可从天线系统202接收模拟rf信号并且处理模拟rf信号以获得数字基带样本。rf收发器204可将数字基带样本提供到数字信号处理器208,数字信号处理器208可对数字基带样本执行物理层处理。数字信号处理器208随后可将得到的数据提供给协议控制器210,协议控制器210可根据协议栈的层特定功能来处理得到的数据并且将得到的传入数据提供给应用处理器212。应用处理器212随后可在应用层处理传入数据,这可包括利用该数据执行一个或多个应用程序和/或将该数据经由用户界面呈现给用户。

[0030]

存储器214可实现终端设备102的存储器组件,例如硬盘驱动器或者另外的这种永久存储器设备。虽然在图2中没有明确描绘,但图2所示的终端设备102的各种其他组件还可各自包括集成的永久和非永久存储器组件,例如用于存储软件程序代码、缓冲数据,等等。

[0031]

根据一些无线电通信网络,终端设备102和104可执行移动性过程以连接到无线电通信网络100的无线电接入网络的网络接入节点、与这些网络接入节点断开连接、以及在这些网络接入节点之间切换。由于无线电通信网络100的每个网络接入节点可具有各自的覆盖区域,所以终端设备102和104可被配置为在可用的网络接入节点之间进行选择和重选择,以与无线电通信网络100的无线电接入网络维持强无线电链路。例如,终端设备102可与网络接入节点110建立无线电链路,而终端设备104可与网络接入节点112建立无线电链路。在当前无线电链路劣化的情况下,终端设备102或104可寻求与无线电通信网络100的另一网络接入节点的新无线电链路。例如,终端设备104可从网络接入节点112的覆盖区域移动到网络接入节点110的覆盖区域中。结果,与网络接入节点112的无线电链路可能劣化。终端设备104可以通过无线电测量,例如网络接入节点112的信号强度或信号质量测量,来检测该劣化。取决于无线电通信网络100的适当网络协议中定义的移动性过程,终端设备104可寻求新的无线电链路(其例如可以在终端设备104处触发或者由无线电接入网络触发)。在一些情况下,终端设备104可以通过对邻近的网络接入节点执行无线电测量来搜索新的无线电链路,以确定任何邻近的网络接入节点是否能够提供适当的无线电链路。由于终端设备104可能已移动到网络接入节点110的覆盖区域中,所以终端设备104可识别网络接入节点110(这可由终端设备104选择或者由无线电接入网络选择)并且转移到与网络接入节点110的新无线电链路。在各种网络协议中定义了这些移动性过程,包括无线电测量、小区选择/重选择以及切换。

[0032]

图3根据一些方面示出了终端设备102的示例性内部配置。终端设备102可被配置

为执行本公开的资源指派技术。如图2所示,终端设备102可包括天线系统202、rf收发器204、以及基带调制解调器206,它们可如上文对于图2所描述那样被配置。在图3的示例中,天线系统202被示为有四个天线。从而,在接收方向上,天线系统202可能够针对每个载波支持多达四层。在其他示例中,天线的数目、载波的天线数据流的数目numrx、以及最大层数可缩放到任何数量。

[0033]

在图3所示的配置中,终端设备102还可包括数据总线302、控制器304、估计处理器306、测量引擎308、以及转换器320。数据总线302可以是一组数据线,该组数据线将rf收发器204与基带调制解调器206相对接。数据总线302可具有有限的容量。例如,数据总线302可能只能够将最大量的数据从rf收发器204路由到基带调制解调器206。这可能限制了rf收发器204能够递送到基带调制解调器206的、来自天线系统202的支持数据流的总数。在一些方面中,rf收发器204的硬件能力也可能限制支持的天线数据流的这个总数。例如,rf收发器204的硬件设计(例如,复用器或模拟电路组件)可能只能够支持所支持的天线数据流的总数。

[0034]

如上文对于图2所描述,终端设备102的基带调制解调器206可包括物理层子组件(dsp 208)和协议栈子组件(协议处理器210)。基带调制解调器206的子组件可以是那些物理层子组件(dsp 208)和/或那些协议栈子组件(协议处理器210)的一部分;换句话说,图3所示的子组件不限于是物理层或协议栈层组件。基带调制解调器206的控制器304可以是被配置为管理载波聚合并且将设备处理资源指派给载波的控制器。在一些方面中,控制器304可以是协议栈层组件,例如协议处理器210的一部分,或者可以是物理层组件,例如数字信号处理器208的一部分。估计处理器306可以是被配置为确定对各种设备处理资源的吞吐量增益和功率惩罚的估计的处理器。在下文中针对图4对这些操作进行了全面描述。在一些方面中,估计处理器306可以是协议栈层组件,例如协议处理器210的一部分,或者可以是物理层组件,例如数字信号处理器208的一部分。

[0035]

测量引擎308可以是被配置为执行信道测量的电路。在一些方面中,测量引擎308可包括数字硬件电路(例如,asic),其配置为处理数字数据以确定信道测量。在一些方面中,测量引擎308可以额外地或者替换地包括一个或多个处理器,该处理器被配置为执行处理数字数据以确定信道测量的软件。在一些方面中,测量引擎308可以是基带调制解调器206的物理层的一部分,例如dsp 208的一部分。

[0036]

转换器320可以是射频数模转换器。rfdac体系结构使用小型单位单元功率放大器的阵列,这些功率放大器根据数字代码有条件地并联连接。线和列解码器确保了正确数目的单位单元被激活并且其输出功率被组合到匹配网络中。

[0037]

图4a描绘了示例性rfdac。射频数模转换器(rfdac)本身是作为通常的射频发送链的替代物存在的,通常的射频发送链包括数模转换器、基带滤波器、上变频混频器和功率放大器。如图4a中所示,转换器320可包括单位单元功率放大器阵列480、数字解码器410(有时被称为列解码器)、第一相位分量线解码器420、第二相位分量线解码器422、以及匹配网络440。转换器接收数字信号430和本地振荡器信号432,并且产生射频信号450。转换器320的体系结构使用小型单位单元功率放大器的阵列480,这些功率放大器根据数字代码字有条件地并联连接。线解码器420和422与数字解码器410一起确保阵列480的正确数目的单位单元放大器被激活,并且确保它们的输出功率被组合到匹配网络440中。

[0038]

例如,列解码器410输出时钟,其中相位取决于输入代码和符号。此外,解码器410输出使能信号,以使能阵列480的单位单元,其中使能信号取决于输入代码和符号。

[0039]

示例性阵列480可以利用差分(differential)单位单元。差分单位单元被配置为接收时钟分量和180度时钟。此外,可以实现单位单元的列的另一个使能信号以激活单位单元。

[0040]

图4b描绘了转换器320作为示例性i/q rfdac。应当注意,该配置也适用于多相位rfdac。如图4b中所示,转换器320还可包括第一相位分量本地振荡器缓冲器414、第二相位分量本地振荡器缓冲器416,它们分别接收第一相位分量本地振荡器信号434、第二相位分量本地振荡器信号436。此外,第一相位分量线解码器420和第二相位分量线解码器422确定是否要激活阵列480的单位单元功率放大器,如箭头402和404分别描绘的。应当注意,在极性rfdac配置中,将不需要第二相位分量线解码器422和第二相位分量本地振荡器缓冲器416。

[0041]

rfdac的拓扑结构可被细分为两个类别。第一类是极性,其中有源功率放大器单位单元的数量决定了幅度,并且相位由本地振荡器定义。第二类是i/q笛卡尔,其中同相(i)和正交(q)的正交分量的向量相加决定了幅度和相位。由于执行了向量加法,因此对于相同数目的单位单元,与极性拓扑结构相比,对于i/q笛卡尔拓扑结构,iq-rfdac可以提供更少的输出功率。然而,极性rfdac具有如下缺点:幅度和相位谱要求的带宽大于基带信号,从而其应用通常限于窄带信号。宽带现代长期演进(lte)和新无线电(nr)发送器更可能应用iq-rfdac拓扑结构。

[0042]

如图4b中所描绘的,阵列480中的i/q rfdac的单位单元放大器具有在第一相位分量(例如,i时钟分量)或第二相位分量(例如,q时钟分量)中操作的能力。因此,如图4b中所示,两个时钟分量都可以被分发到所有的列。列解码器410基于i/q输入数字代码430来决定阵列480的每个个体行是否将接收i时钟分量或q时钟分量,或者其时钟是否应当被停用(deactivate)。线解码器424和426进而决定由列切片激活的阵列480的行中的单位单元放大器是否应被激活或停用。因此,如箭头402和404所示,每个线控制信号必须被路由通过阵列480的行中的每个单位单元放大器。

[0043]

这种实现方式要求在数字解码器410内部存在一种有挑战性的解码过程。为了到达阵列480的所有行并且执行从二进制到测温码(thermometric code)的转换,控制信号必须在布局中覆盖大的物理距离。因为这一点,解码器410的内部逻辑门应具有非常大的扇出,以便将决定时钟的激活和极性所需的信号分发在阵列480的每一行中。此外,每个解码和激活过程中都必须涉及i和q时钟分量两者的数字代码,从而增大了复杂性和组合逻辑深度。rfdac不断增长的操作频率对信号施加了非常有限的传播时间。这是以额外的电流和硅片面积为代价的。

[0044]

这种解决方案的第二个缺点存在于线解码器424和426的输出级以及lo缓冲器414和416,它们要求大的扇出以到达所有的单位单元放大器。如箭头402和404所示,线解码器424和426必须驱动整个阵列480的单元。再一次,这引入了两个缺点。第一,这要求线的大扇出。第二,需要覆盖大的物理距离,从而引入了大量的寄生。因此,输出门必须非常大,以便能够驱动大的负载,并且导致大的功率消耗。

[0045]

此外,在大多数应用中,单位单元功率放大器阵列480应具有单独的电源域。这样

做是为了依据输出功率要求来优化电源电压。在这种情况下,来自线解码器424和426的线控制信号的切换在电源域上注入电荷,导致了串扰,这提高了频谱噪声水平。呈现给线解码器424和426的输出级的负载越高,电荷注入就越大。

[0046]

图4c描绘了示例性rfdac,它减少了需要由多个时钟分量激活的个体单位单元放大器。在各种方面中,描述了对于射频数模转换器(rfdac)320内的单位单元功率放大器阵列480的覆盖的减少。通过减少每个块组件所覆盖的单位单元功率放大器的数量,可以减少功率消耗。此外,逻辑门可以被简化,并且这些修改不会导致信号质量的任何缺点。

[0047]

例如,在iq-rfdac的情况下,如果阵列480的单位单元功率放大器中只有(1/√2)

×

100%将会可用于两相位时钟的每个分量,则可以减少功率消耗,而不影响输出信号质量。通过减少每个相位分量可用的功率放大器的数量,由线解码器424和426分发的线控制信号、缓冲的逻辑振荡器(lo)信号和解码信号不需要到达阵列480的每个单位单元功率放大器。

[0048]

作为另一个示例,在多相位rfdac的情况下,如果阵列480的单位单元功率放大器中只有cos(δφ/2)xl00%将会可用于多相位时钟的每个分量,则可以减少功率消耗,而不影响输出信号质量。通过减少每个相位分量可用的功率放大器的数量,由线解码器424和426分发的线控制信号、逻辑振荡器(lo)缓冲器信号和解码信号不需要到达阵列480的每个单位单元功率放大器。

[0049]

所要求的到达的减少导致了更低的功率消耗,这与驱动的电容成正比,从而减少了扇出和驱动线大小。例如,线解码器424和426可能只需要将线控制信号分发给阵列480的、如箭头408和406所描绘的行中的一部分。鉴于输出缓冲器处于lo缓冲器414和416对线解码器424和426的功率消耗贡献中,减少它们的功率消耗相当于rfdac 320总功率消耗的一个重大部分。解码器410处的逻辑简化将减少传播时间,使得能够实现更高的操作频率。作为副作用,跨电力域注入的电荷减少了,有可能导致更低的串扰和噪声。带有解码器410的简化逻辑也允许了更紧凑的布局,因此减小了硅面积。

[0050]

减少的单位单元功率放大器阵列480使用方案的一些方面也可能允许轻松实现低功率操作模式。因此,使一些lo和线控制路由资源成为不必要的,而是可改为用于在输出功率有限的情况下路由单独的lo和线控制信号。

[0051]

在时钟分量之间的90度相位差中,例如iq-rfdac,可以减少阵列480中的单元的覆盖,从而对于每个分量只要求单位单元功率放大器的(1/√2)

×

100%。例如,阵列480的区域464只关注第一时钟分量,并且阵列480的区域466只关注第二时钟分量。阵列480的其余部分可以作为第一时钟分量或第二时钟分量被激活。例如,在iq rfdac的情况下,同时作为i或q。取决于阵列480中实现的行和列的数目,可以非常接近(1/√2)

×

100%的值。例如,如果阵列480被划分为四个部分,则区域464和466都可以是阵列480的25%,并且只分别作为第一时钟分量或第二时钟分量被激活,留下阵列480的另外50%作为第一时钟分量或第二时钟分量被激活。这确保了至少(1/√2)

×

100%的单位单元功率放大器能够针对每个时钟分量被激活。例如,在iq rfdac中,阵列的25%将能够专门作为i分量被激活,阵列的25%将能够专门作为q分量被激活。在这种情况下,阵列的50%将能够作为i和q分量两者被激活。这将允许阵列的75%作为i或q时钟分量来操作。并非所有的单位单元功率放大器都能够作为两个分量来操作。如图4c所描绘的,阵列的一部分专门用于i时钟分量或q时钟分量。因

此,线控制信号406和408、解码器410内部的缓冲lo信号、以及来自数字代码430的解码信号只必须达到其当前阵列480范围的大约(1/√2)

×

100%。已证明,对于正常的lte和nr信号,这种修改并不意味着在信号质量或其他方面有任何缺点,并且使得能够实现大规模的逻辑减少和简化。

[0052]

应当注意,在多相位rfdac中,可能要求针对每个分量的单位单元的cos(δφ/2)xl00%覆盖。

[0053]

如图4c中所示的单位单元阵列使用,对每个信号相位分量使用减少的单位单元覆盖范围。例如,iq rfdac中的i分量或q分量。作为说明,选择可被4除尽的数字,从而选择75%覆盖,因为它是与(1/√2)

×

100%覆盖的值最接近并且大于该值的整数。因此,底部的25%的单位单元被专门保留给第二时钟分量,例如i分量,并且顶部的25%被专门保留给第一时钟分量,例如q分量。因此,线控制信号和缓冲lo只必须到达阵列的75%,从而提供更低的扇出、更短的物理线和更简单的组合逻辑。

[0054]

图6a描绘了被显示为630a的原本可实现值。这种修改转化为可实现值的减少的星座,这被显示为两相位时钟的线640a。注意,可实现值足以覆盖由对于所有信号相位可实现的最大输出功率所限制的值的圈子。

[0055]

图5a进一步详细描绘了示例性解码器410。如上文关于图4a-4c的描述,解码器410根据不同的时钟分量控制阵列480的行的激活。图5a描绘了用于解码两相位时钟(例如iq时钟)的示例性解码器。解码器410通过接口寄存器570接收数字信号430。接口寄存器570将第一分量的数字信号分发给列切片510和时钟列切片520。接口寄存器570将第二分量的数字信号分发给时钟列切片520和列切片530。时钟分量切片520接收两个时钟分量,而分量切片510和530分别只接收第一时钟分量和第二时钟分量。

[0056]

时钟分量切片510、520和530可分别包括组合逻辑512、522和532并且分别包括复用器(mux)514、524和534。此外,分量切片从lo振荡器缓冲器414和416(见图4b)接收时钟542、544、552和554。

[0057]

列切片510、520和530可被配置为针对阵列480中的每一行输出使能信号和时钟。尽管名称是“列”,但每个切片控制着行,如图4a-4c中所描绘的。例如,如果阵列480是32乘16的阵列,则它将有32个列切片来控制阵列480中的32行中的每一行。可以实现一种示例性rfdac,其中线解码器如图4a-4c所示控制列或者控制行(未描绘)。同样地,列切片可能被配置为如图4a-4c所示控制行或者控制列(未描绘)。术语“列”是观点问题,而不应当被解释为限制性的。

[0058]

示例性列解码器可包括列切片510、520和530,它们可被配置为在差分时钟的情况下输出四个使能信号和两个时钟信号。单位单元是否被使能取决于列切片的使能信号和线解码器424和426的线控制信号的组合。如果单位单元被使能,则它将与通过列切片接收的时钟同相输出。时钟输出是由lo复用器514、524和534定义的。注意以下这点是重要的:列解码器输出一个时钟,其中相位取决于输入代码和符号,并且选择信号来使能单位单元(也取决于输入代码和符号)。

[0059]

组合逻辑512和532被配置为威胁符号变化和时钟分量。例如,组合逻辑512是针对符号变化和第一时钟分量来配置的,并且组合逻辑532是针对符号变化和第二时钟分量来配置的。而组合逻辑522被配置为威胁第一时钟分量和第二时钟分量。

[0060]

lo复用器(mux)514、524和534分别从组合逻辑512、522和532接收输入。阵列480的单位单元由如下项来激活:单位单元从lo复用器(mux)514、524和534接收的使能信号;以及从线解码器424和426接收的、由箭头402和404表示的线控制信号。如果一列单位单元处于活跃,它就会根据来自lo mux 514、524和534的输出接收正确的时钟。

[0061]

符号542表示第一时钟分量的正号,544表示第一时钟分量的负号,552表示第二时钟分量的正号,并且554表示第二时钟分量的负号。

[0062]

mux 514和524接收第一时钟分量的时钟符号,并且mux 524和534接收第二时钟分量的时钟符号。

[0063]

作为支持符号变化的iq-rfdac的示例,如图5a所示,阵列480中支持第一时钟分量和第二时钟分量两者的激活的行(由分量切片520激活的那些)必须不支持符号变化。阵列480中只支持第一时钟分量的激活(由分量切片510激活的那些)和只支持第二时钟分量的激活(由分量切片530激活的那些)的行必须只支持符号变化。

[0064]

例如,在iq-rfdac中,分量切片510将只关注i相位时钟分量,分量切片520将关注i相位时钟分量和q相位时钟分量两者,并且分量切片530将只关注q相位时钟分量。为了实现上文描述的(1/√2)

×

100%覆盖,分量切片510可以覆盖阵列480中的25%的行,分量切片520可以覆盖阵列480中的50%的行,并且分量切片530可以覆盖阵列480中的25%的行。由于激活控制信号与lo的同步,符号变化在iq-rfdac中通常具有挑战性。适当的符号变化逻辑实现要求相对复杂的逻辑。通过不必同时处理符号变化和数字信号的两个时钟分量,逻辑可以被简化,这进而又有利于更高的操作频率。事实上,对于大得多的相对带宽,一些分量切片将需要支持符号变化以及两个信号分量。

[0065]

可以按许多方式来处理符号切换。作为示例,在iq rfdac中,符号切换与rfdac阵列电路中的i相位输入数据相关联。在一些方面中,如图8a所示,在常规操作期间,从左到右填充i相位片段。在这种情况下,阵列480的最左侧i相位片段802a(根据i相位分量激活的单位单元功率放大器)被用作i相位符号变化片段。然而,在其他方面中,i相位符号变化片段可包括rfdac的阵列内的、与i相位片段的集合和q相位片段的集合不同的任何单位单元功率放大器。为了利用最左侧片段802a作为i相位符号变化片段,rfdac阵列电路800被配置为在符号变化之前的lo时段期间以这样一种方式移动i相位片段的集合:在符号变化之前,最左侧片段802a是空的,如图8b所示。另外,在符号变化之后的lo时段的前半部804期间,部分活跃片段802b被停用,并且i相位符号变化片段802a被激活以处理符号变化。另外,在符号变化之后的lo时段的后半部806期间,i相位符号变化片段802a被停用,并且部分活跃片段802b被重新激活,如图8c所示。此外,在符号变化之后的后续lo时段之后,i相位片段的集合被移回到原始位置,如图8d所示。上述实现方式只是一种可能的实现方式,而不应被理解为是限制性的。在其他方面中,可以在不移动i相位片段的集合的情况下,基于利用任何可用片段(i相位或q相位)处理符号变化,来实现符号切换。

[0066]

图5b描绘了一种示例性解码器,该解码器通过允许纳入低功率控制信号而扩展了关于图5a介绍的益处,低功率控制信号438被接口寄存器570接收。此外,接收信号符号542、544、552和554的分量切片可以只被保留给高功率。来自lo振荡器缓冲器414和416的信号符号546、548、556和558可以只被保留给低功率信号符号。

[0067]

例如,信号符号542表示第一时钟分量的高功率正号,544表示第一时钟分量的高

功率负号,552表示第二时钟分量的高功率正号,并且554表示第二时钟分量的高功率负号。

[0068]

此外,信号符号546表示第一时钟分量的低功率正号,548表示第一时钟分量的低功率负号,556表示第二时钟分量的低功率正号,并且558表示第二时钟分量的低功率负号。如图所示,低功率信号符号必须只被路由到关注符号变化的分量切片,即,对于第一时钟分量是512,对于第二时钟分量是532。

[0069]

例如,iq rfdac可以如图5b中描绘的那样来实现。这扩展了图4c中描述的单位单元阵列使用的益处。以这种方式,可以使用先前用于为其各自的本地振荡器路由两个时钟分量的面积和金属来实现专用的低功率振荡器信号。换句话说,先前用于将第一时钟分量的分量信号从第一时钟的本地振荡器路由到专用于第二时钟分量的分量切片的面积和金属可被用于低功率信号。例如,由于信号符号552和554只从用于第二时钟分量的本地振荡器缓冲器416被路由到分量切片530和520,所以先前用于将信号符号552和554路由到分量切片510的资源可被用于将低功率信号546和548从用于第一时钟分量的本地振荡器缓冲器414路由到分量切片510。从而,可以实现专用的低功率(lp)本地振荡器信号546、548、556和558。只要增加很少的组合逻辑,在要求的输出功率较低的情况下,只有专门为一个分量服务的列会被激活。因此,lp lo可以被从缓冲器414和416路由,强度降低并且消耗的功率也少得多。类似的策略可被应用于线解码器,以使用功率消耗更少的输出缓冲器来驱动减少的控制线。在本公开的示例实现方式中,如果预期调制信号具有低于iq-rfdac所支持的最大值的峰值输出功率dbb,则除了通过高功率(hp)模式以外,也可以通过低功率模式提供信号,每个分量只用25%的行来实现。

[0070]

图5c描绘了具有逻辑rfdac的示例性解码器410。如上所述,有可能实现解码器来处理多于两个时钟分量。图5c示出了使用这一概念和减小的阵列范围的解码器的一种可能实现方式。多相位时钟生成器590将为相位选择器592提供所有相位,相位选择器592将把2个相邻的相位(这里命名为φk和φk+l)传递给列切片510、520和530。

[0071]

相位选择器592也被提供了相位选择比特594,并且将本地振荡器信号φk 596和本地振荡器信号φk+1 598分别提供给本地振荡器缓冲器582和584。

[0072]

例如,在包括512个单位单元功率放大器的阵列480中的60

°

相位步长的情况下,每个分量的单位单元功率放大器的最小数目是444。假设具有32行和16列的阵列480。在这种情况下,32行中有28行(阵列的87.5%)必须要被每个相位分量所覆盖。从而,4行对于低功率模式将专门在φk分量上操作,4行对于低功率模式将专门在φk+l分量上操作,并且24行将在φk分量和φk+1分量两者上操作。

[0073]

在另一示例中,在包括512个单位单元功率放大器的阵列480中的45

°

相位步长的情况下,每个分量的单位单元的最小数目是474。假设具有32行和16列的阵列480。在这种情况下,32行中有30行(阵列的93.75%)必须要被每个相位分量所覆盖。从而,2行对于低功率模式将专门在φk分量上操作,2列对于低功率模式将专门在φk+l分量上操作,并且28列被φk分量和φk+1分量两者所共享。

[0074]

相位数目越高,使用图5c中描绘的实施例,专门用一个相位分量操作的行就越少。该实现方式将对lo缓冲器582和584产生较小的负载,从而产生对功率消耗和面积的节省。

[0075]

作为示例,如果使用小于60

°

的相位步长,则就有可能生成与相位分量覆盖无关的低功率控制信号。

[0076]

图6a描绘了rfdac中的示例性可实现值。例如,在阵列480中具有n个单位单元功率放大器的iq-rfdac中。可实现值630a对应于图4b中描绘的实现方式。在这样的实现方式中,所有单位单元都是可以在两个信号相位分量之间共享的。单元和列的离散性被忽略了。最大输出功率范围620a指示出对于所有信号相位可以获得的最大输出功率。该约束来自于这样的情况:如610a所示,一半的单位单元(n/2)进行操作来为q分量服务,另一半进行操作来为i分量服务。对于任何两相位rfdac而言都是如此。将值削剪(clip)到对于所有相位可实现的最大输出功率是发送器中进行的通常操作,并且它有助于降低信号峰均功率比(peak-to-average power ratio,papr)并且避免通过放大器的非线性造成的信号失真。这种限制进而导致,对于相同数目的单元并且考虑到经调制的信号,iq-rfdac可以提供比其极性对应物低3db的峰值输出功率。极性rfdac可以使用整个阵列来向信号提供所有可能的相位。

[0077]

应当注意,最大输出功率620a不受两个时钟分量在单位单元功率放大器阵列480上的覆盖减少的影响,如图6a中的610a和640a所描绘的。

[0078]

该解释与转换器的类型无关。例如,它可以适用于开关电容器rfdac,并且可能适用于未来体系结构的rfdac。然而,应当提到的是,有可能向一些rfdac添加更多的单位单元功率放大器,以提高输出功率,而在开关电容器rfdac中,添加单元通常无助于更高的输出功率。

[0079]

图6b描绘了多相位转换器的示例性可实现值。每个分量的单位单元的最大数目被限制到cos(δφ/2)*n,图示为圆圈620b。其中δφ是多相位rfdac中的相邻相位之间的差异。

[0080]

与两相位iq rfdac一样,630b表示在整个阵列480可以按照两个时钟分量被激活的情况下的可能的可实现值。640b示出了阵列中的覆盖的可能限制。对cos(δφ/2)*n进行上舍入得出每个分量的单位单元的最小必要数目。对于每个时钟相位分量需要考虑的单位单元功率放大器的数目的绝对最小限制。

[0081]

通过使用此实现方式的各种标准测试信号进行的系统仿真验证,已经得到确认。例如,图7a、7b和7c示出了rfdac的仿真结果。黑点730a、730b和730c图示了硬削之后输入到rfdac的代码,以逼近所有信号相位的最大功率幅度620a的圆圈。可以注意到,输入代码逼近八边形,因为输入值是有限的,以至于阵列的行或列中的所有单元都在单个信号分量下操作。细的虚线图示了列实现方式。菱形的粗虚线表示先前由阵列中的总单位单元数目施加的限制。菱形和方形粗虚线之间的交点考虑了新的单位单元阵列使用方案的限制,其中每个分量被限制到阵列的75%。

[0082]

图7a、7b和7c示出了lte和nr频段的三种所标识的关键情况。图7a和7b图示了具有更高的相对带宽的nr和lte情况,并且图7c图示了在6ghz以下频段具有最高lo频率和更宽带宽的情况。所有的仿真都考虑了完全资源块(resource block,rb)分配。lte信号是使用单载波频分多址接入(single-carrier frequency-division multiple access,sc-fdma)的正交相移键控(quadrature phase shift keying,qpsk)调制的。nr信号是使用循环前缀正交频分复用(cyclic-prefix orthogonal frequency division multiplexing,cp-ofdm)的64正交幅度调制(quadrature amplitude modulated,qam)的。还图示了经过削剪、滤波所获得的信号谱和类似八边形的值星座。

[0083]

在图7a、7b和7c中,对于每个时钟分量,先前或随后输入代码具有不同符号的值被

标记为710a、720a、710b、720b、710c和720c。在该示例中,iq rfdac的i和q分量。i分量由720a、720b和720c表示,而q分量分别由710a、710b、720b、710c和710c表示。从而,在符号变化过程中涉及的代码被强调了。值得注意的是,阴影区域(710a、720a、710b、720b、710c和720c)被限制在远少于25%的列。

[0084]

图9示出了控制rfdac的方法的示例性方法900。如图9所示,方法900包括:控制阵列的第一多个单位单元功率放大器来按照第一时钟操作(902),控制阵列的第二多个单位单元功率放大器来按照第二时钟操作(904),控制阵列的第三多个单位单元功率放大器来按照第一时钟或第二时钟操作(906),将第一时钟的符号输出到第一多个单位单元功率放大器(908),将第二时钟的符号输出到第二多个单位单元功率放大器(910),并且为第三多个单位单元功率放大器区分第一时钟和第二时钟(912)。

[0085]

虽然上面的描述和联系的附图可将电子设备组件描绘为分开的元素,但本领域技术人员将会明白将离散的元素组合或集成到单个元素中的各种可能性。这可包括组合两个或更多个电路以形成单个电路,将两个或更多个电路安装到共同的芯片或机壳上以形成集成元素,在共同的处理器核心上执行离散的软件组件,等等。相反,本领域技术人员将会认识到将单个元素分离成两个或更多个离散元素的可能性,例如将单个电路分割成两个或更多个分开的电路,将芯片或机壳分离成原本在其上提供的离散元素,将软件组件分离成两个或更多个部分并且在单独的处理器核心上执行每个部分,等等。

[0086]

要明白,本文详述的方法的实现方式是演示性的,从而被理解为能够在相应的设备中实现。类似地,要明白,本文详述的设备的实现方式被理解为能够被实现为相应的方法。从而要理解,与本文详述的方法相对应的设备可包括被配置为执行相关方法的每个方面的一个或多个组件。

[0087]

以上描述中定义的所有缩写在这里包括的所有权利要求中也成立。

[0088]

接下来的示例公开了本公开的各种方面:

[0089]

示例1是一种射频转换器,该射频转换器包括单位单元功率放大器的阵列,其中,所述单位单元功率放大器的阵列包括第一多个单位单元功率放大器、第二多个单位单元功率放大器、以及第三多个单位单元功率放大器;其中,所述第一多个单位单元功率放大器被配置为按照第一时钟操作;其中,所述第二多个单位单元功率放大器被配置为按照第二时钟操作;其中,所述第三多个单位单元功率放大器被配置为按照所述第一时钟或所述第二时钟操作;以及解码器,被配置为:为所述第一多个单位单元功率放大器输出所述第一时钟和所述第一时钟的使能信号;为所述第二多个单位单元功率放大器输出所述第二时钟和所述第二时钟的使能信号;为所述第三多个单位单元功率放大器区分所述第一时钟和所述第二时钟。

[0090]

在示例2中,如示例1所述的主题可以可选地还包括所述解码器被配置为接收低功率控制信号。

[0091]

在示例3中,如示例1或2所述的主题可以可选地还包括所述解码器包括多个接口寄存器。

[0092]

在示例4中,如示例1至3中的任何一项所述的主题,可以可选地还包括所述解码器包括用于所述第一多个单位单元功率放大器的第一组合逻辑,用于所述第二多个单位单元功率放大器的第二组合逻辑,以及用于所述第三多个单位单元功率放大器的第三组合逻

辑。

[0093]

在示例5中,如示例1至4中的任何一项所述的主题,可以可选地还包括接口寄存器,其被配置为接收所述低功率控制信号并且将所述低功率控制信号路由到所述第一组合逻辑或所述第二组合逻辑。

[0094]

在示例6中,如示例1至5中的任何一项所述的主题,可以可选地还包括其中,所述解码器包括第一本地振荡器缓冲器和第二本地振荡器缓冲器。

[0095]

在示例7中,如示例1至6中的任何一项所述的主题可以可选地还包括第一线解码器和第二线解码器。

[0096]

在示例8中,如示例1至7中的任何一项所述的主题,可以可选地还包括其中,所述第一线解码器被配置为:接收来自所述第一本地振荡器的信号;基于来自所述第一本地振荡器的信号而激活所述第一多个单位单元功率放大器或所述第三多个单位单元功率放大器中的任何单位单元功率放大器;并且其中,所述第二线解码器被配置为:接收来自所述第二本地振荡器的信号;基于来自所述第二本地振荡器的信号而激活所述第二多个单位单元功率放大器或所述第三多个单位单元功率放大器中的任何单位单元功率放大器。

[0097]

在示例9中,如示例1至8中的任何一项所述的主题,可以可选地还包括其中,所述解码器还被配置为:接收数字信号;基于所述数字信号根据第一时钟激活所述第一多个单位单元功率放大器或所述第三多个单位单元功率放大器中的一行单位单元功率放大器;并且基于所述数字信号根据第二时钟激活所述第二多个单位单元功率放大器或所述第三多个单位单元功率放大器中的一行单位单元功率放大器。

[0098]

在示例10中,如示例1至9中的任何一项所述的主题,可以可选地还包括其中,所述解码器还包括相位选择器。

[0099]

在示例11中,如示例1至10中的任何一项所述的主题,可以可选地还包括其中,所述相位选择器还被配置为:接收多个时钟相位;接收多个数字信号;接收相位选择比特;基于所述多个时钟相位中的至少一者为所述第一时钟产生第一本地振荡器信号;并且基于所述多个时钟相位中的至少一者为所述第二时钟产生第二本地振荡器信号。

[0100]

在示例12中,如示例1至11中的任何一项所述的主题,可以可选地还包括其中,所述第一本地振荡器信号和所述第二本地振荡器信号表示相邻的相位。

[0101]

在示例13中,如示例1至12中的任何一项所述的主题,可以可选地还包括其中,所述第一振荡器信号被路由到第一本地振荡器缓冲器;并且所述第二振荡器信号被路由到第二本地振荡器缓冲器。

[0102]

在示例14中,如示例1至13中的任何一项所述的主题,可以可选地还包括其中,所述第一多个单位单元功率放大器部分地基于所述第一时钟的符号被激活;并且所述第二多个单位单元功率放大器部分地基于所述第二时钟的符号被激活。

[0103]

在示例15中,如示例1至14中的任何一项所述的主题,可以可选地还包括第一多个复用器,第二多个复用器,以及第三多个复用器;其中,所述第一多个复用器被配置为激活所述第一多个单位单元功率放大器;其中,所述第二多个复用器被配置为激活所述第二多个单位单元功率放大器;其中,所述第三多个复用器被配置为激活所述第三多个单位单元功率放大器。

[0104]

在示例16中,如示例1至15中的任何一项所述的主题,可以可选地还包括其中,所

述第一多个复用器被配置为在低功率模式中基于所述符号变化来激活所述第一多个单位单元功率放大器;其中,所述第二多个复用器被配置为在所述较低功率模式中基于所述符号变化来激活所述第二多个单位单元功率放大器;其中,所述第三多个复用器被配置为基于所述第一时钟或所述第二时钟的分量信号来激活所述第三多个单位单元功率放大器。

[0105]

示例17是一种用于将数字信号转换到模拟无线电频率的系统,该系统包括单位单元功率放大器的阵列,其中,所述单位单元功率放大器的阵列包括第一多个单位单元功率放大器、第二多个单位单元功率放大器、以及第三多个单位单元功率放大器;其中,所述第一多个单位单元功率放大器被配置为按照第一时钟操作;其中,所述第二多个单位单元功率放大器被配置为按照第二时钟操作;其中,所述第三多个单位单元功率放大器被配置为按照所述第一时钟或所述第二时钟操作;以及解码器,被配置为:为所述第一多个单位单元功率放大器输出所述第一时钟和所述第一时钟的使能信号;为所述第二多个单位单元功率放大器输出所述第二时钟和所述第二时钟的使能信号;为所述第三多个单位单元功率放大器区分所述第一时钟和所述第二时钟。

[0106]

在示例18中,如示例17所述的主题可以可选地还包括所述解码器被配置为接收低功率控制信号。

[0107]

在示例19中,如示例17或18所述的主题可以可选地还包括所述解码器包括多个接口寄存器。

[0108]

在示例20中,如示例17至19中的任何一项所述的主题,可以可选地还包括所述解码器包括用于所述第一多个单位单元功率放大器的第一组合逻辑,用于所述第二多个单位单元功率放大器的第二组合逻辑,以及用于所述第三多个单位单元功率放大器的第三组合逻辑。

[0109]

在示例21中,如示例17至20中的任何一项所述的主题,可以可选地还包括接口寄存器,其被配置为接收所述低功率控制信号并且将所述低功率控制信号路由到所述第一组合逻辑或所述第二组合逻辑。

[0110]

在示例22中,如示例17至21中的任何一项所述的主题,可以可选地还包括其中,所述解码器包括第一本地振荡器缓冲器和第二本地振荡器缓冲器。

[0111]

在示例23中,如示例17至22中的任何一项所述的主题可以可选地还包括第一线解码器和第二线解码器。

[0112]

在示例24中,如示例17至23中的任何一项所述的主题,可以可选地还包括其中,所述第一线解码器被配置为:接收来自所述第一本地振荡器的信号;基于来自所述第一本地振荡器的信号而激活所述第一多个单位单元功率放大器或所述第三多个单位单元功率放大器中的任何单位单元功率放大器;并且其中,所述第二线解码器被配置为:接收来自所述第二本地振荡器的信号;基于来自所述第二本地振荡器的信号而激活所述第二多个单位单元功率放大器或所述第三多个单位单元功率放大器中的任何单位单元功率放大器。

[0113]

在示例25中,如示例17至24中的任何一项所述的主题,可以可选地还包括其中,所述解码器还被配置为:接收数字信号;基于所述数字信号根据第一时钟激活所述第一多个单位单元功率放大器或所述第三多个单位单元功率放大器中的任何单位单元功率放大器;并且基于所述数字信号根据第二时钟激活所述第二多个单位单元功率放大器或所述第三多个单位单元功率放大器中的任何单位单元功率放大器。

[0114]

在示例26中,如示例17至25中的任何一项所述的主题,可以可选地还包括其中,所述解码器还包括相位选择器。

[0115]

在示例27中,如示例17至26中的任何一项所述的主题,可以可选地还包括其中,所述相位选择器还被配置为:接收多个时钟相位;接收多个数字信号;接收相位选择比特;基于所述多个时钟相位中的至少一者为所述第一时钟产生第一本地振荡器信号;并且基于所述多个时钟相位中的至少一者为所述第二时钟产生第二本地振荡器信号。

[0116]

在示例28中,如示例17至27中的任何一项所述的主题,可以可选地还包括其中,所述第一本地振荡器信号和所述第二本地振荡器信号表示相邻的相位。

[0117]

在示例29中,如示例17至28中的任何一项所述的主题,可以可选地还包括其中,所述第一振荡器信号被路由到第一本地振荡器缓冲器;并且所述第二振荡器信号被路由到第二本地振荡器缓冲器。

[0118]

在示例30中,如示例17至29中的任何一项所述的主题,可以可选地还包括其中,所述第一多个单位单元功率放大器部分地基于所述第一时钟的符号被激活;并且所述第二多个单位单元功率放大器部分地基于所述第二时钟的符号被激活。

[0119]

在示例31中,如示例17至30中的任何一项所述的主题,可以可选地还包括第一多个复用器,第二多个复用器,以及第三多个复用器;其中,所述第一多个复用器被配置为激活所述第一多个单位单元功率放大器;其中,所述第二多个复用器被配置为激活所述第二多个单位单元功率放大器;其中,所述第三多个复用器被配置为激活所述第三多个单位单元功率放大器。

[0120]

在示例32中,如示例17至31中的任何一项所述的主题,可以可选地还包括其中,所述第一多个复用器被配置为在低功率模式中基于所述符号变化来激活所述第一多个单位单元功率放大器;其中,所述第二多个复用器被配置为在所述较低功率模式中基于所述符号变化来激活所述第二多个单位单元功率放大器;其中,所述第三多个复用器被配置为基于所述第一时钟或所述第二时钟的分量信号来激活所述第三多个单位单元功率放大器。

[0121]

示例33是一种用于将数字信号转换到模拟无线电频率的装置,该装置包括单位单元功率放大器的阵列,其中,所述单位单元功率放大器的阵列包括第一多个单位单元功率放大器、第二多个单位单元功率放大器、以及第三多个单位单元功率放大器;其中,所述第一多个单位单元功率放大器被配置为按照第一时钟操作;其中,所述第二多个单位单元功率放大器被配置为按照第二时钟操作;其中,所述第三多个单位单元功率放大器被配置为按照所述第一时钟或所述第二时钟操作;以及解码器,被配置为:为所述第一多个单位单元功率放大器输出所述第一时钟和所述第一时钟的使能信号;为所述第二多个单位单元功率放大器输出所述第二时钟和所述第二时钟的使能信号;为所述第三多个单位单元功率放大器区分所述第一时钟和所述第二时钟。

[0122]

在示例34中,如示例33所述的主题可以可选地还包括所述解码器被配置为接收低功率控制信号。

[0123]

在示例35中,如示例33或34所述的主题可以可选地还包括所述解码器包括多个接口寄存器。

[0124]

在示例36中,如示例33至35中的任何一项所述的主题,可以可选地还包括所述解码器包括用于所述第一多个单位单元功率放大器的第一组合逻辑,用于所述第二多个单位

单元功率放大器的第二组合逻辑,以及用于所述第三多个单位单元功率放大器的第三组合逻辑。

[0125]

在示例37中,如示例33至36中的任何一项所述的主题,可以可选地还包括接口寄存器,其被配置为接收所述低功率控制信号并且将所述低功率控制信号路由到所述第一组合逻辑或所述第二组合逻辑。

[0126]

在示例38中,如示例33至37中的任何一项所述的主题,可以可选地还包括其中,所述解码器包括第一本地振荡器缓冲器和第二本地振荡器缓冲器。

[0127]

在示例39中,如示例33至38中的任何一项所述的主题可以可选地还包括第一线解码器和第二线解码器。

[0128]

在示例40中,如示例33至39中的任何一项所述的主题,可以可选地还包括其中,所述第一线解码器被配置为:接收来自所述第一本地振荡器的信号;基于来自所述第一本地振荡器的信号而激活所述第一多个单位单元功率放大器或所述第三多个单位单元功率放大器中的任何单位单元功率放大器;并且其中,所述第二线解码器被配置为:接收来自所述第二本地振荡器的信号;基于来自所述第二本地振荡器的信号而激活所述第二多个单位单元功率放大器或所述第三多个单位单元功率放大器中的任何单位单元功率放大器。

[0129]

在示例41中,如示例33至39中的任何一项所述的主题,可以可选地还包括其中,所述解码器还被配置为:接收数字信号;基于所述数字信号根据第一时钟激活所述第一多个单位单元功率放大器或所述第三多个单位单元功率放大器中的任何单位单元功率放大器;并且基于所述数字信号根据第二时钟激活所述第二多个单位单元功率放大器或所述第三多个单位单元功率放大器中的任何单位单元功率放大器。

[0130]

在示例42中,如示例33至40中的任何一项所述的主题,可以可选地还包括其中,所述解码器还包括相位选择器。

[0131]

在示例43中,如示例33至41中的任何一项所述的主题,可以可选地还包括其中,所述相位选择器还被配置为:接收多个时钟相位;接收多个数字信号;接收相位选择比特;基于所述多个时钟相位中的至少一者为所述第一时钟产生第一本地振荡器信号;并且基于所述多个时钟相位中的至少一者为所述第二时钟产生第二本地振荡器信号。

[0132]

在示例44中,如示例33至42中的任何一项所述的主题,可以可选地还包括其中,所述第一本地振荡器信号和所述第二本地振荡器信号表示相邻的相位。

[0133]

在示例45中,如示例33至43中的任何一项所述的主题,可以可选地还包括其中,所述第一振荡器信号被路由到第一本地振荡器缓冲器;并且所述第二振荡器信号被路由到第二本地振荡器缓冲器。

[0134]

在示例46中,如示例33至44中的任何一项所述的主题,可以可选地还包括其中,所述第一多个单位单元功率放大器部分地基于所述第一时钟的符号被激活;并且所述第二多个单位单元功率放大器部分地基于所述第二时钟的符号被激活。

[0135]

在示例47中,如示例33至45中的任何一项所述的主题,可以可选地还包括第一多个复用器,第二多个复用器,以及第三多个复用器;其中,所述第一多个复用器被配置为激活所述第一多个单位单元功率放大器;其中,所述第二多个复用器被配置为激活所述第二多个单位单元功率放大器;其中,所述第三多个复用器被配置为激活所述第三多个单位单元功率放大器。

[0136]

在示例48中,如示例33至46中的任何一项所述的主题,可以可选地还包括其中,所述第一多个复用器被配置为在低功率模式中基于所述符号变化来激活所述第一多个单位单元功率放大器;其中,所述第二多个复用器被配置为在所述较低功率模式中基于所述符号变化来激活所述第二多个单位单元功率放大器;其中,所述第三多个复用器被配置为基于所述第一时钟或所述第二时钟的分量信号来激活所述第三多个单位单元功率放大器。

[0137]

示例49是一种控制射频转换器的方法,包括:控制第一多个单位单元功率放大器,所述第一多个单位单元功率放大器被配置为按照第一时钟操作;控制第二多个单位单元功率放大器,所述第二多个单位单元功率放大器被配置为按照第二时钟操作;控制第三多个单位单元功率放大器,所述第三多个单位单元功率放大器被配置为按照所述第一时钟或所述第二时钟操作;并且为所述第一多个单位单元功率放大器输出所述第一时钟和所述第一时钟的使能信号;为所述第二多个单位单元功率放大器输出所述第二时钟和所述第二时钟的使能信号;为所述第三多个单位单元功率放大器区分所述第一时钟和所述第二时钟。

[0138]

在示例50中,如示例49所述的主题可以可选地还包括接收低功率控制信号。

[0139]

在示例51中,如示例49或50所述的主题可以可选地还包括控制多个接口寄存器来将低功率信号路由到第一组合逻辑或第二组合逻辑。

[0140]

在示例52中,如示例49至51中的任一项所述的主题可以可选地包括控制多个接口寄存器来将第一时钟路由到第一组合逻辑和第三组合逻辑;并且将第二时钟路由到第二组合逻辑和第三组合逻辑。

[0141]

在示例53中,如示例49至52中的任何一项所述的主题,可以可选地还包括控制第一组合逻辑来激活所述第一多个单位单元功率放大器,控制第二组合逻辑来激活所述第二多个单位单元功率放大器,并且控制第三组合逻辑来激活所述第三多个单位单元功率放大器。

[0142]

在示例54中,如示例49至53中的任何一项所述的主题,可以可选地还包括接收低功率控制信号并且将所述低功率控制信号路由到所述第一组合逻辑或所述第二组合逻辑。

[0143]

在示例55中,如示例49至54中的任何一项所述的主题,可以可选地还包括缓冲第一本地振荡器信号并且缓冲第二本地振荡器信号。

[0144]

在示例56中,如示例49至55中的任何一项所述的主题,可以可选地还包括对第一本地振荡器信号解码并且对第二本地振荡器信号解码。

[0145]

在示例57中,如示例49至56中的任何一项所述的主题,可以可选地还包括接收来自所述第一本地振荡器的信号并且基于来自所述第一本地振荡器的信号而激活所述第一多个单位单元功率放大器或所述第三多个单位单元功率放大器中的任何单位单元功率放大器;接收来自所述第二本地振荡器的信号并且基于来自所述第二本地振荡器的信号而激活所述第二多个单位单元功率放大器或所述第三多个单位单元功率放大器中的任何单位单元功率放大器。

[0146]

在示例58中,如示例49至57中的任何一项所述的主题,可以可选地还包括接收数字信号;基于所述数字信号根据第一时钟激活所述第一多个单位单元功率放大器或所述第三多个单位单元功率放大器中的任何单位单元功率放大器;并且基于所述数字信号根据第二时钟激活所述第二多个单位单元功率放大器或所述第三多个单位单元功率放大器中的任何单位单元功率放大器。

[0147]

在示例59中,如示例49至58中的任何一项所述的主题,可以可选地还包括从多个时钟相位中选择时钟信号。

[0148]

在示例60中,如示例49至59中的任何一项所述的主题,可以可选地还包括接收多个时钟相位;接收多个数字信号;接收相位选择比特;基于所述多个时钟相位中的至少一者为所述第一时钟产生第一本地振荡器信号;并且基于所述多个时钟相位中的至少一者为所述第二时钟产生第二本地振荡器信号。

[0149]

在示例61中,如示例49至60中的任何一项所述的主题,可以可选地还包括其中,基于相邻相位产生第一本地振荡器信号并且产生第二本地振荡器信号。

[0150]

在示例62中,如示例49至61中的任何一项所述的主题,可以可选地还包括将所述第一振荡器信号路由到第一本地振荡器缓冲器;并且将所述第二振荡器信号路由到第二本地振荡器缓冲器。

[0151]

在示例63中,如示例49至62中的任何一项所述的主题,可以可选地还包括部分地基于所述第一时钟的符号来激活所述第一多个单位单元功率放大器;并且部分地基于所述第二时钟的符号来激活所述第二多个单位单元功率放大器。

[0152]

在示例64中,如示例49至63中的任何一项所述的主题,可以可选地还包括控制第一多个复用器来激活所述第一多个单位单元功率放大器;控制第二多个复用器来激活所述第二多个单位单元功率放大器;并且控制第三多个复用器来激活所述第三多个单位单元功率放大器。

[0153]

在示例65中,如示例49至64中的任何一项所述的主题,可以可选地还包括控制第一多个复用器来在低功率模式中基于所述符号变化来激活所述第一多个单位单元功率放大器;控制所述第二多个复用器来在所述较低功率模式中基于所述符号变化来激活所述第二多个单位单元功率放大器;其中,所述第三多个复用器被配置为基于所述第一时钟或所述第二时钟的分量信号来激活所述第三多个单位单元功率放大器。

[0154]

示例66是一种非暂态计算机可读介质,其上存储有指令,所述指令当被转换器的一个或多个处理器执行时,使得所述转换器执行如示例49至64中的任何一项所述的方法。

[0155]

虽然已参考特定方面具体示出和描述了本发明,但本领域技术人员应当理解,在不脱离如所附权利要求限定的本发明的精神和范围的情况下,可对其进行形式和细节上的各种改变。本发明的范围从而由所附权利要求指出,并且因此希望包含属于权利要求的等同含义和范围内的所有变化。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1