显示装置的制作方法

1.本发明涉及显示装置。

背景技术:

2.在专利文献1中公开了对包括驱动晶体管、电容器、发光元件(例如,有机发光二极管)的像素电路供应2个电源电压(elvdd、eelvss)的构成。

3.现有技术文献

4.专利文献

5.专利文献1:日本公开专利公报“特开2015-49335”

技术实现要素:

6.发明要解决的问题

7.当上述2个电源电压不稳定时,存在无法精度良好地控制发光元件的亮度的问题。

8.用于解决问题的方案

9.本发明的一方案的显示装置具备包含多个像素电路的显示区域、边框区域以及端子部,在上述显示装置中,以包围上述显示区域的方式设置有框状的第1堤,在基板的上侧设置有薄膜晶体管层、发光元件层以及密封层,上述薄膜晶体管层包含第1金属层、第1层间绝缘膜、第2金属层、第2层间绝缘膜、第3金属层、第1平坦化膜、第4金属层以及第2平坦化膜,上述发光元件层包含第1电极、边缘覆盖膜、发光层以及第2电极,上述密封层包含第1无机密封膜、有机密封膜、第2无机密封膜,各像素电路包含发光元件、驱动晶体管以及电容器,上述显示区域包含扫描信号线、数据信号线以及与上述电容器的一个电极电连接的电源电压线,上述有机密封膜的端部由上述第1堤规定,在上述显示区域和上述第1堤之间,设置有除去了上述第1平坦化膜、上述第2平坦化膜以及上述边缘覆盖膜而成的第1狭缝,上述第3金属层包含与上述电源电压线电连接的第1电源干配线、以及经由与上述第1电极同层的导电膜与上述第2电极电连接的第2电源干配线,上述第4金属层包含与上述第1电源干配线接触的第1金属凸部、以及与上述第2电源干配线接触的第2金属凸部,上述第1电源干配线及上述第2电源干配线与上述第1狭缝重叠,上述第1堤包含:上述第1金属凸部及上述第2金属凸部;以及第1树脂凸部,其以与上述第1金属凸部及上述第2金属凸部重叠的方式按框状形成于与上述边缘覆盖膜相同的层。

10.发明效果

11.通过设置与第1电源干配线接触的第1金属凸部、以及与第2电源干配线接触的第2金属凸部,从第1电源干配线供应的第1电源电压和从第2电源干配线供应的第2电源电压得以稳定化,能够精度良好地控制发光元件的亮度。

附图说明

12.图1是示出实施方式1的显示装置的构成的俯视图。

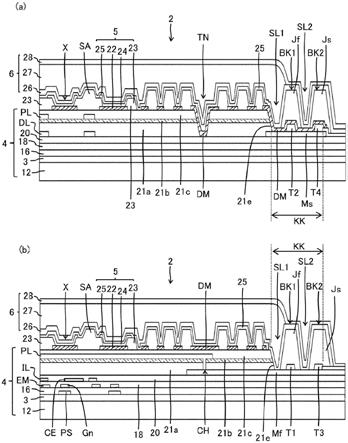

13.图2的(a)是图1的a-a截面图,图2的(b)是图1的b-b截面图。

14.图3是实施方式1的像素电路的电路图。

15.图4是示出实施方式1的显示装置的制造方法的流程图。

16.图5是示出实施方式1的显示装置的变形例的俯视图。

17.图6是示出本实施方式2的显示装置的构成的俯视图。

18.图7的(a)是图6的a-a截面图,图7的(b)是图6的b-b截面图。

具体实施方式

19.[实施方式1]

[0020]

图1是示出实施方式1的显示装置的构成的俯视图。图2的(a)是图1的a-a截面图,图2的(b)是图1的b-b截面图。

[0021]

如图1、图2所示,在显示装置2中,在基板12上按顺序形成有阻挡层3、薄膜晶体管层4、顶部发光(向上层侧发光)类型的发光元件层5以及密封层6,在显示区域da中形成有分别包含自发光型的发光元件x的多个像素电路pk。在包围显示区域da的边框区域na设置有端子部ta。

[0022]

基板12是玻璃基板或者以聚酰亚胺等树脂为主要成分的挠性基板,例如,也能够由两层的聚酰亚胺膜和被它们夹着的无机膜构成基板12。阻挡层(底涂层)3是防止水、氧等异物侵入的无机绝缘层,例如能够使用氮化硅、氧化硅等构成。

[0023]

如图2所示,薄膜晶体管层4包含:半导体层ps,其比阻挡层3靠上层;栅极绝缘膜16,其比半导体层ps靠上层;第1金属层(包含扫描信号线gn),其比栅极绝缘膜16靠上层;第1层间绝缘膜18,其比第1金属层靠上层;第2金属层(包含初始化电压线il),其比第1层间绝缘膜18靠上层;第2层间绝缘膜20,其比第2金属层靠上层;第3金属层(包含数据信号线dl),其比第2层间绝缘膜20靠上层;第1平坦化膜21a,其比第3金属层靠上层;第3层间绝缘膜21b,其比第1平坦化膜21a靠上层;第4金属层(包含电源电压线pl),其比第3层间绝缘膜21b靠上层;以及第2平坦化膜21c,其比第4金属层靠上层。

[0024]

半导体层ps例如是低温形成的多晶硅(ltps),各种晶体管以包含与扫描信号线gn同层的栅极电极及半导体层ps的方式构成。关于半导体层ps,也可以是晶体管的沟道区域以外的区域被导体化。

[0025]

第1金属层、第2金属层、第3金属层以及第4金属层例如由包含铝、钨、钼、钽、铬、钛以及铜中的至少1者的金属的单层膜或多层膜构成。

[0026]

栅极绝缘膜16、第1层间绝缘膜18、第2层间绝缘膜20以及第3层间绝缘膜21b例如能够由通过cvd法形成的、氧化硅(siox)膜或氮化硅(sinx)膜或者它们的层叠膜构成。第1平坦化膜21a及第2平坦化膜21c例如能够由聚酰亚胺、丙烯酸树脂等可涂敷的有机材料构成。

[0027]

发光元件层5包含:第1电极(下部电极)22,其比平坦化膜21靠上层;绝缘性的边缘覆盖膜23,其覆盖第1电极22的边缘;el(电致发光)层24,其比边缘覆盖膜23靠上层;以及第2电极(上部电极)25,其比el层24靠上层。边缘覆盖膜23例如通过在涂敷聚酰亚胺、丙烯酸树脂等有机材料后利用光刻进行图案化来形成。

[0028]

在发光元件层5例如形成发出不同颜色的多个发光元件x,各发光元件包含岛状的

第1电极22、el层24(包含发光层)以及第2电极25。第2电极25是在多个发光元件中共用的满面状的共用电极。

[0029]

发光元件x例如可以是包含有机层作为发光层的oled(有机发光二极管),也可以是包含量子点层作为发光层的qled(量子点发光二极管)。

[0030]

el层24例如通过从下层侧起按顺序层叠空穴注入层、空穴传输层、发光层、电子传输层、电子注入层来构成。发光层通过蒸镀法或喷墨法或光刻法在边缘覆盖膜23的开口(按每个发光元件)形成为岛状。其它层形成为岛状或满面状(共用层)。另外,也能够设为不形成空穴注入层、空穴传输层、电子传输层、电子注入层中的1个以上的层的构成。

[0031]

第1电极22(阳极)例如是通过ito(indium tin oxide:铟锡氧化物)与ag(银)或包含ag的合金的层叠而构成的光反射电极。第2电极25(阴极)例如由镁银合金等金属薄膜构成,具有光透射性。

[0032]

在发光元件x为oled的情况下,通过第1电极22和第2电极25之间的驱动电流,空穴与电子在发光层ek内复合,由此产生的激子在转变为基底状态的过程中放出光。在发光元件x为qled的情况下,通过第1电极22和第2电极25之间的驱动电流,空穴与电子在发光层ek内复合,由此产生的激子在从量子点的导带能级(conduction band)转变为价带能级(valence band)的过程中放出光。

[0033]

在图2的(b)中,覆盖发光元件层5的密封层6是防止水、氧等异物向发光元件层5浸透的层,能够由第1无机密封膜26及第2无机密封膜28和形成在它们之间的有机密封膜27构成。

[0034]

图3是示出像素电路的一个例子的电路图。该像素电路不过是一个例子,能采用其它各种构成。

[0035]

图3的像素电路包含:发光元件x;电容器cp;第1初始化晶体管tri,其栅极端子连接到前级(n-1级)的扫描信号线gn-1;阈值控制晶体管trs,其栅极端子连接到本级(n级)的扫描信号线gn;写入控制晶体管trw,其栅极端子连接到本级(n级)的扫描信号线gn;驱动晶体管trd,其控制发光元件x的电流;电源供应晶体管trp,其栅极端子连接到发光控制线em(n级);发光控制晶体管tre,其栅极端子连接到发光控制线em(n级);以及第2初始化晶体管trj,其栅极端子连接到本级(n级)的扫描信号线gn。

[0036]

驱动晶体管trd的栅极端子经由电容器cp连接到电源电压线pl,并且经由第1初始化晶体管tri连接到初始化电压线il。驱动晶体管trd的源极端子经由写入控制晶体管trw连接到数据信号线dl,并且经由电源供应晶体管trp连接到电源电压线pl。驱动晶体管trd的漏极端子经由发光控制晶体管tre连接到发光元件x的阳极,并且经由阈值控制晶体管trs连接到驱动晶体管trd的栅极端子。发光元件x的阳极经由第2初始化晶体管trj连接到初始化电压线il。例如,对电源电压线pl供应高电压侧的第1电源电压(elvdd),对发光元件x的阴极供应低电压侧的第2电源电压(elvss)。

[0037]

在边框区域na设置:端子部ta,其与显示区域da的一个边相面对;堤bk1,其为框状,包围显示区域da;以及堤bk2,其为框状,包围堤bk1。第1堤bk1例如作为喷射涂敷有机密封膜27时的阻液件发挥功能,规定有机密封膜27的端部(边缘)。

[0038]

在显示区域da和堤bk1之间,设置有除去了第1平坦化膜21a、第3层间绝缘膜21b、第2平坦化膜21c以及边缘覆盖膜23而成的沟槽tn。沟槽tn沿着显示区域da的三个边、以及

余下的一个边(与端子部ta相面对的边)的两端形成。在端子部ta与第2堤bk2之间形成折弯部zs。能够通过折弯部zs将端子部ta向背面(下表面)侧折弯。

[0039]

在端子部ta与显示区域da之间,设置有与第1堤bk1及第2堤bk2重叠并经过沟槽tn的中断处的第1电源干配线mf,第1电源干配线mf与数据信号线dl一起包含于第3金属层,并经由2个引出配线hf连接到端子部ta。经由端子部ta对第1电源干配线mf供应第1电源电压(elvdd),多个电源电压线pl分别与第1电源干配线mf电连接。

[0040]

在沟槽tn的外侧,设置有与第1堤bk1及第2堤bk2重叠并沿着沟槽tn这样的第2电源干配线ms,第2电源干配线ms与数据信号线dl一起包含于第3金属层,并经由2个引出配线hs连接到端子部ta。经由端子部ta对第2电源干配线ms供应第2电源电压(elvss),发光元件x的第2电极(阴极)25与第2电源干配线ms电连接。

[0041]

在显示部da中,多个扫描信号线gn、多个发光控制线em以及多个初始化电压线il在行方向上延伸,多个电源电压线pl及多个数据信号线dl在列方向上延伸。多个电源电压线pl也可以在行方向及列方向上延伸并按格子状设置。在边框区域na中,折弯部zs在行方向上延伸,2个引出配线hf及2个引出配线hs在列方向上延伸。此外,2个引出配线hf设置于2个引出配线hs之间。像素电路pk以对应于扫描信号线gn与数据信号线dl的交点的方式按矩阵状设置有多个。

[0042]

如图1、图2所示,在显示装置2中,在显示区域da和第1堤bk1之间设置有除去了第1平坦化膜21a、第3层间绝缘膜21b、第2平坦化膜21c以及边缘覆盖膜23而成的第1狭缝sl1,第1电源干配线mf及第2电源干配线ms与第1狭缝sl1重叠。

[0043]

另外,在第1堤bk1和第2堤bk2之间设置有除去了第1平坦化膜21a、第3层间绝缘膜21b、第2平坦化膜21c以及边缘覆盖膜23而成的第2狭缝sl2,第1电源干配线mf及第2电源干配线ms与第2狭缝sl2重叠。

[0044]

在包含第1电极22的第1电极层中,形成有与沟槽tn、第1狭缝sl1、第1堤bk1以及第2堤bk2重叠的导电膜dm,导电膜dm在沟槽tn中与第2电极25接触,在第1狭缝sl1中与第2电源干配线ms接触。在图2中,在第1狭缝sl1与第3层间绝缘膜21b的开口kk的重叠部中,导电膜dm与第2电源干配线ms接触。电源电压线pl在将第1平坦化膜21a及第3层间绝缘膜21b贯通的接触孔ch中与第1电源干配线mf接触。

[0045]

在包含电源电压线pl的第4金属层中形成:第1金属凸部t1及第3金属凸部t3,其与第1电源干配线mf接触;以及第2金属凸部t2及第4金属凸部t4,其与第2电源干配线ms接触。

[0046]

第1金属凸部t1及第3金属凸部t3是形成在端子部ta与显示区域da之间的线状凸部,第2金属凸部t2及第4金属凸部t4是以沿着与端子部ta相对的显示区域da的一个边的一部分、以及显示区域da的余下的三个边的方式形成的框状凸部。在图2中,在第3层间绝缘膜21b的开口kk下,第1电源干配线mf与第1金属凸部t1及第3金属凸部t3接触,第2电源干配线ms与第2金属凸部t2及第4金属凸部t4接触。

[0047]

第1堤bk1构成为包括:第1金属凸部t1及第2金属凸部t2;第1树脂凸部jf,其以与第1金属凸部t1及第2金属凸部t2重叠的方式按框状形成于比第1电极22靠上的层(在图2中,是与边缘覆盖膜23相同的层);以及岛状金属凸部t5,其在第1金属凸部t1和第2金属凸部t2之间形成于与它们相同的层(第4金属层)。

[0048]

第2堤bk2构成为包括:第3金属凸部t3及第4金属凸部t4;第2树脂凸部js,其以与

第3金属凸部t3及第4金属凸部t4重叠的方式按框状形成于比第1电极22靠上的层(在图2中,是与边缘覆盖膜23相同的层);以及岛状金属凸部t6,其在第3金属凸部t3和第4金属凸部t4之间形成于与它们相同的层(第4金属层)。

[0049]

通过设置岛状金属凸部t5,能够确保第1堤bk1的厚度。岛状金属凸部t5是与第1金属凸部t1及第2金属凸部t2电绝缘的。例如即使第1金属凸部t1与岛状金属凸部t5由于工序的偏差而被电连接了,进一步导致岛状金属凸部t5与第2金属凸部t2被电连接的可能性也低。即,第1金属凸部t1及第2金属凸部t2发生漏电的可能性低,能够保证成品率。

[0050]

另外,通过设置岛状金属凸部t6,能够确保第2堤bk2的厚度。岛状金属凸部t6是与第3金属凸部t3及第4金属凸部t4电绝缘的。在此,例如即使第3金属凸部t3与岛状金属凸部t6由于工序的偏差而被电连接了,进一步导致岛状金属凸部t6与第4金属凸部t4被电连接的可能性也低。即,第3金属凸部t3及第4金属凸部t4发生漏电的可能性低,能够保证成品率。

[0051]

这样,通过设置第1金属凸部t1~第4金属凸部t4,能够实现第1电源干配线mf及第2电源干配线ms的低电阻化,从第1电源干配线mf供应到电源配线pl的第1电源电压(elvdd)和从第2电源干配线ms供应到第2电极25的第2电源电压(elvss)得以稳定化,能够精度良好地控制发光元件x的亮度。

[0052]

另外,与在第1树脂凸部jf之下残留第2平坦化膜21c(有机膜)的情况相比,能够抑制第1堤bk1的高度,因此能够防止第1电源干配线mf与第2电源干配线ms的相邻部as在第1狭缝sl1处易于发生的两者(mf、ms)的短路。当第1堤bk1过高时,导电膜dm有时会在相邻部as处没有被蚀刻而残留,这成为第1电源干配线mf与第2电源干配线ms的短路原因。

[0053]

此外,第4金属层(包含电源电压线pl、第1金属凸部t1~第4金属凸部t4、岛状金属凸部t5、t6)的厚度例如是1μm,第1堤bk1的厚度(高度)例如是3.5μm,第2堤bk2的厚度(高度)例如是4μm,第3金属层(包含数据信号线dl、第1电源干配线mf、第2电源干配线ms)的厚度例如是1μm,第1平坦化膜21a及第2平坦化膜21c各自的厚度例如是1.5μm。

[0054]

感光间隔物sa作为发光层蒸镀时的fmm的抵接面发挥功能,能够与第1树脂凸部jf及第2树脂凸部js同样地形成于与边缘覆盖膜23相同的层。

[0055]

如果第1金属凸部t1与第2金属凸部t2的间隙小,则也可以不设置岛状金属凸部t5,如果第3金属凸部t3与第4金属凸部t4的间隙小,则也可以不设置岛状金属凸部t6。其原因是,通过第1树脂凸部jf及第2树脂凸部js的表面张力,能够确保第1堤bk1及第2堤bk2的厚度。

[0056]

第3层间绝缘膜21b设置于第1平坦化膜21a与第4金属层之间,但不限于此,也可以设置于第3金属层与第1平坦化膜21a之间。

[0057]

图4是示出实施方式1的显示装置的制造方法的流程图。在步骤s1中,形成基板12。在步骤s2中,进行底涂层3的成膜。在步骤s3中,进行半导体层ps的成膜。在步骤s4中,进行光刻。在步骤s5中,进行半导体层ps的图案化。在步骤s6中,进行栅极绝缘膜16的成膜。在步骤s7中,进行第1金属层的成膜。在步骤s8中,进行光刻。在步骤s9中,进行第1金属层(包含扫描信号线gn、发光控制线em、各晶体管的栅极电极)的图案化。在步骤s10中,进行第1层间绝缘膜18的成膜。在步骤s11中,进行第2金属层的成膜。在步骤s12中,进行光刻。在步骤s13中,进行第2金属层(包含初始化电压线il、作为电容器的一个电极的电容电极ce)的图案

化。在步骤s14中,进行第2层间绝缘膜20的成膜。在步骤s15中,进行光刻。在步骤s16中,进行第2层间绝缘膜20、第1层间绝缘膜18、栅极绝缘膜16的图案化(接触孔的形成)。在步骤s17中,进行光刻。在步骤s18中,进行折弯部zs的蚀刻(第2层间绝缘膜20、第1层间绝缘膜18、栅极绝缘膜16、底涂层3)。在步骤s19中,对在步骤s18中形成的、折弯部zs的凹陷进行填充层(例如,聚酰亚胺)的涂敷。在步骤s20中,进行光刻。

[0058]

在步骤s21中,进行填充层的图案化。在步骤s22中,进行第3金属层的成膜。在步骤s23中,进行光刻。在步骤s24中,进行第3金属层(包含数据信号线dl、第1电源干配线mf、第2电源干配线ms)的图案化。在步骤s25中,进行第1平坦化膜21a的涂敷。在步骤s26中,进行光刻。在步骤s27中,进行第1平坦化膜21a的图案化。在步骤s28中,进行第3层间绝缘膜21b的成膜。在步骤s29中,进行光刻。在步骤s30中,进行第3层间绝缘膜21b的图案化。在步骤s31中,进行第4金属层的成膜。在步骤s32中,进行光刻。在步骤s33中,进行第4金属层(包含电源电压线pl、第1金属凸部t1~第4金属凸部t4、岛状金属凸部t5、t6)的图案化。在步骤s34中,进行第2平坦化膜21c的涂敷。在步骤s35中,进行光刻。在步骤s36中,进行第2平坦化膜21c的图案化。在步骤s37中,进行第1电极层的成膜。在步骤s38中,进行光刻。在步骤s39中,进行第1电极层(包含第1电极22、导电膜dm)的图案化。在步骤s40中,进行边缘覆盖层的涂敷。在步骤s41中,进行光刻。在步骤s42中,进行边缘覆盖层(包含边缘覆盖膜23、第1树脂凸部jf、第2树脂凸部js)的图案化。

[0059]

<变形例>

[0060]

图5是示出实施方式1的显示装置的变形例的俯视图。在图5中,在第1电源干配线mf与第2电源干配线ms的相邻区域as中,第1平坦化膜21a的边缘21e下的第1电源干配线mf与第2电源干配线ms的间隙宽度比第1堤bk1下的第1电源干配线mf与第2电源干配线ms的间隙宽度大。也就是说,在第2电源干配线ms与第1平坦化膜21a交叉之处,在第2电源干配线ms设置有切口。这样的话,在第1平坦化膜21a的边缘21e上第4金属层及导电膜dm的残留膜难以从第1电源干配线mf连续至第2电源干配线ms,经由残留膜的第1电源干配线mf与第2电源干配线ms的短路发生得到抑制。

[0061]

[实施方式2]

[0062]

图6是示出实施方式2的显示装置的构成的俯视图。图7的(a)是图6的a-a截面图,图7的(b)是图6的b-b截面图。在图7的(a)中,在第1狭缝sl1中,第2电源干配线ms由第3层间绝缘膜21b覆盖,在第3层间绝缘膜21b中至少形成有与第1堤bk1重叠的开口、以及与第2堤bk2重叠的开口,导电膜dm与第2电源干配线ms经由第2金属凸部t2及第4金属凸部t4电连接。

[0063]

即,导电膜dm覆盖第2金属凸部t2及第4金属凸部t4,在第3层间绝缘膜21b的与第1堤bk1重叠的开口中,第2电源干配线ms与第2金属凸部t2接触,在第3层间绝缘膜21b的与第2堤bk2重叠的开口中,第2电源干配线ms与第4金属凸部t4接触。由此,能够实现第2电源干配线ms的低电阻化。

[0064]

在图7的(b)中,在第1狭缝sl1中,第1电源干配线mf由第3层间绝缘膜21b覆盖,在第3层间绝缘膜21b中,至少形成有与第1堤bk1重叠的开口、以及与第2堤bk2重叠的开口,在第3层间绝缘膜21b的与第1堤bk1重叠的开口中,第1电源干配线mf与第1金属凸部t1接触,在第3层间绝缘膜21b的与第2堤bk2重叠的开口中,第1电源干配线mf与第3金属凸部t3接

触。由此,能够实现第1电源干配线mf的低电阻化。

[0065]

在实施方式2中,设置在第1平坦化膜21a与第4金属层之间的第3层间绝缘膜21b只要至少覆盖第1平坦化膜21a的边缘21e并包含与第1堤bk1重叠的开口、以及与第2堤bk2重叠的开口即可。

[0066]

根据实施方式2,在第1电源干配线mf与第2电源干配线ms的相邻区域as中,即使在第1平坦化膜21a的边缘21e上发生导电膜dm的膜残留,由于第3层间绝缘膜21b,残留膜也会与第1电源干配线mf及第2电源干配线ms绝缘,因此,能够防止经由残留膜的第1电源干配线mf与第2电源干配线ms的短路发生。

[0067]

上述的各实施方式以例示和说明为目的,不以限定为目的。如果基于这些例示和说明,则很多变形方式成为可能,这对于本领域技术人员而言是显而易见的。

[0068]

[方案1]

[0069]

一种显示装置,具备包含多个像素电路的显示区域、边框区域以及端子部,在上述显示装置中,

[0070]

以包围上述显示区域的方式设置有框状的第1堤,

[0071]

在基板的上侧设置有薄膜晶体管层、发光元件层以及密封层,

[0072]

上述薄膜晶体管层包含第1金属层、第1层间绝缘膜、第2金属层、第2层间绝缘膜、第3金属层、第1平坦化膜、第4金属层以及第2平坦化膜,

[0073]

上述发光元件层包含第1电极、边缘覆盖膜、发光层以及第2电极,

[0074]

上述密封层包含第1无机密封膜、有机密封膜、第2无机密封膜,

[0075]

各像素电路包含发光元件、驱动晶体管以及电容器,

[0076]

上述显示区域包含扫描信号线、数据信号线以及与上述电容器的一个电极电连接的电源电压线,

[0077]

上述有机密封膜的端部由上述第1堤规定,

[0078]

在上述显示区域和上述第1堤之间,设置有除去了上述第1平坦化膜、上述第2平坦化膜以及上述边缘覆盖膜而成的第1狭缝,

[0079]

上述第3金属层包含与上述电源电压线电连接的第1电源干配线、以及经由与上述第1电极同层的导电膜与上述第2电极电连接的第2电源干配线,

[0080]

上述第4金属层包含与上述第1电源干配线接触的第1金属凸部、以及与上述第2电源干配线接触的第2金属凸部,

[0081]

上述第1电源干配线及上述第2电源干配线与上述第1狭缝重叠,

[0082]

上述第1堤包含:上述第1金属凸部;上述第2金属凸部;以及第1树脂凸部,其与上述第1金属凸部及上述第2金属凸部重叠,并且按框状形成于比上述第1电极靠上的层。

[0083]

[方案2]

[0084]

例如根据方案1所述的显示装置,

[0085]

上述第1树脂凸部与上述边缘覆盖膜同层并且由与上述边缘覆盖膜相同的材料构成。

[0086]

[方案3]

[0087]

例如根据方案2所述的显示装置,

[0088]

上述第1金属凸部设置在上述端子部和与上述端子部相对的上述显示区域的一个

边之间。

[0089]

[方案4]

[0090]

例如根据方案3所述的显示装置,

[0091]

上述第2金属凸部以沿着与上述端子部相对的上述显示区域的一个边的一部分、以及上述显示区域的余下的三个边的方式设置。

[0092]

[方案5]

[0093]

例如根据方案1~4中的任意1个方案所述的显示装置,

[0094]

上述第1堤包含岛状金属凸部,上述岛状金属凸部在上述第1金属凸部和上述第2金属凸部之间形成于与它们相同的层。

[0095]

[方案6]

[0096]

例如根据方案1~5中的任意1个方案所述的显示装置,

[0097]

在上述第3金属层和上述第4金属层之间设置有第3层间绝缘膜,

[0098]

在上述第3层间绝缘膜的开口下,上述第1电源干配线与上述第1金属凸部接触,上述第2电源干配线与上述第2金属凸部接触。

[0099]

[方案7]

[0100]

例如根据方案6所述的显示装置,

[0101]

在上述第1狭缝与上述第3层间绝缘膜的开口的重叠部中,上述导电膜与上述第2电源干配线接触。

[0102]

[方案8]

[0103]

例如根据方案7所述的显示装置,

[0104]

在上述第1电源干配线与上述第2电源干配线相邻的区域中,上述第1平坦化膜的边缘下的上述第1电源干配线与上述第2电源干配线的间隙宽度比第1堤下的上述第1电源干配线与上述第2电源干配线的间隙宽度大。

[0105]

[方案9]

[0106]

例如根据方案1~5中的任意1个方案所述的显示装置,

[0107]

在上述第1平坦化膜与上述第4金属层之间设置有第3层间绝缘膜,

[0108]

在上述第1狭缝中,上述第1电源干配线及上述第2电源干配线由上述第3层间绝缘膜覆盖。

[0109]

[方案10]

[0110]

例如根据方案9所述的显示装置,

[0111]

上述导电膜与上述第2电源干配线经由上述第2金属凸部电连接。

[0112]

[方案11]

[0113]

例如根据方案1~10中的任意1个方案所述的显示装置,

[0114]

上述扫描信号线包含于第1金属层,

[0115]

作为上述电容器的一个电极发挥功能的电容电极包含于上述第2金属层,

[0116]

上述数据信号线包含于上述第3金属层,

[0117]

上述电源电压线包含于上述第4金属层。

[0118]

[方案12]

[0119]

例如根据方案1~11中的任意1个方案所述的显示装置,

[0120]

以包围上述第1堤的方式按框状设置有第2堤,

[0121]

在上述第1堤和上述第2堤之间,设置有除去了上述第1平坦化膜、上述第2平坦化膜以及上述边缘覆盖膜而成的第2狭缝,

[0122]

上述第1电源干配线及上述第2电源干配线与上述第2狭缝重叠,

[0123]

上述第4金属层包含与上述第1电源干配线接触的第3金属凸部、以及与上述第2电源干配线接触的第4金属凸部,

[0124]

上述第2堤包含:上述第3金属凸部及上述第4金属凸部;以及第2树脂凸部,其以与上述第3金属凸部及上述第4金属凸部重叠的方式按框状形成于比上述第1电极靠上的层。

[0125]

附图标记说明

[0126]

2 显示装置

[0127]

4 薄膜晶体管层

[0128]

5 发光元件层

[0129]

6 密封层

[0130]

12 基板

[0131]

16 栅极绝缘膜

[0132]

18 第1层间绝缘膜

[0133]

20 第2层间绝缘膜

[0134]

21a 第1平坦化膜

[0135]

21b 第3层间绝缘膜

[0136]

21c 第2平坦化膜

[0137]

22 第1电极

[0138]

23 边缘覆盖膜

[0139]

24 el层

[0140]

25 第2电极

[0141]

x 发光元件

[0142]

pk 像素电路

[0143]

cp 电容器

[0144]

ps 半导体层

[0145]

gn 扫描信号线

[0146]

pl 电源电压线

[0147]

dl 数据信号线

[0148]

trd 驱动晶体管

[0149]

bk1 第1堤

[0150]

bk2 第2堤

[0151]

sl1 第1狭缝

[0152]

sl2 第2狭缝

[0153]

mf 第1电源干配线

[0154]

ms 第2电源干配线

[0155]

t1~t4 第1金属凸部~第4金属凸部

[0156]

t5~t6 岛状金属凸部

[0157]

da 显示区域

[0158]

na 边框区域

[0159]

ta 端子部

[0160]

jf 第1树脂凸部

[0161]

js 第2树脂凸部。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1