电路板的插件孔结构及其制造方法与流程

1.本发明是有关于一种电路板结构,尤其是指一种电路板的插件孔(焊接孔)结构及其制造方法。

背景技术:

2.一般电路板除了布设电子线路外,另有一些电路板需插接电子组件;由于某些电子组件具有接脚,因此要结合到电路板时,需在电路板设置相对应的插件孔(焊接孔),借以穿设电子组件的接脚,并将该电子组件的接脚焊接于电路板的背面。

3.再者,为求快速且大量的生产,前述电路板上的电子组件接脚通常是通过使用锡炉的波焊制程(wave solder process)而将接脚上锡,以使穿设在插接孔中的电子组件的接脚(pin)结合到电路板,并达到电性连接的目的。然而,由于波焊制程的时间通常很短,但电路板的插件孔导热却很慢,致使锡炉内的锡料无法在短时间内爬上电子组件的接脚而发生沾锡不良等缺陷,影响电子组件的电气特性,降低电路板的优良率。

4.有鉴于此,本发明人遂针对上述现有技术,特潜心研究并配合学理的运用,尽力解决上述的问题点,即成为本发明人改良的目标。

技术实现要素:

5.本发明的目的之一,在于提供一种电路板的插件孔结构,借以使插接用的电子组件的接脚良好地焊接至插件孔,以提高电路板的焊接速度、可靠度及制程优良率。

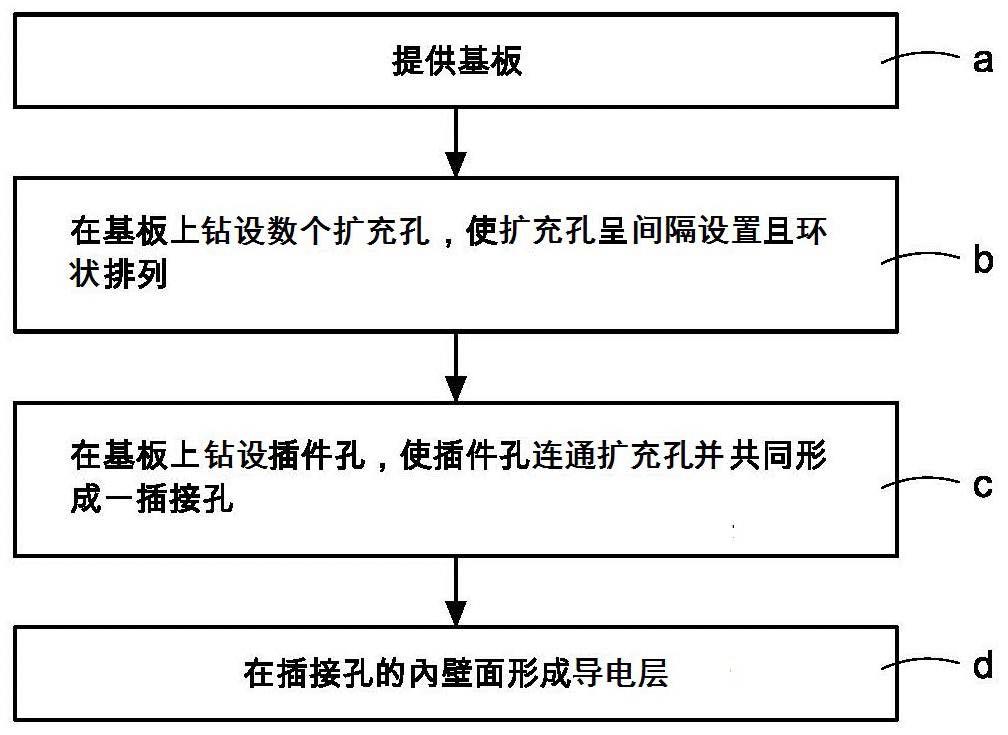

6.为了达成上述的目的,本发明为一种电路板的插件孔的制造方法,用以在电路板上形成插接至少一电子组件的插件孔结构,包括:a)提供一基板,该基板具有相对的一第一表面及一第二表面;b)在该基板上钻设贯穿该第一表面及该第二表面的数个扩充孔,该数个扩充孔为间隔设置且呈环状排列;c)在该基板上钻设贯穿该第一表面及该第二表面的一插件孔,该插件孔连通该数个扩充孔并与该数个扩充孔共同形成一插接孔;以及d)在该插接孔的内壁面形成一导电层。

7.为了达成上述的目的,本发明为一种电路板的插件孔结构,包括基板、插件孔、数个扩充孔及导电层。基板具有相对的第一表面及第二表面;插件孔设置在基板上并贯穿第一表面及第二表面;数个扩充孔设置在基板上并贯穿第一表面及第二表面,该数个扩充孔呈间隔设置并环状排列在插件孔的外周缘,且该数个扩充孔连通插件孔而与该插件孔共同形成插接孔;以及导电层成型在插接孔的内壁面。

8.相较于已知技术,本发明的电路板的插件孔的制造方法主要是先在基板上设置间隔且呈环状排列的数个扩充孔,接着在该数个扩充孔所围合的中心位置处设置插件孔,并使插件孔连通该数个扩充孔而共同形成插接孔,借此扩大插件孔的范围,另外在插接孔的内壁面形成导电层,以完成插接孔与电路板的电性导接;后续,将电子组件的接脚插入电路板的插接孔中,并将其送入锡炉进行焊接,据此使焊锡沾附在接脚及插接孔的导电层;据此,本发明的电路板的接脚在插件孔时可加快焊接速度,并可节省焊接时间;此外,电子组

件的接脚可良好地焊接在插件孔中而使电子组件结合在电路板上,借此提高电路板的可靠度及制程优良率,增加本发明的实用性。

附图说明

9.图1为本发明的电路板及电子组件插接前的示意图。

10.图2为本发明的电路板的插件孔的制造方法流程示意图。

11.图3至图7为本发明的电路板的插件孔的制造过程示意图。

12.图8为本发明的电路板及电子组件插接后的组合示意图。

13.附图中的符号说明:1: 电路板;2: 电子组件;3: 接脚;4: 焊锡;10: 基板;11: 第一表面;12: 第二表面;20: 插件孔;200: 插接孔;30: 扩充孔;40: 导电层;41: 第一焊接垫;42: 第二焊接垫;a)~d): 步骤。

具体实施方式

14.有关本发明的详细说明及技术内容,配合图式说明如下,然而所附图式仅提供参考与说明用,并非用来对本发明加以限制。

15.请参照图1,为本发明的电路板及电子组件插接前的示意图。本发明提供一种电路板的插件孔结构,用以插接至少一电子组件2,包括一基板10、一插件孔20、数个扩充孔30及一导电层40。该插件孔20及该数个扩充孔30设置在该基板10上,该导电层40是设置在该插件孔20及该数个扩充孔30的内壁面,据以构成一电路板1。更详细描述该电路板1的插件孔结构及制造方法如后。

16.请另参照图2,为本发明的电路板的插件孔的制造方法流程示意图;请同时参照图3至图7,为本发明的电路板的插件孔的制造过程示意图。本发明电路板1的插件孔的制造方法如下述。如图3所示,步骤a),首先提供一基板10,该基板10具有相对的一第一表面11及一第二表面12;较佳地,该基板10为一多层基板,例如电木板或玻璃纤维等材质所构成。

17.另外,请参照图4,步骤b),在该基板10上钻设贯穿该第一表面11及该第二表面12的数个扩充孔30,且该数个扩充孔30为间隔设置且呈环状排列。续参照图5,步骤c),在该基板10上钻设贯穿该第一表面11及该第二表面12的一插件孔20,该插件孔20是连通该数个扩充孔30并与该数个扩充孔30共同形成一插接孔200。

18.本实施例中,该插件孔20设置为一圆孔,另外,该数个扩充孔30分别设置为一半开孔,各该扩充孔30的两端分别连接该插件孔20的周缘;据此,该数个扩充孔30呈放射状地排列在该插件孔20的周缘,举例来说,该插接孔200的轮廓可设置呈梅花状。

19.请同时参照图6及图7,步骤d),在该插接孔200(由该插件孔20及该数个扩充孔30所构成)的内壁面形成一导电层40。较佳地,该导电层40为一铜箔层,且该导电层40与该基板10的电路(图未示)形成电性导接。

20.具体而言,该数个扩充孔30是呈间隔设置并环状排列在该插件孔20的外周缘,且该数个扩充孔30是连通该插件孔20而与该插件孔20共同形成该插接孔200。另外,该导电层40成型在该插接孔200的内壁面。

21.于本发明的一实施例中,该电路板1的插件孔20的制造方法还包括步骤e),在该第

一表面11形成一第一焊接垫41,另外在该第二表面12形成一第二焊接垫42,该导电层40是连接该第一焊接垫41及该第二焊接垫42。较佳地,该第一焊接垫41、该第二焊接垫42及该导电层40是通过一电镀制程而一体成型。

22.即,该电路板1的插件孔结构还包括一第一焊接垫41及一第二焊接垫42。该第一焊接垫41成型在该插接孔200的周缘并位于该第一表面11,该第二焊接垫42成型在该插接孔200的周缘并位于该第二表面12。该导电层40连接该第一焊接垫41及该第二焊接垫42,借以达到相互导接的目的。

23.要说明的是,于本实施例中,该插接孔200为一导通孔(plating through hole),实际实施时则不以此为限制,该插接孔200可单纯设为一贯通孔而通过该第一焊接垫41及/或该第二焊接垫42而完成电性导接。

24.请续参照图8,为本发明的电路板及电子组件插接后的组合示意图。本发明的电路板1的插件孔的制造方法还包括步骤f),将一电子组件2安置在该基板10上并使其接脚3插入该插接孔200。

25.最后进入步骤g),将插接有该电子组件2的该电路板1送入具有焊锡4的一锡炉(图未示)中从而使部分的焊锡4沾附在该接脚3上,一部分的焊锡4也会沾附在该第二焊接垫42及该插接孔200的导电层40上;要注意的是,同时还有一部分的焊锡4会沿着该导电层40而沾附在该第一焊接垫41上。借此,该电子组件2的插脚3通过该焊锡4而结合在该插接孔200中,并据此将该电子组件2结合在该电路板1上。

26.举例来说,以传统电路板上所设置的插件孔20的孔径为0.66mm而言,另外在该插件孔20的周缘间隔设置并环状排列数个扩充孔30而形成插接孔200,该插接孔200的孔径大约为1.27mm。在此情况下,在该插接孔200的位置处进行焊接时,其焊接时间可大幅缩短,例如在原插件孔20的孔径下的焊接时间需要12.5秒时,在改变为该插接孔200的孔径下的焊接时间可缩短变为7.5至6秒;在原插件孔20的孔径下的焊接时间需要5.5秒时,在改变为该插接孔200的孔径下的焊接时间可缩短变为3.5秒。

27.再者,传统电路板的插件孔20周缘具有大面积的焊接垫(铜箔)时会因散热较快而使焊锡流动慢,并导致焊接速度也会变慢。另一方面,当本发明的插接孔200具有较大面积的第一焊接垫41及第二焊接垫42(较大面积的铜箔)时,其焊接速度明显比传统更快。

28.此外,电子组件2的接脚3在插入传统电路板的插件孔20时会有部分歪斜的情形而造成接脚3与导电层40间的空隙不均,导致该接脚3在空隙较小之处无法确实地完成焊接。另一方面,本发明的插接孔200可借由扩充孔30的设置而让焊锡流至接脚3空隙较小之处,借以提高接脚3的焊接优良率。

29.综上,本发明的电路板1是通过该插接孔200的设置而加快焊接速度,借以节省焊接时间,并增加可靠度及提高优良率。

30.以上所述仅为本发明的较佳实施例,并非用以限定本发明的专利范围,其他运用本发明的专利精神的等效变化,均应俱属本发明的专利范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1