多相位时钟产生器及其相关频率合成器的制作方法

1.本发明涉及一种多相位时钟产生器及其相关电路,且特别涉及一种开回路(open loop)的多相位时钟产生器及其相关频率合成器。

背景技术:

2.众所周知,所有的电子芯片都需要根据时钟信号来运作。以人工智能芯片(ai chip)为例,人工智能芯片中包括类神经网络系统。而类神经网络系统由众多的神经元(neuron)以及众多的神经元连接权重(neuron connection weight)所构成,用来执行各种检测与辨识的行为。一般来说,类神经网络系统中的神经元连接权重会被记录在模拟式非易失性存储器(analog nvm)中。也就是说,模拟式非易失性存储器非常适合运用在人工智能芯片。再者,人工智能芯片的运算速度可由时钟信号的频率来决定,而频率合成器(frequency synthesizer)可以产生各种频率不同的时钟信号。

3.基本上,已知的频率合成器可由闭回路的(close loop)锁相回路(phase lock loop circuit,简称pll)或者延迟锁定回路(delay lock loop circuit,简称dll)搭配组合逻辑电路(combinational logic circuit)来完成。

4.请参照图1a与图1b,其所绘示为已知锁相回路及其频率合成器与相关信号示意图。频率合成器100包括一锁相回路与一组合逻辑电路190。其中,锁相回路为一种多相位时钟产生器。锁相回路包括一相位频率检测器(phase frequency detector,简称pfd)110、一电荷泵(charge pump)120、回路滤波器(loop filter)130、一电压控制振荡器(voltage control oscillator,简称vco)140、一分频器(frequency divider)150。

5.相位频率检测器(pfd)110接收一参考时钟信号(reference clock signal)ckr与分频时钟信号(divided clock signal)ckd并产生一控制信号sctrl至电荷泵120。

6.电荷泵120中包括一充电路径(charging path)与一放电路径(discharging path)。控制信号sctrl可以控制充电路径或者放电路径上来产生一驱动电流(driving current)ic至回路滤波器130。

7.回路滤波器130为一rc电路,根据电荷泵120产生的驱动电流ic来对rc电路进行充放电控制(charge/discharge control),并产生调整电压(tuned voltage)vtune至压控振荡器(vco)140。

8.压控振荡器(vco)140接收调整电压vtune,并产生相同频率的多个调整时钟信号(tuned clock signal)ckt_1~ckt_n。再者,当调整电压vtune改变时,压控振荡器(vco)即改变调整时钟信号ckt_1~ckt_n的频率。举例来说,n等于4,压控振荡器(vco)140产生4个调整时钟信号ckt_1~ckt_4,每个调整时钟信号ckt_1~ckt_4之间的相位相差90度。

9.分频器(frequency divider)150,接收其中一个调整时钟信号ckt_n并且对调整时钟信号ckt_n进行分频的动作,并产生分频时钟信号ckd至相位频率检测器(pfd)110。基本上,假设参考时钟信号ckf的频率为fref,则调整时钟信号ckt_1~ckt_n的调整频率ft为参考频率fref的n倍(亦即,ft=n

×

fref),其中n为分频器150的分频值。

10.再者,组合逻辑电路190接收调整时钟信号ckt_1~ckt_n,并进行逻辑运算后,可以产生一输出时钟信号ckout。其中,组合逻辑电路190中包括多个逻辑电路,根据调整时钟信号ckt_1~ckt_n来产生的输出时钟信号ckout,其输出频率fout可为调整频率ft的特定倍数。

11.举例来说,压控振荡器(vco)140产生4个调整时钟信号ckt_1~ckt_4。因此,如图1b所示,每个调整时钟信号ckt_1~ckt_4之间的相位相差90度。再者,组合逻辑电路190可为异或门。将调整时钟信号ckt_1、ckt_2输入组合逻辑电路190后,即可产生输出时钟信号ckout,且其输出频率fout可为调整频率ft的2倍。

12.当然,组合逻辑电路190并不限定于异或门,在此领域的技术人员也可以利用各种逻辑门的结合成为组合逻辑电路,用来产生各种频率的多个输出时钟信号。

13.请参照图2,其所绘示为已知延迟锁定回路及其相关频率合成器示意图。频率合成器200包括一延迟锁定回路与一组合逻辑电路290。其中,延迟锁定回路为一种多相位时钟产生器。延迟锁定回路包括一相位检测器(phase detector,简称pd)210、一电荷泵220、回路滤波器230、一电压控制延迟线电路240。

14.相位检测器(pfd)210接收一参考时钟信号(reference clock signal)ckr与调整时钟信号ckt_n并产生一控制信号sctrl至电荷泵220。电荷泵220根据控制信号sctrl来产生一驱动电流ic至回路滤波器230。回路滤波器230根据驱动电流ic来产生调整电压vtune至电压控制延迟线电路240。

15.电压控制延迟线电路240接收参考时钟信号ckr与调整电压vtune,并产生相同频率的多个调整时钟信号(tuned clock signal)ckt_1~ckt_n。相同地,当调整电压vtune改变时,电压控制延迟线电路240即改变调整时钟信号ckt_1~ckt_n的延迟时间。举例来说,n等于4,电压控制延迟线电路240产生4个调整时钟信号ckt_1~ckt_4,每个调整时钟信号ckt_1~ckt_4之间的相位相差90度。

16.另外,组合逻辑电路290接收调整时钟信号ckt_1~ckt_n,并进行逻辑运算后,可以产生输出时钟信号ckout。其中,组合逻辑电路290中包括多个逻辑电路,根据调整时钟信号ckt_1~ckt_n来产生的输出时钟信号ckout,其输出频率fout可为调整频率ft的特定倍数。

技术实现要素:

17.本发明目的在于提出一种开回路(open loop)的多相位时钟产生器及其相关频率合成器。

18.本发明涉及一种多相位时钟产生器,包括:一电流镜,包括一接收端,一第一镜射端与一第二镜射端;一电压控制器,该电压控制器连接至该电流镜的该接收端,该电压控制器的一反馈端连接至该电流镜的该第一镜射端;一拟态电阻电路,该拟态电阻电路的一第一端连接至该电流镜的该第一镜射端,该拟态电阻电路的一第二端连接至一接地端;以及一第一延迟电路,连接至该电流镜的该第二镜射端,其中该第一延迟电路的一输入端接收一第一输入时钟信号,该第一延迟电路的一输出端产生一第一延迟时钟信号;其中,该拟态电阻电路包括一第一电容器、一第一开关、一第二开关、一第三开关与一第四开关,该第一开关的一第一端连接至该电流镜的该第一镜射端,该第一开关的一第二端连接至该第一电

容器的一第一端,该第二开关的一第一端连接至该电流镜的该第一镜射端,该第二开关的一第二端连接至该第一电容器的一第二端,该第三开关的一第一端连接至该接地端,该第三开关的一第二端连接至该第一电容器的该第一端,该第四开关的一第一端连接至该接地端,该第四开关的一第二端连接至该第一电容器的该第二端;其中,第一开关与该第四开关受控于一第一控制时钟信号且第二开关与该第三开关受控于一第二控制时钟信号。

19.为了对本发明的上述及其他方面有更佳的了解,下文特举优选实施例,并配合附图,作详细说明如下:

附图说明

20.图1a与图1b为已知锁相回路及其频率合成器与相关信号示意图。

21.图2为已知延迟锁定回路及其相关频率合成器示意图。

22.图3a至图3d为拟态电阻电路、控制时钟信号及拟态电阻电路运作示意图。

23.图4为利用拟态电阻电路所设计的频率转电流电路。

24.图5a与图5b为本发明的多相位时钟产生器的第一实施例以及时钟信号之间的关系示意图。

25.图5c为临限电压产生器。

26.图6为本发明的多相位时钟产生器的第二实施例。

27.图7为本发明的频率合成器。

28.图8为运用于图7中组合逻辑电路的另一范例。

29.【符号说明】

30.100,200:频率合成器

31.110:位频率检测器

32.120,220:电荷泵

33.130,230:回路滤波器

34.140:电压控制振荡器

35.150:分频器

36.190,290,690,790:组合逻辑电路

37.210:相位检测器

38.240:电压控制延迟线电路

39.300:拟态电阻电路

40.400:频率转电流电路

41.410:电流镜

42.420:电压控制

43.430:负载

44.450:运算放大器

45.500,600:多相位时钟产生器

46.510,520,710,720:延迟电路

47.512,514,516,522,524:反相器

48.700:频率合成器

49.791:或门

50.793,795,797,799:与非门

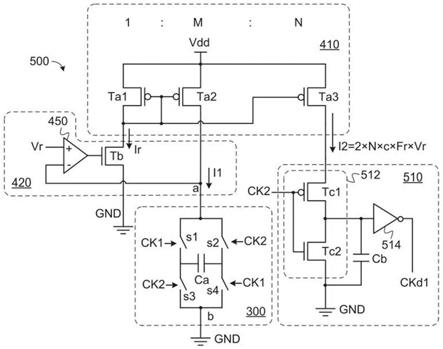

具体实施方式

51.首先,本发明先介绍拟态电阻电路(pseudo-resistor circuit)。请参照图3a至图3d,其所绘示为拟态电阻电路、控制时钟信号(control clock signal)及拟态电阻电路运作示意图。拟态电阻电路300包括:电容器ca与四个开关s1~s4。其中,节点a作为拟态电阻电路300的第一端,节点b作为拟态电阻电路300的第二端。再者,拟态电阻电路300的二端连接至电源电压vcc。

52.开关s1的第一端连接至节点a,开关s1的第二端连接至电容器ca的第一端。开关s2第一端连接至节点a,开关s2的第二端连接至电容器ca的第二端。开关s3的第一端连接至节点b,开关s3的第二端连接至电容器ca的第一端。开关s4的第一端连接至节点b,开关s4的第二端连接至电容器ca的第二端。其中,开关s1与s4根据第一控制时钟信号ck1运作,开关s2与s3根据第二控制时钟信号ck2运作。

53.如图3b所示,第一控制时钟信号ck1与第二控制时钟信号ck2互补。另外,第一控制时钟信号ck1与第二控制时钟信号ck2的频率相同且周期为tr。举例来说,第一控制时钟信号ck1可由石英振荡器(quartz oscillator)所产生。

54.假设4个开关s1~s4在高电平时为闭合状态(close state),低电平时为打开状态(open state)。如图3c所示,当第一控制时钟信号ck1为高电平且第二控制时钟信号ck2为低电平时,开关s1与s4为闭合状态且开关s2与s3为打开状态。电流ix流经拟态电阻电路300内部的节点a、开关s1、电容器ca、开关s4、节点b,且电流ix=c

×

vcc/tr。其中,电容器ca的电容值为c。

55.同理,如图3d所示,当第一控制时钟信号ck1为低电平且第二控制时钟信号ck2为高电平时,开关s1与s4为打开状态且开关s2与s3为闭合状态。电流iy流经拟态电阻电路300内部的节点a、开关s2、电容器ca、开关s3、节点b,且电流iy=c

×

vcc/tr。

56.因此,流经拟态电阻电路300的总电流为i,且i=ix+iy=2

×

c

×

vcc/tr。而拟态电阻电路300的等效电阻req为,req=vcc/i=1/(2

×

c

×

fr)。其中,fr为第一控制时钟信号ck1的频率,且fr=1/tr。根据以上的说明可知,当电容器ca的电容值c为固定值时,拟态电阻电路300的等效电阻值req相关于第一控制时钟信号ck1的频率fr。举例来说,第一控制时钟信号ck1的频率fr越高时,拟态电阻电路300的等效电阻值req越小;第一控制时钟信号ck1的频率fr越低时,拟态电阻电路300的等效电阻值req越大。

57.请参照图4,其所绘示为利用拟态电阻电路所设计的频率转电流电路(frequency-to-current converting circuit)。频率转电流电路400包括:电流镜410、拟态电阻电路300、电压控制器420与负载(load)430。其中,拟态电阻电路300的结构与运作原理相同于图3a,此处不再赘述。

58.电流镜410包括晶体管ta1、ta2、ta3。晶体管ta1的第一漏/源极端(drain/source terminal)接收电源电压vdd,晶体管ta1的第二漏/源极端为电流镜410的接收端(receiving terminal)。晶体管ta2的第一漏/源极端接收电源电压vdd,晶体管ta2的第二漏/源极端为电流镜410的第一镜射端(mirroring terminal),晶体管ta2的栅极端连接至

晶体管ta1的栅极端。晶体管ta3的第一漏/源极端接收电源电压vdd,晶体管ta3的第二漏/源极端为电流镜410的第二镜射端,晶体管ta3的栅极端连接至晶体管ta1的栅极端。另外,三个晶体管ta1、ta2、ta3长宽比(aspect ratio)的比例为1:m:n。

59.再者,电流镜410的第一镜射端连接于拟态电阻电路300的第一端(节点a),电流镜410的接收端连接至电压控制器420,电流镜410的第二镜射端连接至负载430的第一端。另外,拟态电阻电路300的第二端(节点b)连接至接地端gnd,负载430的第二端连接至接地端gnd。

60.电压控制器420包括一运算放大器450、一控制晶体管tb。运算放大器450的正输入端接收一控制电压vr,运算放大器450的负输入端作为电压控制器420的反馈端(feedback terminal),其连接至电流镜400的第一镜射端,运算放大器450的输出端连接至控制晶体管tb的栅极端。控制晶体管tb的第一漏/源极端连接至电流镜410的接收端,控制晶体管tb的第二漏/源极端连接至接地端gnd。

61.当频率转电流电路400运作时,电流镜410的接收端会接收电流ir。其中,ir=vr/req=2

×

c

×

fr

×

vr。由于晶体管ta1、ta2、ta3的长宽比为1:m:n,所以电流镜410的第一镜射端产生电流i1,第二镜射端产生电流i2。其中,i1=2

×

m

×

c

×

fr

×

vr,i2=2

×

n

×

c

×

fr

×

vr。再者,电容器ca的电容值c,第一控制时钟信号ck1的频率为fr。

62.根据以上的说明可知,电流镜410的第二镜射端可产生电流i2至负载430,且电流i2相关于第一控制时钟信号ck1的频率fr。举例来说,电容器ca的电容值c与控制电压vr为固定值。当第一控制时钟信号ck1的频率fr越高时,电流i2越大。当第一控制时钟信号ck1的频率fr越低时,电流i2越小。

63.再者,根据上述的频率转电流电路400的特性,更可以设计多相位时钟产生器及其相关的频率合成器。

64.请参照图5a与图5b,其所绘示为本发明的多相位时钟产生器的第一实施例以及时钟信号之间的关系示意图。多相位时钟产生器500包括:电流镜410、拟态电阻电路300、电压控制器420与一延迟电路510。其中,电流镜410、拟态电阻电路300与电压控制器420的结构与运作原理相同于图4,此处不再赘述。

65.再者,延迟电路510包括二反相器(inverter)512、514与电容器cb1。延迟电路510有一输入端与一输出端。其中,反相器512的输入端作为延迟电路510的输入端,反相器514的输出端作为延迟电路510的输出端。

66.反相器512的输入端接收第二控制时钟信号ck2,反相器512的输出端连接至反相器514的输入端,反相器514的输出端产生延迟时钟信号(delayed clock signal)ckd1。再者,电容器cb1的二端分别连接至反相器512的输出端以及接地端gnd。反相器512的二个电源端(power terminal)分别连接至电流镜410的第二镜射端以及接地端gnd。

67.再者,反相器512包括晶体管tc1、tc2。晶体管tc1的第一漏/源极端连接至电流镜410的第二镜射端,晶体管tc1与tc2的栅极端接收第二控制时钟信号ck2,晶体管tc2的第一漏/源极端连接至晶体管tc1的第二漏/源极端以及反相器514的输入端,晶体管tc2的第二漏/源极端连接至接地端gnd。

68.根据本发明的第一实施例,电压控制器420接收的控制电压vr相同于反相器514的临限电压(threshold voltage)或称为转态电压(transition voltage)。再者,电容器ca的

尺寸(size)为电容器cb1的m倍。亦即,电容器ca的电容值为c时,电容器cb1的电容值为c/m。以下介绍延迟电路510的运作。

69.当第二控制时钟信号ck2由高电平转换为低电平时,晶体管tc1开启(turn on)且晶体管tc2关闭(turn off),电容器cb1接收电流i2开始充电。当电容器cb1充电至控制电压vr(亦即,反相器514的临限电压)时,反相器514产生的延迟时钟信号ckd1由高电平转换为低电平。

70.另外,当第二控制时钟信号ck2由低电平转换为高电平时,晶体管tc1关闭且晶体管tc2开启,电容器cb1放电至接地电压(0v),且反相器514产生的延迟时钟信号ckd1由低电平转换为高电平。

71.基本上,电容器cb1充电至控制电压vr需要δtf的时间。此时,电容器cb1存储的电荷量q为(c/m)

×

vr。因此,

72.其中,tr为第二控制时钟信号ck2的周期,n为电流镜410中电经体ta1与ta3的长宽比的关系,m为电容器ca与cb1的尺寸关系。

73.如图5b所示,第二控制时钟信号ck2与延迟时钟信号ckd1的下降沿(falling edge)会由特定的延迟时间δtf,且延迟时间δtf相关于tr、n、m。换句话说,本发明的多相位时钟产生器500可准确地控制延迟时间δtf,且延迟时钟信号ckd1不会受到工艺(process)、电压(voltage)、温度(temperature)的影响。

74.为了让电压控制器420产生的控制电压vr相同于反相器514的临限电压,可以利用相同构造的反相器来产生临限电压。如图5c所示,其为临限电压产生器。临限电压产生器包括一反相器516,反相器516与反相器514有相同的构造。反相器516的输入端连接至反相器516的输出端。再者,反相器516的二个电源端分别接收电源电压vdd以及接地端gnd。如此,反相器516的输出端即产生临限电压,并作为控制电压vr。

75.另外,第一实施例中的延迟电路510中,反相器512接收第二控制时钟信号ck2。实际上,本发明并不限定于此,在此领域的技术人员也可以设计反相器512接收第一控制时钟信号ck1,也可以达成本发明的效果。

76.再者,由于第一控制时钟信号ck1与延迟时钟信号ckd1之间有固定的延迟时间δtf,因此将第一控制时钟信号ck1与延迟时钟信号ckd1输入组合逻辑电路(未绘示),后即可产生特定频率的输出时钟信号ckout。

77.请参照图6,其所绘示为本发明的多相位时钟产生器的第二实施例。多相位时钟产生器600包括:电流镜410、拟态电阻电路300、电压控制器420与多个延迟电路510、520。其中,电流镜410、拟态电阻电路300与电压控制器420的结构与运作原理相同于图4,此处不再赘述。另外,每个延迟电路510、520的结构相同,此处不再赘述。

78.根据本发明的第二实施例,多个延迟电路510、520串接形成开回路(open loop)的延迟线电路(delay line circuit)。亦即,第一个延迟电路510的输入端接收第二控制时钟信号ck2,而后一个延迟电路520的输入端连接至前一个延迟电路510的输出端,依此类推。再者,每个延迟电路510、520会产生对应的延迟时钟信号ckd1、ckd2。因此,当多相位时钟产生器600正常运作时,延迟电路510、520产生的延迟时钟信号ckd1、ckd2之间会有固定的相位关系(phase relationship)。当然,在延迟线电路(delay line circuit)中可包括二个

以上的延迟电路串接。

79.举例来说,多相位时钟产生器600中包括4个延迟电路形成延迟线电路(delay line circuit)。第一个延迟电路产生第一延迟时钟信号ckd1,其下降沿落后第二控制时钟信号ck2的下降沿一个延迟时间δtf。第二个延迟电路产生第二延迟时钟信号ckd2,其下降沿落后第一延迟时钟信号ckd1的下降沿一个延迟时间δtf。第三个延迟电路产生第三延迟时钟信号ckd3,其下降沿落后第二延迟时钟信号ckd2的下降沿一个延迟时间δtf。第四个延迟电路产生第四延迟时钟信号ckd4,其下降沿落后第三延迟时钟信号ckd3的下降沿一个延迟时间δtf。

80.再者,如图6所示,将相位时钟产生器600结合组合逻辑电路690后即形成频率合成器。举例来说,组合逻辑电路690接收所有延迟时钟信号ckd1、ckd2并进行逻辑运算后,可以产生一个特定频率的输出时钟信号ckout。举例来说,由于延迟时间δtf为,δtf=tr/(2

×

n

×

m)。因此,可以设计周期为(2

×

δtf)的输出时钟信号ckout,亦即频率为(n

×

m

×

fr)的输出时钟信号ckout。当然,组合逻辑电路690也可以根据所有延迟时钟信号ckd1、ckd2来产生其他不同频率的多个输出时钟信号。

81.请参照图7,其所绘示为本发明的频率合成器。频率合成器700包括:电流镜410、拟态电阻电路300、电压控制器420、二个延迟电路710、720以及一组合逻辑电路790。其中,电流镜410、拟态电阻电路300与电压控制器420的结构与运作原理相同于图5,此处不再赘述。

82.再者,本发明利用二个延迟电路710、720搭配组合逻辑电路790形成张弛振荡器(relaxation oscillator)。其中,二个延迟电路710、720的输出端分别产生延迟时钟信号ckd1、ckd2至组合逻辑电路790,而组合逻辑电路790分别产生输出时钟ckout1、ckout2至二个延迟电路710、720的输入端。

83.其中,延迟电路710、720的结构相同,以下仅介绍延迟电路720。延迟电路720包括二反相器522、524与电容器cb2。延迟电路720有一输入端与一输出端。其中,反相器522的输入端作为延迟电路720的输入端,反相器523的输出端作为延迟电路720的输出端。再者,反相器522的输出端连接至反相器524的输入端,电容器cb1的二端分别连接至反相器522的输出端以及接地端gnd。反相器522的二个电源端分别连接至电流镜410的第二镜射端以及接地端gnd。

84.再者,反相器522包括晶体管tc3、tc4。晶体管tc3的第一漏/源极端连接至电流镜410的第二镜射端,晶体管tc3与tc4的栅极端为反相器522的输入端,晶体管tc4的第一漏/源极端连接至晶体管tc3的第二漏/源极端以及反相器524的输入端,晶体管tc4的第二漏/源极端连接至接地端gnd。

85.组合逻辑电路790包括与非门(nand gate)793、795。其中,与非门793的第一输入端接收延迟时钟信号ckd2,与非门793的第二输入端连接至与非门795的输出端,与非门795的第一输入端接收延迟时钟信号ckd1,与非门795的第二输入端连接至与非门793的输出端,与非门793的输出端产生延迟信号ckout2,与非门795的输出端产生延迟信号ckout1。

86.当频率合成器700在运作时,二个延迟电路710、720搭配组合逻辑电路790形成张持振荡器(relaxation oscillator)。组合逻辑电路790产生互补的输出时钟ckout1、ckout2。再者,由于延迟时间δtf为,δtf=tr/(2

×

n

×

m)。因此,组合逻辑电路790产生的输出时钟ckout1、ckout2,其频率为(n

×

m

×

fr)。

87.当然,本发明订不限定于组合逻辑电路790的实际电路结构。在此领域的技术人员可以利用其他的组合逻辑电路来产生输出时钟信号。请参照图8,其所绘示为运用于图7频率合成器700中组合逻辑电路的另一范例。

88.组合逻辑电路790包括或门(or gate)791与与非门(nand gate)793、795、797、799。其中,或门791的第一输入端接收延迟时钟信号ckd1,或门791的第二输入端接收延迟时钟信号ckd2,或门791的输出端连接至与非门797的第一输入端,与非门793的第一输入端接收延迟时钟信号ckd2,与非门793的第二输入端连接至与非门795的输出端以及与非门799的第一输入端,与非门795的第一输入端接收延迟时钟信号ckd1,与非门795的第二输入端连接至与非门793的输出端以及与非门797的第二输入端,与非门799的第二输入端接收高电平(hi),与非门797的输出端产生延迟信号ckout1,与非门799的输出端产生延迟信号ckout2。

89.在组合逻辑电路790中,或门791根据延迟时钟信号ckd1、ckd2的关系来产生重置信号rst并重置组合逻辑电路790。相同地,组合逻辑电路790也可产生频率为(n

×

m

×

fr)的输出时钟ckout1、ckout2,且输出时钟ckout1、ckout2互补。

90.由以上的说明可知,本发明提出一种多相位时钟产生器及其相关频率合成器。利用拟态电阻电路的特性来设计多相位时钟产生器,可以产生特定相位差的延迟时钟信号。而本发明的多相位时钟产生器可准确地控制延迟时间δtf,用以控制延迟时钟信号之间的相位差,且延迟时钟信号不会受到工艺(process)、电压(voltage)、温度(temperature)的影响。换句话说,频率合成器所产生的输出时钟信号也不会受到工艺(process)、电压(voltage)、温度(temperature)的影响。

91.综上所述,虽然本发明已以优选实施例公开如上,然其并非用以限定本发明。本发明所属领域技术人员,在不脱离本发明的精神和范围内,当可作各种的更动与润饰。因此,本发明的保护范围当视所附权利要求书界定范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1