一种带异步置位复位的CMOS混合型边沿忆阻D触发器电路的制作方法

一种带异步置位复位的cmos混合型边沿忆阻d触发器电路

技术领域

[0001]

本发明属于电路设计技术领域,涉及一种忆阻d触发器电路,具体涉及一种带异步置位复位的cmos混合型边沿忆阻d触发器电路,实现上升沿触发、具有非易失性的特点和异步置位复位功能。

背景技术:

[0002]

忆阻器最早于1971年被提出,作为新型器件已经被广泛研究,针对忆阻器的非易失性和滞回等特性,将忆阻器应用于神经网络、存储器、数字逻辑电路等领域的研究已经相对比较全面。但是由于纳米技术存在制作困难和成本高等不足,忆阻器还未作为一个商业产品走向市场,目前主要利用忆阻器的各种等效电路模型和数学模型来设计电路,其中阈值型忆阻器模型可以使忆阻器工作在高低阻态上,类似开关的特性,非常适合应用于数字逻辑电路,比如与、或、异或等忆阻逻辑运算单元,以及加法器、乘法器等忆阻组合逻辑电路,但是目前对忆阻时序逻辑电路特别是触发器电路的研究还较少。

技术实现要素:

[0003]

针对现在技术和研究成本上所存在的问题,本发明提供了一种带异步置位复位的cmos混合型边沿忆阻d触发器电路,其中的忆阻器采用biolek阈值型忆阻器,可对该模型的最大阻值r

off

、最小阻值r

on

、参数β(用于控制忆阻器模型的阻值变化速率,一般为10

13

)、阈值电压v

t

等关键参数进行直接调整。

[0004]

本发明解决技术问题所采取的技术方案如下:

[0005]

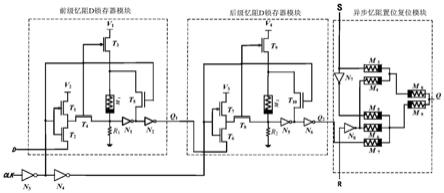

一种带异步置位复位的cmos混合型边沿忆阻d触发器电路,包括前级忆阻d锁存器模块、异步忆阻置位复位模块和后级忆阻d锁存器模块。其中,前级忆阻d锁存器模块包括mos管t1、t2、t3、t4和t5,忆阻器m1,电阻r1以及cmos反相器n1和n2;后级忆阻d锁存器模块包括mos管t6,t7,t8,t9和t

10

,忆阻器m2,电阻r2以及cmos反相器n5和n6;异步忆阻置位复位模块包括忆阻器m3、m4、m5、m6、m7、m8和m9以及反相器n7和n8;用于时钟输入的cmos反相器n3和n4;其中mos管t2、t4、t5、t6、t8和t

10

为nmos晶体管,t1、t3、t7和t9为pmos晶体管,m1、m2、m3、m4、m5、m6、m7、m8和m9均为biolek阈值型忆阻器。在前级忆阻d锁存器模块内,t1、t2、t3、t4和t5的栅极连接反相器n3的输出端和n4的输入端相连接作为前级忆阻d锁存器模块的时钟输入口;t2的源极作为前级忆阻d锁存器模块的信号输入端也即整个边沿忆阻d触发器的输入端d,t2的漏极连接t1和t4的漏极;t1的源极连接直流电压v2;t4的源极连接电阻r1的一端、忆阻器m1的负端和反相器n1的输入端;t3的源极连接直流电压v1,漏极连接忆阻器m1的正端和t5的源极;t5的漏极连接反相器n1的输出端和反相器n2的输入端;电阻r1的另一端连接地;反相器n2的输出端作为前级忆阻器d锁存器模块的输出端q1;在后级忆阻d锁存器模块内,t6、t7、t8、t9和t

10

的栅极连接反相器n4的输出端作为后级忆阻d锁存器模块的时钟输入口;mos管t6的源极作为后级忆阻d锁存器模块的信号输入口连接前级忆阻d锁存器的输出端q1(反相器n2的输出端),t6的漏极连接t7和t8的漏极;mos管t7的源极连接直流电压v3;mos管t8的源极连接电阻

r2的一端、忆阻器m2的负端和反相器n5的输入端;mos管t9的源极连接直流电压v4,漏极连接忆阻器m2的正端和mos管t

10

的源极;mos管t

10

的漏极连接反相器n5的输出端和反相器n6的输入端;电阻r2的另一端连接地;反相器n6的输出端作为后级忆阻d锁存器模块的信号输出端q2。异步忆阻置位复位模块作为d触发器的外加电路,其连接为:反相器n7的输入端与忆阻器m3的正端连接在一起作为置位信号s的输入端,n7的输出端连接忆阻器m5的正端;反相器n8的输入端作为复位信号r的输入端,n8的输出端连接忆阻器m6和m4的正端;忆阻器m7的正端连接后级忆阻d锁存器模块的输出端q2(反相器n6的输出端);忆阻器m3和m4的负端连接连接忆阻器m8的负端;忆阻器m5、m6和m6的负端连接连接忆阻器m9的负端;忆阻器m8和m9的负端连接作为整个边沿忆阻d触发器最终输出端q。

[0006]

更进一步地,电阻r1的阻值需远远大于忆阻器m1设定的最大阻值且远远小于设定的最小阻值;电阻r2的阻值需远远大于忆阻器m2设定的最大阻值且远远小于设定的最小阻值。

[0007]

更进一步地,电压v1、v2、v3和v4为直流电压,v2和v3设定高电平,直流电压v1和v4的电压小于忆阻器m1和m4所设定的阈值电压。

[0008]

更进一步地,置位信号s和复位信号r不能同时1。

[0009]

与现有技术相比,本发明提出了一种带异步置位复位的cmos混合型边沿忆阻d触发器,其设计思路是将2个由cmos与忆阻器混合构成的忆阻d锁存器级联构成,并且添加由忆阻器构成的异步置位复位电路,电路结构简单,功能齐全,系统的集成度高。前级忆阻d锁存器模块和后级忆阻d锁存器模块由忆阻器与cmos混合构成,电路具有非易失性。异步忆阻置位复位模块由忆阻器构成的与门和或门构建而成,该模块使d触发器具有异步置位和复位的功能。本发明采用biolek阈值型忆阻器模型,利用该阈值型忆阻器与cmos实现了带异步置位复位的混合型边沿忆阻器d触发器电路具有非易失性,拥有异步置位和复位功能。

附图说明

[0010]

图1是本发明的电路结构框图。

[0011]

图2是本发明所采用忆阻器的电路符号。

[0012]

图3是本发明所采用阈值型忆阻器模型的电流-电压曲线图。

[0013]

图4是本发明的具体电路结构图。

[0014]

图5是本发明的仿真波形图。

具体实施方式

[0015]

为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及发明实例,对本发明进一步说明。

[0016]

图1是本发明的电路结构框图,本发明将前级忆阻d锁存、后级忆阻d锁存器和忆阻异步置位复位电路各作为一个模块,将这3个模块依次连接起来构建带异步置位复位的cmos混合型边沿忆阻d触发器。如图1所示,构建边沿忆阻d触发器的方式是将前级忆阻d锁存器模块和后级d锁存器模块通过级联的方式构成,本发明还为使整个d触发器添加了完全由忆阻器构成的异步置位复位电路,整个d触发器使用的器件数量大大减少,电路结构简单,可以极大提高速度并降低功耗。

[0017]

图2是本发明采用biolek提出的阈值型忆阻器模型的电路符号,图3是忆阻器在外加正弦激励信号下的电流-电压波形,其中忆阻器相关参数设定为:β=10

13

、r

off

=100kω、r

on

=800ω、v

t

=4.5v;外加正弦电压激励相关参数设定为:幅度为6v,频率为100hz。图2可以看出,该忆阻器模型具有滞回特性和阈值特性,正负电压下都各具有1个阈值,+v

t

和-v

t

。当忆阻器外加的正向激励电压大于正向阈值+v

t

时忆阻器会成高阻态;当反向激励电压大于负向阈值-v

t

时忆阻器会转变成低阻态,且在上述变化后若电压不变或者变化范围小于阈值电压,则忆阻器将会保持之前的阻态,直到忆阻器两端所加的激励电压差大于阈值。本发明中前级忆阻d锁存器模块和后级忆阻d锁存器模块中的忆阻器模型都承担起了记忆存储的作用。而异步忆阻置位复位模块则是利用忆阻器构成与门和或门,实现异步置位和复位的功能。

[0018]

图4是本发明基于带异步置位复位的cmos混合型边沿忆阻d触发器具体电路图。电压参数设定为:v2=v3=8v,v1=v4=3.4v;忆阻器参数设定为:m1和m2:β=10

13

、r

off

=100kω、r

on

=800ω、v

t

=3.5v;m3、m4、m5、m6、m7、m8和m9:β=10

13

、r

off

=100kω、r

on

=800ω、v

t

=0.5v;其他相关参数设定为:r1=r2=10kω。如图3所示,该边沿忆阻d触发器包括9个忆阻器m1、m2、m3,m4、m5、m6、m7、m8和m9定值电阻r1、r2(r

on

<<r1,r2<<r

off

,其中r

on

和r

off

分别为忆阻器设定的最低阻值和最高阻值),mos管t2、t4、t5、t6、t8和t

10

为nmos晶体管,t1、t3、t7和t9为pmos晶体管,m1、m2、m3、m4、m5、m6、m7、m8和m9均为biolek阈值型忆阻器。t1、t2、t3、t4和t5的栅极连接反相器n3的输出端和n4的输入端;t2的源极作为整个边沿忆阻d触发器的输入端d,t2的漏极连接t1和t4的漏极;t1的源极连接直流电压v2;t4的源极连接电阻r1的一端、忆阻器m1的负端和反相器n1的输入端;t3的源极连接直流电压v1,漏极连接忆阻器m1的正端和t5的源极;t5的漏极连接反相器n1的输出端和反相器n2的输入端;电阻r1的另一端连接地;反相器n2的输出端连接mos管t6的源极;t6、t7、t8、t9和t

10

的栅极连接反相器n4的输出端;mos管t6的源极连接反相器n2的输出端,t6的漏极连接t7和t8的漏极;mos管t7的源极连接直流电压v3;mos管t8的源极连接电阻r2的一端、忆阻器m2的负端和反相器n5的输入端;mos管t9的源极连接直流电压v4,漏极连接忆阻器m2的正端和mos管t

10

的源极;mos管t

10

的漏极连接反相器n5的输出端和反相器n6的输入端;电阻r2的另一端连接地;反相器n6的输出端连接忆阻器m7的正端。反相器n7的输入端连接置位信号s,输出端连接忆阻器m5的正端;反相器n8的输入端连接复位端r,输出端连接忆阻器m6和m4的正端;忆阻器m3的正端连接置位信号s;忆阻器m7的正端连接反相器n6的输出端;忆阻器m3和m4的负端连接连接忆阻器m8的负端;忆阻器m5、m6和m6的负端连接连接忆阻器m9的负端;忆阻器m8和m9的负端连接作为整个边沿忆阻d触发器最终输出端q;

[0019]

下面参照图5所示的pspice仿真波形图具体来解释本发明的带异步置位复位的混合型边沿忆阻d触发器工作原理。其中输入信号d、时钟输入信号clk,置位信号s和复位信号r均为方波。本发明的边沿忆阻d触发器工作原理为:当clk=0时,mos管t2、t4和t5处于打开状态,mos管t1和t3处于关断状态,此时输入信号d从q1端输出,由于反相器n1的存在,忆阻器m1两端电压差大于忆阻器阈值电压,此时忆阻器m1会根据输入信号d的状态而存储相应状态(若d=1,则m1为低阻态即r

on

;若d=0,则忆阻器为高阻态即r

off

),当clk由0变为1时,mos管t2、t4和t5处于关断状态,mos管t1和t3处于打开状态,电压v1由于小于忆阻器所设定的阈值电压,通过v1可以读出忆阻器m1此前存储的数据(若m1为高阻态则读出0,m1为低阻态则读出

1),然后经过反相器n1和n2从q2端输出。以上为前级忆阻器d锁存器工作原理,后级忆阻d锁存器工作原理与前级一样。将这两个锁存器级联可构成上升沿触发的d触发器,其原理为:当clk=0时,前级忆阻d锁存器输入端打开忆阻器用于存储当前的转态,此时q1=d,后级忆阻d锁存器输入端关闭,mos管t7和t8打开,通过电压v4读出此前存储的状态并且通过q2端输出。当上升沿到来时前级忆阻d锁存器输入端关闭(t2、t4和t5关闭),后级忆阻d锁存器输入端打开(t6、t8和t

10

打开),由电压v1读出m1中存储的状态,然后从q1端输入到后级忆阻器d锁存器中并且从q2端输出,即q2=d。忆阻异步置位复位电路工作原理为:忆阻器m3和m4构成二输入与门,忆阻器m5、m6和m7构成三输入与门,忆阻器m8和m9构成二输入或门,因此整个忆阻异步置位复位电路的逻辑输出表达式为(s和r不能同时为1),当s=1,r=0时,由忆阻器m3和m4构成的二输入与门输出为1(m3和m4的负端),由忆阻器m8和m9构成二输入或门一端(m8的负端)为1,此时无论上升沿是否到来,输出端q=1,起到了异步置位的功能;当s=0,r=1时,由忆阻器m3和m4构成的二输入与门输出为0,由忆阻器m5、m6和m7构成三输入与门输出为0,此时忆阻器m8和m9构成二输入或门两端(m8的负端,m9的负端)同时为0;此时无论上升沿是否到来,输出端q=0起到异步复位的功能。在图5中,置位信号s在0-6us内为1,复位信号r在12.5-14us内为1,从图5中可以看出0-6us时输出端q一直为1而不随输入信号变化和上升沿到来的影响;6-12.5us时输出端q在clk上升沿到来时,输出信号q与输入信号d一致,符合d触发器定义;12.5-14us时输出端q一直为0,而不受输入信号d变化和上升沿到来的影响,因此电路具有异步置位和复位的功能。

[0020]

在本发明中,需注意的是电阻r1的阻值需远远大于忆阻器m1设定的最大阻值且远远小于设定的最小阻值;电阻r2的阻值需远远大于忆阻器m2设定的最大阻值且远远小于设定的最小阻值。

[0021]

在本发明中,还需注意的是电压v1、v2、v3、v4、v5和v6为直流电压,电压v2和v5为高电平,电压v1、v3和v4小于忆阻器所设定的阈值电压。

[0022]

在本发明中,需注意置位信号s和复位信号r的不能同时为1

[0023]

本发明所提供的一种带异步置位复位的cmos混合型边沿忆阻d触发器,电路性能稳定,具有非易失性,电路具有异步置位和复位功能,且电路仿真测试效果良好。可根据具本发明具体电路图进行实际样品的制作。

[0024]

本领域的技术人员容易理解,以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所做的任何修改、替换和改进等,均应包含在本发明的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1