用于对码字进行译码的方法及译码器与流程

用于对码字进行译码的方法及译码器

1.本申请是申请日为2016年12月26日、申请号为201611216448.2、发明创造名称为“用于对码字进行译码的方法及译码器”的中国发明申请的分案申请。

技术领域

2.本发明涉及低密度奇偶校验(low-density parity check,ldpc)解码,尤其是涉及一种用于节省电力的低密度奇偶校验译码器和相关的译码方法。

背景技术:

3.低密度奇偶校验译码器使用具有奇偶位(parity bit)的线性错误校正码来进行译码,其中奇偶位会提供用于验证接收到的码字(codeword)的奇偶方程式给译码器。举例来说,低密度奇偶校验可为一具有固定长度的二进制代码,其中所有的符元(symbol)相加会等于零。

4.在编码过程中,所有的数据位会被重复执行并且被传送至对应的编码器,其中每个编码器会产生一奇偶符元(parity symbol)。码字是由k个信息位(information digit)以及r个校验位(check digit)所组成。如果码字总共有n位,则k=n-r。上述码字可用一奇偶校验矩阵来表示,其中所述奇偶校验矩阵具有r列(表示方程式的数量)以及n行(表示位数),如图1所示。这些码的所以被称为「低密度」是因为相较于奇偶校验矩阵中位0的数量而言,位1的数量相对的少。在解码过程中,每次的奇偶校验都可视为一奇偶校验码,并随后与其他奇偶校验码一起进行交互校验(cross-check),其中译码会在校验节点(check node)进行,而交互校验会在变数节点(variable node)进行。

5.ldpc译码器支持三种模式:硬判定硬解码(hard decision hard decoding)、软判定硬解码(soft decision hard decoding),以及软判定软解码(soft decision hard decoding)。图1是奇偶校验矩阵h(图1的上半部份)以及tanner graph(图1的下半部份)的示意图,其中tanner graph是另一种表示码字的方式,并且可用于解释当使用一位翻转(bit flipping)算法时,ldpc译码器的一些关于硬判定软解码的操作。

6.在tunner graph中,方形(c1~c4)所表示的校验节点(check node)代表奇偶位(parity bit)的数量,且圆形(v1~v7)所表示的变数节点(variable node)是一码字中位的数量。如果一特定方程式与码符元(code symbol)有关,则对应的校验节点与变数节点之间会以联机来表示。被估测的消息会沿着这些联机来传递,并且于节点上以不同的方式组合。一开始时,变数节点将发送一估测至所有联机上的校验节点,其中这些联机包括被认为是正确的位。接着,每个校验节点会依据对所有其他的连接的估测(connected estimate)来针对每一变数节点进行新的估测,并且将新的估测传回至变数节点。新的估测是基于:奇偶校验方程式迫使所有的变数节点连接至一特定校验节点,以使总和为零。

7.这些变数节点会接收新的信息以及使用一多数规则(majority rule)(也就是硬判定),来判断所传送的原始位的值是否正确,若不正确,所述原始位会被翻转(flipped)。所述位接着会被传回至所述校验节点,且上述步骤会被迭代地执行一预定次数,直到符合

这些校验节点的奇偶校验方程式。若有符合这些奇偶校验方程式(也就是校验节点所计算的值符合接收自变数节点的值),则可启用提前终止(early termination),这会使得系统在最大迭代次数达到之前就结束译码程序。

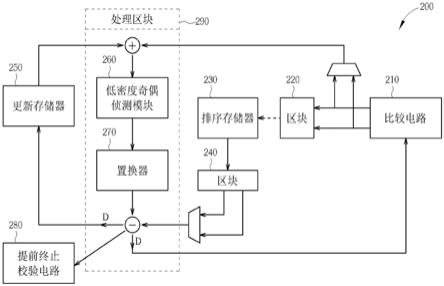

8.所述奇偶校验限制是由进行一症状校验(syndrome check)来实施。一个有效的码字将会符合方程式:h.c

t

=s=0,其中h是奇偶矩阵、c是硬判定码字,且s是症状。当s等于零时,表示译码程序已完成,且不需要更进一步的信息。一般来说,硬判定以及症状校验会在迭代期间执行,其中一非零(non-zero)症状表示有奇性(odd parity)存在,并且需要再执行新的译码迭代。

9.如上所述,通常会对每一次迭代进行症状校验以进行提前终止(early termination)。由于在一开始的迭代中,一码字不太可能会通过奇偶校验,因此若对于每一次迭代都进行症状校验会浪费电源。反的,若能降低症状校验的频率,则能够达到省电的效果。

技术实现要素:

10.本发明的一目的在于公开一种用于估测进行症状校验的最佳时间点的系统以及方法,并且利用所述系统以及方法来在一低密度奇偶校验(low-density parity check,ldpc)译码器中降低进行症状校验的频率。

11.本发明的一实施例公开了一种用于对低密度奇偶校验数据进行译码以译码一码字(codeword)的方法,所述方法包括以下步骤:接收多个初始估测(initial estimate),所述初始估测代表来自多个变数节点(variable node)的码字;发送所述初始估测至对应的多个校验节点;使用所述初始估测中所有的初始估测来计算多个后验机率(a posteriori probability,app)值以及一外部信息(extrinsic information),并且将所述后验机率值以及所述外部信息发送至所述变数节点;监测接收于所述校验节点的所述外部信息;当所述外部信息开始收敛到同一正负号(sign)时,针对所述初始估测启用一症状校验(syndrome check);以及当所述症状校验等于零时,提前终止(early termination)译码程序,否则,继续执行下一次的迭代。

12.本发明的一实施例公开了一种用于解码一码字的低密度奇偶校验译码器,包括一通道存储器、一减法器、一处理器、一加法器、低密度奇偶侦测电路、一提前终止电路以及一置换器。所述通道存储器是用于储存多个初始估测;所述减法器是耦接于所述通道存储器,并且用于产生一结果值以更新所述初始估测;所述处理器是耦接于所述减法器,并且用于产生多个后验机率(a posteriori probability,app)值以及一外部信息(extrinsic information);所述一加法器是耦接于所述处理器以及所述通道存储器,并且用于对所述后验机率值以及所述初始估测进行累加,以产生多个更新后初始估测;所述低密度奇偶侦测电路是耦接于所述加法器,并且用于侦测所述更新后初始估测;所述提前终止电路是耦接于所述低密度奇偶侦测电路,并且用于对所述更新后初始估测进行症状校验(syndrome check),以及于所述更新后初始估测通过症状校验时结束译码程序,其中当针对所述更新后初始估测的症状校验等于零时,判定所述更新后初始估测为通过症状校验;所述置换器是耦接于所述低密度侦测电路以及所述提前终止电路之间,其中当所述低密度侦测电路判断所述外部信息收敛至同一正负号时,所述置换器发送所述更新后初始估测至所述提前终

止电路。

附图说明

13.图1是根据先前技术的用于进行低密度奇偶校验译码的一奇偶校验矩阵以及tanner graph的示意图。

14.图2是根据本发明一实施例的低密度奇偶校验译码器的示意图。

15.其中,附图标记说明如下:

16.200

ꢀꢀꢀꢀꢀꢀꢀꢀ

低密度奇偶校验译码器

17.210

ꢀꢀꢀꢀꢀꢀꢀꢀ

比较电路

18.220,240

ꢀꢀꢀꢀ

区块

19.230

ꢀꢀꢀꢀꢀꢀꢀꢀ

排序存储器

20.250

ꢀꢀꢀꢀꢀꢀꢀꢀ

更新存储器

21.260

ꢀꢀꢀꢀꢀꢀꢀꢀ

低密度奇偶侦测模块

22.270

ꢀꢀꢀꢀꢀꢀꢀꢀ

置换器

23.280

ꢀꢀꢀꢀꢀꢀꢀꢀ

提前终止校验电路

24.290

ꢀꢀꢀꢀꢀꢀꢀꢀ

处理区块

具体实施方式

25.本发明的目的在于决定进行症状校验的最佳时间以节省电源,且目标是只有在结果(也就是上述的症状)可能等于零的时候才进行症状校验,而非如同先前技术在每一次迭代都进行症状校验。

26.以下列举两个方程式来说明本发明的方法,如以上关于先前技术的段落中所述,当症状(syndrome)等于零时,表示符合奇偶校验且译码程序可被终止。上述症状是通过将所述变数节点(variable node)值乘上奇偶校验矩阵而产生,如出方程式1所示:

27.h.c

t

=s

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(1)

28.当s等于零时,这表示可终止译码程序以及硬判定;否则,继续执行下一次的迭代。

29.此外,本发明使用和-积(sum-product)译码算法来判断何时可启用症状校验,而不使用位翻转(bit flipping)算法。在本发明所采用的和-积算法中,每一用于表示判定的信号是机率值。在位翻转算法中,虽然进行了硬判定,然而实际上接收到的是真实值(real value),其中位0、1分别表示正判定(positive decision)、负判定(negative decision),且数值的大小表示判定的可信度(level of confidence),此即为所谓的「软信息」(soft information)。和-积算法可通过针对每一位计算一后验机率(a posteriori probability,app)值app

j

来使用此软信息。后验机率值是在所有的奇偶校验都符合的情况下时,某一位会等于1的机率,而所述后验机率值app

j

的近似值(approximation)将会基于一系列的迭代来运算。

30.上述迭代会遵循位翻转算法,除了每次所计算的是:在所述位是一特定值的情况下,一奇偶校验方程式会被符合的机率。在所述校验节点每一次回传一机率值时,同时也会针对接着要被所述变数节点使用的位来回传独立于所述机率值的外部信息(extrinsic information),以作为下一次迭代的先验信息(a priori information)。

31.变数节点值、校验节点值以及用于和-积解码的后验机率值之间的关系如方程式2所示:

32.app

j

–

r

ij

=q

ij

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(2)

33.其中app

j

是校验节点所传送的后验机率值,q

ij

是来自变数节点的响应值,以及rij是来自所述校验节点的外部信息。下标j表示某一奇偶校验方程式,以及下标i表示所述程序代码的某一位。

34.在上述和-积算法中,当一码字被建立时,app

j

会逐渐地收敛。从方程式(2)可看出当app

j

逐渐地在一码字中收敛,r

ij

也会收敛但会小于app

j

。此外,当q

ij

收敛的时候,q

ij

的正负会大致相同(approximately equal)于app

j

的正负。因此,ldpc系统可通过使用一侦测电路来于多个校验节点值收敛到同一正负号(sign)的时候进行判断,以得知症状校验应该何时被启用。

35.接着,当症状校验被启用时,q

ij

值会代入方程式(1),以判断所述奇偶校验条件是否符合。一旦所述码字符合所述奇偶校验,可启用提前终止(early termination)来直接结束译码程序,而不需要等到迭代的最大数量已达到时才结束译码程序。

36.本发明实施例通过关闭症状校验,直到判断出来自校验节点的外部信息(或称软信息(soft information))有收敛至同一正负号才执行症状校验,可避免对每次迭代都进行症状校验而衍生的耗电。也就是说,当判断出一码字不会符合奇偶条件时,可避免多余地执行症状校验。此外,本发明在实作上使用一简单的侦测电路即可侦测到外部信息的正负,而不需要在ldpc译码器中额外套用复杂的电路架构。

37.参见图2,图2是根据本发明一实施例的低密度奇偶校验译码器200的示意图。如图2所示,排序存储器(order memory)230会接收到对应于所接收的符元(symbol)的多个对数可能性比(log likelihood ratio,llr),并且将其以向量的形式储存,而成为多个通道值。所述通道值以及对应的矩阵会被传递至一减法器(subtractor)(如图2中处理区块290内

“-”

所示),且结果值d会被传送至比较电路210以更新所述通道值,以及传送至更新存储器250。之后,更新存储器250再传送一结果至处理区块290,其中输出处理区块290会输出多个调整后的矩阵(modified metrics)。经过调整后的通道值以及矩阵会于加法器(如图2中处理区块290内“+”所示)累加,以产生一新的app值。在先前技术中,此新的app值会直接被传送至置换器(permutator)(例如图2所示的置换器270),而置换器270就会通过提前终止校验电路280来启动一症状校验操作。然而在本发明中,新的app值会先被传送至一低密度奇偶(low parity)侦测模块260,而不会直接传送至置换器270。低密度奇偶侦测模块260是用于侦测接收来自加法器的rij值,以判断这些rij值何时会收敛至同一正负号,并据此判断qij值是否稳定。若符合上述条件(也就是rij值已收敛至同一正负号且qij值已经稳定),置换器270会传送数据至提前终止校验电路280。若不符合上述条件(也就是rij值尚未收敛至同一正负号及/或qij值尚未稳定),置换器270会直接进行新的迭代,而不启用症状校验。比较电路210以及区块220、240(分别以w seq、r seq示意)的操作为本领域通常知识者可轻易了解,为简洁的故,其细节不再赘述。

38.综上所述,本发明利用和-积算法来对低密度奇偶校验码进行硬判定软译码(hard decision soft decoding),因而达到省电的效果。

39.以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技

术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1