电路板结构及其制作方法与流程

1.本发明涉及一种电路板结构及其制作方法,尤其涉及一种可避免在回焊期间产生翘曲的电路板结构及其制作方法。

背景技术:

2.发光二极管的选择和放置与电路板上的铜接触垫的平坦度有关。若电路板上的铜接触垫的平坦度不佳,则会降低接合良率,导致良率损失。再者,回焊温度及电路板的尺寸也会影响接合良率。当回焊温度较高时,较大面积尺寸的电路板因应力无法释放,而会发生较大的翘曲,进而降低电路板的组装良率。若为了避免大尺寸面积的电路板产生翘曲,而将电路板裁切成小面积尺寸的电路板,则会减少表面黏着技术(surface mounting technology,smt)组件的产能(assembly throughput),且也会增加发光二极管组装至显示器上的制作步骤。

技术实现要素:

3.本发明是针对一种电路板结构,可在回焊期间避免或减少产生翘曲,且可提高表面黏着技术(smt)组件的组装良率。

4.本发明还针对一种电路板结构的制作方法,用以制作上述的电路板结构。

5.根据本发明的实施例,电路板结构,其包括至少两子电路板以及至少一连接件。每一子电路板包括多个载板单元。连接件连接于子电路板之间,而于子电路板之间定义出多个应力释放间隙。

6.在根据本发明的实施例的电路板结构中,上述的每一应力释放间隙为贯孔。

7.在根据本发明的实施例的电路板结构中,上述的每一载板单元包括核心基材、多个导电胶块、第一线路层以及第二线路层。核心基材具有彼此相对的上表面与下表面以及贯穿核心基材且连接上表面与下表面的多个通孔。导电胶块分别配置于核心基材的通孔内。第一线路层配置于核心基材的上表面上,且覆盖上表面与每一导电胶块的顶表面。第二线路层配置于核心基材的下表面上,且覆盖下表面与每一导电胶块的底表面。

8.在根据本发明的实施例的电路板结构中,上述的每一载板单元还包括第一防焊层以及第二防焊层。第一防焊层配置于第一线路层所暴露出的部分上表面上,且延伸覆盖部分第一线路层上,并暴露出部分第一线路层。第二防焊层配置于第二线路层所暴露出的部分下表面上,且延伸覆盖部分第二线路层上,并暴露出部分第二线路层。

9.在根据本发明的实施例的电路板结构中,上述的每一载板单元还包括第一表面处理层以及第二表面处理层。第一表面处理层配置于第一防焊层所暴露出的第一线路层上。第二表面处理层配置于第二防焊层所暴露出的第二线路层上。

10.在根据本发明的实施例的电路板结构中,上述的至少一连接件包括多个连接件,且连接件位于同一轴线上。

11.在根据本发明的实施例的电路板结构中,上述的至少一连接件包括多个第一连接

件以及多个第二连接件。第一连接件位于第一轴线上,而第二连接件位于第二轴线上,且第一轴线垂直于第二轴线。

12.根据本发明的实施例,电路板结构的制作方法其包括以下步骤。提供电路基板,电路基板上形成有多个载板单元。形成多个应力释放间隙于电路基板上,而将电路基板区分为至少两子电路板以及至少一连接件。连接件连接于子电路板之间,且子电路板包括载板单元。

13.在根据本发明的实施例的电路板结构的制作方法中,上述的形成应力释放间隙于电路基板上的步骤包括形成多个贯孔于电路基板上。

14.在根据本发明的实施例的电路板结构的制作方法中,上述的形成每一载板单元的步骤包括:提供核心基材,核心基材具有彼此相对的上表面与下表面以及贯穿核心基材且连接上表面与下表面的多个通孔,其中核心基材处于b阶段(b-stage)状态。填充多个导电胶块于核心基材的通孔内,其中导电胶块突出于上表面与下表面。以压合、固化及图案化的方式分别形成第一线路层与第二线路层于核心基材上。核心基材由b阶段状态转变成c阶段(c-stage)状态。第一线路层配置于核心基材的上表面上,且覆盖上表面与每一导电胶块的顶表面,而第二线路层配置于核心基材的下表面上,且覆盖下表面与每一导电胶块的底表面。

15.基于上述,在本发明的电路板结构的设计中,连接于子电路板之间的连接件可与子电路板定义出应力释放间隙,藉此可释放于回焊期间电路板结构所产生的应力。因此,本发明的电路板结构可避免或减少产生翘曲,进而可提高表面黏着技术(smt)组件组装于其上的组装良率。

附图说明

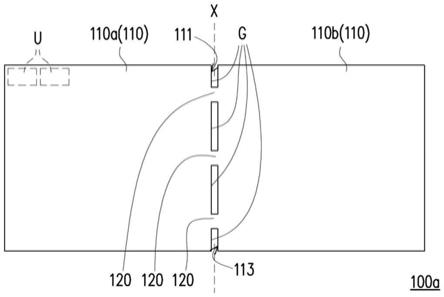

16.图1a是依照本发明的一实施例的一种电路板结构的示意图;

17.图1b是图1a中一个载板单元的剖面示意图;

18.图2是依照本发明的另一实施例的一种电路板结构的示意图;

19.图3是图1a的电路板结构接合至电路母板且芯片配置于电路板结构上的剖面示意图。

20.附图标记说明

21.10:电路母板;

22.20:芯片;

23.30:第一凸块;

24.40:第二凸块;

25.100a、100b:电路板结构;

26.110、110’:电路基板;

27.110a、110b、110c、110d:子电路板;

28.111、113:侧壁;

29.120:连接件;

30.120a:第一连接件;

31.120b:第二连接件;

32.210:核心基材;

33.212:上表面;

34.214:下表面;

35.216:通孔;

36.220:导电胶块;

37.222:顶表面;

38.224:底表面;

39.230:第一线路层;

40.240:第二线路层;

41.250:第一防焊层;

42.260:第二防焊层;

43.270:第一表面处理层;

44.280:第二表面处理层;

45.g、g1、g2:应力释放间隙;

46.u:载板单元;

47.x:轴线;

48.x1:第一轴线;

49.x2:第二轴线。

具体实施方式

50.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

51.图1a是依照本发明的一实施例的一种电路板结构的示意图。图1b是图1a中一个载板单元的剖面示意图。请先参考图1a,在本实施例中,电路板结构100a包括至少两子电路板(示意地示出两个子电路板110a、110b)以及至少一连接件(示意地示出三个连接件120)。每一子电路板110a、110b包括多个载板单元u。连接件120连接于子电路板110a、110b之间,而于子电路板110a、110b之间定义出多个应力释放间隙(示意地示出四个应力释放间隙g)。也就是说,每一连接件120是局部连接于子电路板110a、110b彼此相邻的两侧壁111、113,而两侧壁111、113与连接件120之间具有应力释放间隙g,其中应力释放间隙g与连接件120交替排列。此处,连接件120是位于同一轴线x上。

52.进一步来说,本实施例是先提供已形成有多个载板单元u的电路基板110。之后,形成应力释放间隙g于电路基板110上,而将电路基板110区分为子电路板110a、110b以及连接件120。此处,每一应力释放间隙g具体化为贯孔,其中例如是通过切割(cut)或钻孔的方式来形成应力释放间隙g,但不以此为限。

53.更具体来说,请参考图1b,每一载板单元u包括核心基材210、多个导电胶块(示意地示出两个导电胶块220)、第一线路层230以及第二线路层240。核心基材210具有彼此相对的上表面212与下表面214以及贯穿核心基材210且连接上表面212与下表面214的多个通孔(示意地示出两个通孔216)。导电胶块220分别配置于核心基材210的通孔216内。第一线路层230配置于核心基材210的上表面212上,且覆盖上表面212与每一导电胶块220的顶表面

222。第二线路层240配置于核心基材210的下表面214上,且覆盖下表面214与每一导电胶块220的底表面224。此处,第一线路层230与第二线路层240分别为图案化线路层,其中第一线路层230会暴露出核心基材210的部分上表面212,而第二线路层240会暴露出核心基材210的部分下表面214。

54.在制程上,形成每一载板单元u的步骤包括先提供核心基材210,其中核心基材210于此时处于b阶段状态,意即尚未完全固化,且核心基材210的厚度例如是20微米至100微米。接着,可于核心基材210的相对两侧贴附离型膜,其中离型膜的材质如是聚酯聚合物(pet)。接着,对核心基材210进行钻孔程序,而形成通孔216,其中钻孔程序例如是雷射钻孔或机械钻孔,但不以此为限。接着,以印刷(printing)或注入(injection)的方式,于通孔216内填充导电胶材,而形成导电胶块220。之后,移除贴附在核心基材210相对两侧的离型膜,而使导电胶块220的顶表面222与底表面224分别突出于核心基材210的上表面212与下表面214。接着,在核心基材210处于b阶段状态时,压合两铜箔层于核心基材210的上表面212与下表面214上,其中铜箔层覆盖核心基材210的上表面212与下表面214以及导电胶块220的顶表面222与底表面224。特别是,铜箔层的表面粗糙度小于1微米,其中铜箔层的相对两面的表面粗糙度可以不同,而铜箔层是以较粗面朝向核心基材210。之后,进行固化程序,而使铜箔层固定于核心基材210上。此时,核心基材210会由原来的b阶段状态转变成c阶段状态,意即呈现完全固化状态。紧接着,对两铜箔层进行图案化程序,而形成位于核心基材210的上表面212上的第一线路层230以及位于核心基材210的下表面214上的第二线路层240。

55.请再参考图1b,在本实施例中,每一载板单元u还包括第一防焊层250以及第二防焊层260。第一防焊层250配置于第一线路层230所暴露出的部分上表面212上,且延伸覆盖部分第一线路层230上,并暴露出部分第一线路层230。第二防焊层260配置于第二线路层240所暴露出的部分下表面214上,且延伸覆盖部分第二线路层240上,并暴露出部分第二线路层240。

56.此外,本实施例的每一载板单元u还包括第一表面处理层270以及第二表面处理层280。第一表面处理层270配置于第一防焊层250所暴露出的第一线路层230上,其中第一表面处理层270覆盖第一线路层230相对远离核心基材210的顶面及侧面。第二表面处理层280配置于第二防焊层260所暴露出的第二线路层240上,其中第二表面处理层280覆盖第二线路层240相对远离核心基材210的顶面及侧面。此处,第一表面处理层270与第二表面处理层280的材质分别例如是化镍钯浸金(enepig)、有机保焊剂(organic solderability preservatives,osp)层或无电镀镍浸金enig(electroless nickel immersion gold,enig),但不以此为限。

57.简言之,在本实施例的电路板结构100a的设计中,连接于子电路板110a、110b之间的连接件120可与子电路板110a、110b定义出应力释放间隙g,藉此可释放于回焊期间电路板结构100a所产生的应力。因此,本实施例的电路板结构100a可避免或减少产生翘曲,进而可提高表面黏着技术(smt)组件组装于其上的组装良率。

58.在此必须说明的是,下述实施例沿用前述实施例的元件标号与部分内容,其中采用相同的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,下述实施例不再重复赘述。

59.图2是依照本发明的另一实施例的一种电路板结构的示意图。请同时参考图2与图1a,本实施例的电路板结构100b与上述的电路板结构100a的相似,两者的差异在于:本实施例是于电路基板110’上形成应力释放间隙g1、g2,而将电路基板110’区分为子电路板110a、110b、110c、110d以及第一连接件120a与第二连接件120b。此处,第一连接件120a位于第一轴线x1上,而第二连接件120b位于第二轴线x2上,且第一轴线x1垂直于第二轴线x2。

60.图3是图1a的电路板结构接合至电路母板且芯片配置于电路板结构上的剖面示意图。在应用上,请参考图3,在本实施例中,多个芯片20可通过第一凸块30电性连接至电路板结构100a上,其中每一芯片20可对应一个载板单元u设置。电路板结构100a则可通过第二凸块40而电性连接至电路母板10上,其中第二凸块40的尺寸大于第一凸块30的尺寸。藉此,可扩大电路板结构100a的应用范围。

61.综上所述,在本发明的电路板结构的设计中,连接于子电路板之间的连接件可与子电路板定义出应力释放间隙,藉此可释放于回焊期间电路板结构所产生的应力。因此,本发明的电路板结构可避免或减少产生翘曲,进而可提高表面黏着技术(smt)组件组装于其上的组装良率。

62.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1