一种应用于逐次逼近型模数转换器的两电平开关方法与流程

[0001]

本发明涉及一种应用于逐次逼近型模数转换器的两电平开关方法,属于saradc的电荷重分配型cdac技术领域。

背景技术:

[0002]

电荷重分配型saradc由于高度数字化,与先进工艺兼容,高能效等特点广泛应用于便携设备、医疗器械和物联网等领域。在它的各个模块中,cdac是最耗能的一个部分,在saradc进行模数转换的时候,cdac会进行电容切换产生所需要的参考电压,过程中会产生动态的开关功耗。

[0003]

在已有的研究中,提出了多种开关算法来减小cdac的开关功耗。但是,它们在降低开关功耗的同时提高了复位功耗、共模电平漂移[1]、多个比较器[2]以及复杂的控制逻辑[3]等,最终,要么由于复位功耗的提高导致cdac功耗的降低并不理想,要么对其他模块,如比较器的设计指标提出了更高的要求,这就意味着cdac开关功耗的降低是以cdac本身复位功耗或者其他模块功耗的提高为代价的。因此,这些开关算法[1-3]对saradc整体功耗的降低未必具有积极意义。

[0004]

[1]z.zhu et al.:

‘

a0.6-v 38-nw 9.4-enob 20-ks/s saradc in 0.18-cmos formedical implant devices’,ieee transactions on circuits and systems-i.,2015,62,(9),pp.2167-2176

[0005]

[2]s.-e.hsieh and c.-c.hsieh.:

‘

a0.44-fj/conversion-step 11-bit 600-ks/s saradc with semi-restingdac’,ieee journal ofsolid-state circuits.,2018,53,(9),pp.2595-2603

[0006]

[3]c.h.kuo and c.e.hsieh.:

‘

floating capacitor switching saradc’.electronics letters,2011,47,(13),742-743

技术实现要素:

[0007]

技术问题:本发明所要解决的技术问题在于,针对saradc的设计,提出一种应用于逐次逼近型模数转换器的两电平开关方法,仅使用两个电平来对开关算法的能量效率(包括复位功耗)、电容面积、共模电平偏移和所需控制逻辑复杂度进行更好的折中,使得本开关算法在降低cdac功耗的同时不会对adc其他模块有较高的要求。不同于大多数已发表的开关方法,本发明第一次切换可以在电容顶极板产生

±

v

ref

的电压变化,因此,在相同量程条件下,电容阵列的参考电压v

ref

仅为其他开关算法的一半,利用复位开关和浮置电容技术使得复位功耗为零,且浮置电容在三步切换之内会切换到参考电平,简化了控制逻辑,减小了dac的功耗;仅在最后一位的判决上采用单端切换的开关算法,节省了电容面积,降低了共模电平漂移。

[0008]

技术方案:本发明的一种应用于逐次逼近型模数转换器的两电平开关方法具体采用以下技术方案解决上述技术问题:

[0009]

该方法基于的模数转换器,包括采样开关、复位开关、电容阵列、比较器和数字控制逻辑,其中电容阵列包括完全相同的上电容阵列和下电容阵列;输入信号vip通过采样开关连接到上电容阵列的顶极板,输入信号vin通过采样开关连接到下电容阵列的顶极板;上电容阵列的顶极板与比较器同相输入端相连,下电容阵列的顶极板与比较器的反相输入端相连,在两个电容阵列的顶极板,采样时连接到不同参考电压的子电容阵列之间存在一个复位开关,此开关在采样阶段会经历从打开到闭合两个阶段;比较器的差分输出端通过数字控制逻辑后产生控制信号来控制上下电容阵列的底极板开关,使上下电容阵列的底极板连接到对应电压、合并、分裂和浮置;

[0010]

所述上、下电容阵列均包括两个子电容阵列;其中,上电容阵列的两个子电容阵列分别命名为dac

p1

和dac

p0

;下电容阵列的两个子电容阵列分别命名为dac

n1

和dac

n0

,每一个子电容阵列由一个最高位电容c

n-4

以及n-6个高位电容、次低位电容c1、最低位电容c0以及dummy电容c

d

组成,各电容大小为:c

i

=2

i

c,其中0≤i≤n-4,dummy电容c

d

=c,其中n表示模数转换器的位数,c为单位电容大小;

[0011]

本方法包括对于输入信号vip和vin,经过模数转换器的n次比较后,得到n位数字输出码,分为采样和转换两个阶段。

[0012]

其中:

[0013]

所述开关方法的采样和转换两个阶段,具体包括以下步骤:

[0014]

步骤a、采样阶段

[0015]

输入信号vip和vin通过采样开关分别连接到上电容阵列和下电容阵列的顶极板,此时,复位开关处于打开状态,然后上电容阵列的子电容阵列dac

p1

的所有电容底极板连接到v

ref

参考电压,而上电容阵列的子电容阵列dac

p0

的所有电容底极板连接到gnd;下电容阵列的子电容阵列dac

n1

的所有电容底极板连接到gnd,而下电容阵列的子电容阵列dac

n0

的所有电容底极板连接到v

ref

参考电压;完成上述连接之后,复位开关进入闭合状态,复位开关的断开与闭合是为了实现零复位功耗;

[0016]

步骤b、转换阶段

[0017]

步骤b1,将模数转换器的采样开关断开,然后比较器直接对保持在上下电容阵列顶极板的输入信号vip和vin进行比较,得出最高有效位d

n-1

,根据数字码d

n-1

控制上下电容阵列中电容底极板的连接关系;

[0018]

步骤b2,比较器(4)通过比较从步骤b1获取的上下电容阵列顶极板电压,得出数字码d

n-2

,根据数字码d

n-1

d

n-2

控制上下电容阵列中电容底极板的连接关系;

[0019]

步骤b3,比较器(4)通过比较从步骤b2获取的上下电容阵列顶极板电压,得出数字码d

n-3

,根据数字码d

n-1

d

n-2

和d

n-3

控制上下电容阵列中电容底极板的连接关系;

[0020]

步骤b4,比较器(4)通过比较从步骤b3获取的上下电容阵列顶极板电压,得出数字码d

k

,其中1≤k≤n-4,根据数字码d

n-1

和d

k

控制上下电容阵列中电容底极板的连接关系;且重复步骤b4,直至得出数字码d1;

[0021]

步骤b5,根据数字码d

n-1

和d1控制上下电容阵列中电容底极板的连接关系,比较器通过比较此时的上下电容阵列顶极板电压,得出数字码d0。

[0022]

所述步骤b1,根据数字码d

n-1

控制上下电容阵列中电容底极板的连接关系具体为;

[0023]

情况一:若d

n-1

=1,dac

p0

和dac

n0

的所有电容底极板由gnd和v

ref

变为浮置状态,此

次转换过程中不再对dac

p0

和dac

n0

进行其他操作,dac

p1

和dac

n1

的最高位电容和次高位底极板由v

ref

和gnd变为浮置状态,dac

p1

和dac

n1

中其他电容底极板合并,这样整个dac的差分电压将减少v

ref

;

[0024]

情况二:若d

n-1

=0,dac

p1

和dac

n1

的所有电容底极板由v

ref

和gnd变为浮置状态,此次转换过程中不再对dac

p1

和dac

n1

进行其他操作,dac

p0

和dac

n0

的最高位电容和次高位底极板由gnd和v

ref

变为浮置状态,dac

p0

和dac

n0

中其他电容底极板合并,这样整个dac的差分电压将增加v

ref

。

[0025]

所述步骤b2,根据数字码d

n-1

和d

n-2

控制上下电容阵列中电容底极板的连接关系,具体为:

[0026]

情况一:若d

n-1

d

n-2

=11,dac

p1

的次高位电容由浮置连接到gnd,而dac

n1

的次高位电容由浮置连接到v

ref

参考电压,这样整个dac的差分电压将减少0.5v

ref

;

[0027]

情况二:若d

n-1

d

n-2

=10,dac

p1

的次高位电容由浮置连接到v

ref

参考电压,而dac

n1

的次高位电容由浮置连接到gnd,这样整个dac的差分电压将增加0.5v

ref

;

[0028]

情况三:若d

n-1

d

n-2

=01,dac

p0

的次高位电容由浮置连接到gnd,而dac

n0

的次高位电容由浮置连接到v

ref

参考电压,这样整个dac的差分电压将减少0.5v

ref

;

[0029]

情况四:若d

n-1

d

n-2

=00,dac

p0

的次高位电容由浮置连接到v

ref

参考电压,而dac

n0

的次高位电容由浮置连接到gnd,这样整个dac的差分电压将增加0.5v

ref

。

[0030]

所述步骤b3,根据数字码d

n-1

、d

n-2

和d

n-3

控制上下电容阵列中电容底极板的连接关系,具体为:

[0031]

情况一:若d

n-1

d

n-2

d

n-3

=111,dac

p1

的最高位电容连接到gnd,dac

n1

的最高位电容连接到v

ref

参考电压,这样整个dac的差分电压将减小0.25v

ref

;

[0032]

情况二:若d

n-1

d

n-2

d

n-3

=110,dac

p1

的最高位电容和dac

n1

的最高位电容底极板合并,这样整个dac的差分电压将增加0.25v

ref

;

[0033]

情况三:若d

n-1

d

n-2

d

n-3

=101,dac

p1

的最高位电容和dac

n1

的最高位电容底极板合并,这样整个dac的差分电压将减小0.25v

ref

;

[0034]

情况四:若d

n-1

d

n-2

d

n-3

=100,dac

p1

的最高位电容连接到v

ref

参考电压,dac

n1

的最高位电容连接到gnd,这样整个dac的差分电压将增加0.25v

ref

;

[0035]

情况五:若d

n-1

d

n-2

d

n-3

=011,dac

p0

的最高位电容连接到gnd,dac

n0

的最高位电容连接到v

ref

参考电压,这样整个dac的差分电压将减小0.25v

ref

;

[0036]

情况六:若d

n-1

d

n-2

d

n-3

=010,dac

p0

的最高位电容和dac

n0

的最高位电容底极板合并,这样整个dac的差分电压将增加0.25v

ref

;

[0037]

情况七:若d

n-1

d

n-2

d

n-3

=001,dac

p0

的最高位电容和dac

n0

的最高位电容底极板合并,这样整个dac的差分电压将减小0.25v

ref

;

[0038]

情况八:若d

n-1

d

n-2

d

n-3

=000,dac

p0

的最高位电容连接到v

ref

参考电压,dac

n0

的最高位电容连接到gnd,这样整个dac的差分电压将增加0.25v

ref

。

[0039]

所述步骤b4,根据数字码d

n-1

和d

k

控制上下电容阵列中电容底极板的连接关系,具体为:

[0040]

情况一:若d

n-1

d

k

=11,dac

p1

的电容c

k-2

解除合并状态并连接到gnd,dac

n1

的电容c

k-2

解除合并状态并连接到v

ref

参考电压,这样整个dac的差分电压将减小2

(k-n+1)

v

ref

;

[0041]

情况二:若d

n-1

d

k

=10,,dac

p1

的电容c

k-2

解除合并状态并连接到v

ref

参考电压,dac

n1

的电容c

k-2

解除合并状态并连接到gnd,这样整个dac的差分电压将增加2

(k-n+1)

v

ref

;

[0042]

情况三:若d

n-1

d

k

=01,dac

p0

的电容c

k-2

解除合并状态并连接到gnd,dac

n0

的电容c

k-2

解除合并状态并连接到v

ref

参考电压,这样整个dac的差分电压将减小2

(k-n+1)

v

ref

;

[0043]

情况四:若d

n-1

d

k

=00,,dac

p0

的电容c

k-2

解除合并状态并连接到v

ref

参考电压,dac

n0

的电容c

k-2

解除合并状态并连接到gnd,这样整个dac的差分电压将增加2

(k-n+1)

v

ref

;

[0044]

其中,n为模数转换器位数,k为当前所得数字码的序数,且1≤k≤n-4,即,在步骤b4中将从高到低依次得到d

n-4

到d1等多个数字码。

[0045]

所述步骤b5,根据数字码d

n-1

和d1控制上下电容阵列中电容底极板的连接关系,具体为:

[0046]

情况一:若d

n-1

d1=11,dac

p1

的dummy电容解除合并状态并连接到gnd,dac

n1

的dummy电容解除合并状态并保持浮置,这样整个dac的差分电压将减少2

(2-n)

v

ref

;

[0047]

情况二:若d

n-1

d1=10,dac

p1

的dummy电容解除合并状态并保持浮置,dac

n1

的dummy电容解除合并状态并连接到gnd,这样整个dac的差分电压将增加2

(2-n)

v

ref

;

[0048]

情况三:若d

n-1

d1=01,dac

p0

的dummy电容解除合并状态并连接到gnd,dac

n0

的dummy电容解除合并状态并保持浮置,这样整个dac的差分电压将减小2

(2-n)

v

ref

;

[0049]

情况四:若d

n-1

d1=00,dac

p0

的dummy电容解除合并状态并保持浮置,dac

n0

的dummy电容解除合并状态并连接到gnd,这样整个dac的差分电压将增加2

(2-n)

v

ref

;

[0050]

其中,n为模数转换器位数。

[0051]

有益效果:本发明采用上述技术方案,能产生如下技术效果:

[0052]

1.本发明提出的适用于sar adc的两电平开关方法第一次切换可以在电容顶极板产生

±

v

ref

的电压变化,因此,在相同量程条件下,电容阵列的参考电压v

ref

仅为其他开关算法的一半,大幅降低开关功耗,同时,利用复位开关和浮置电容技术使得复位功耗为零;且浮置电容在三步切换之内会切换到参考电平,简化了控制逻辑;最后一位的单端切换减小电容面积的同时仅引入0.5lsb的共模电平偏移。与传统的开关算法相比,本发明不但能够降低99.51%的电容dac的功耗,节省75%的电容面积,而且对其他模块的要求也没有提高,进一步提升了sar adc整体的能效。

附图说明

[0053]

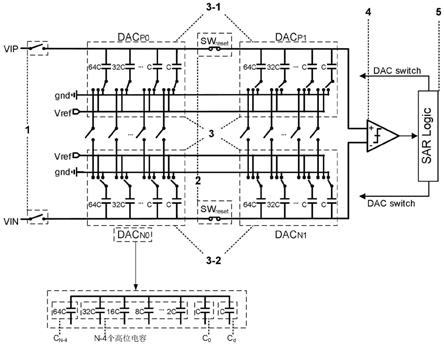

图1为本发明方法实现10位分辨率采用的saradc的结构示意图。

[0054]

图2为本发明方法应用于6位saradc的开关切换示意图。

[0055]

图3为本发明方法应用于10位saradc的开关切换能耗随adc输出码变化的matlab仿真结果图(为了方便比较,图中的v为包括v

cm-based开关算法在内的大多数开关算法的cdac参考电压)。

具体实施方式

[0056]

下面结合说明书附图对本发明的实施方式进行描述。

[0057]

本发明设计了一种适用于低功耗saradc电容阵列的floating开关切换方式,该方法基于的10位saradc的结构如图1所示,包括采样开关、复位开关、电容阵列、比较器和数字

控制逻辑。其中电容阵列包括完全相同的上电容阵列和下电容阵列;输入信号vip通过采样开关连接到上电容阵列的顶极板,输入信号vin通过采样开关连接到下电容阵列的顶极板;上电容阵列的顶极板与比较器同相输入端相连,下电容阵列的顶极板与比较器的反相输入端相连,在两个电容阵列的顶极板,采样时连接到不同参考电压的子电容阵列之间存在一个复位开关,此开关在采样阶段会经历从打开到闭合两个阶段;比较器的差分输出端通过数字控制逻辑后产生控制信号来控制上下电容阵列的底极板开关,使上下电容阵列的底极板连接到对应电压、合并、分裂和浮置;

[0058]

所述上下电容阵列均包括两个子电容阵列。其中,上电容阵列的两个子电容阵列分别命名为dac

p1

和dac

p0

;下电容阵列的两个子电容阵列分别命名为dac

n1

和dac

n0

。每一个子电容阵列由一个最高位电容c

n-4

以及n-6个高位电容、次低位电容c1、最低位电容c0以及dummy电容c

d

组成,各电容大小为:c

i

=2

i

c

u

,其中0≤i≤n-4,dummy电容c

d

=c

u

,其中n表示模数转换器的位数,c

u

为单位电容大小;

[0059]

本方法包括对于输入信号vip和vin,经过模数转换器的n次比较后,得到n位数字输出码,分为采样和转换两个阶段,具体包括以下步骤:

[0060]

步骤a、采样阶段

[0061]

输入信号vip和vin通过采样开关分别连接到上电容阵列和下电容阵列的顶极板。此时,复位开关处于打开状态,然后上电容阵列的子电容阵列dac

p1

的所有电容底极板连接到v

ref

参考电压,而上电容阵列的子电容阵列dac

p0

的所有电容底极板连接到gnd;下电容阵列的子电容阵列dac

n1

的所有电容底极板连接到gnd,而下电容阵列的子电容阵列dac

n0

的所有电容底极板连接到v

ref

参考电压;完成上述连接之后,复位开关进入闭合状态,复位开关的断开与闭合是为了实现零复位功耗;

[0062]

步骤b、转换阶段

[0063]

步骤b1,将模数转换器的采样开关断开,然后比较器直接对保持在上下电容阵列顶极板的输入信号vip和vin进行msb位比较,得出数字码d

n-1

,根据数字码d

n-1

控制上下电容阵列中电容底极板的连接关系;

[0064]

情况一:若d

n-1

=1,dac

p0

和dac

n0

的所有电容底极板由gnd和v

ref

变为浮置状态,此次转换过程中不再对dac

p0

和dac

n0

进行其他操作,dac

p1

和dac

n1

的最高位电容和次高位底极板由v

ref

和gnd变为浮置状态,dac

p1

和dac

n1

中其他电容底极板合并。这样整个dac的差分电压将减少v

ref

;

[0065]

情况二:若d

n-1

=0,dac

p1

和dac

n1

的所有电容底极板由v

ref

和gnd变为浮置状态,此次转换过程中不再对dac

p1

和dac

n1

进行其他操作,dac

p0

和dac

n0

的最高位电容和次高位底极板由gnd和v

ref

变为浮置状态,dac

p0

和dac

n0

中其他电容底极板合并。这样整个dac的差分电压将增加v

ref

;

[0066]

步骤b2,比较器通过比较从步骤b1获取的上下电容阵列顶极板电压,得出数字码d

n-2

,根据数字码d

n-1

d

n-2

控制上下电容阵列中电容底极板的连接关系;

[0067]

情况一:若d

n-1

d

n-2

=11,dac

p1

的次高位电容由浮置连接到gnd,而dac

n1

的次高位电容由浮置连接到v

ref

参考电压。这样整个dac的差分电压将减少0.5v

ref

;

[0068]

情况二:若d

n-1

d

n-2

=10,dac

p1

的次高位电容由浮置连接到v

ref

参考电压,而dac

n1

的次高位电容由浮置连接到gnd。这样整个dac的差分电压将增加0.5v

ref

;

[0069]

情况三:若d

n-1

d

n-2

=01,dac

p0

的次高位电容由浮置连接到gnd,而dac

n0

的次高位电容由浮置连接到v

ref

参考电压。这样整个dac的差分电压将减少0.5v

ref

;

[0070]

情况四:若d

n-1

d

n-2

=00,dac

p0

的次高位电容由浮置连接到v

ref

参考电压,而dac

n0

的次高位电容由浮置连接到gnd。这样整个dac的差分电压将增加0.5v

ref

;

[0071]

步骤b3,比较器通过比较从步骤b2获取的上下电容阵列顶极板电压,得出数字码d

n-3

,根据数字码d

n-1

d

n-2

和d

n-3

控制上下电容阵列中电容底极板的连接关系;

[0072]

情况一:若d

n-1

d

n-2

d

n-3

=111,dac

p1

的最高位电容连接到gnd,dac

n1

的最高位电容连接到v

ref

参考电压,这样整个dac的差分电压将减小0.25v

ref

;

[0073]

情况二:若d

n-1

d

n-2

d

n-3

=110,dac

p1

的最高位电容和dac

n1

的最高位电容底极板合并,这样整个dac的差分电压将增加0.25v

ref

;

[0074]

情况三:若d

n-1

d

n-2

d

n-3

=101,dac

p1

的最高位电容和dac

n1

的最高位电容底极板合并,这样整个dac的差分电压将减小0.25v

ref

;

[0075]

情况四:若d

n-1

d

n-2

d

n-3

=100,dac

p1

的最高位电容连接到v

ref

参考电压,dac

n1

的最高位电容连接到gnd,这样整个dac的差分电压将增加0.25v

ref

;

[0076]

情况五:若d

n-1

d

n-2

d

n-3

=011,dac

p0

的最高位电容连接到gnd,dac

n0

的最高位电容连接到v

ref

参考电压,这样整个dac的差分电压将减小0.25v

ref

;

[0077]

情况六:若d

n-1

d

n-2

d

n-3

=010,dac

p0

的最高位电容和dac

n0

的最高位电容底极板合并,这样整个dac的差分电压将增加0.25v

ref

;

[0078]

情况七:若d

n-1

d

n-2

d

n-3

=001,dac

p0

的最高位电容和dac

n0

的最高位电容底极板合并,这样整个dac的差分电压将减小0.25v

ref

;

[0079]

情况八:若d

n-1

d

n-2

d

n-3

=000,dac

p0

的最高位电容连接到v

ref

参考电压,dac

n0

的最高位电容连接到gnd,这样整个dac的差分电压将增加0.25v

ref

;

[0080]

步骤b4,比较器通过比较从步骤b3获取的上下电容阵列顶极板电压,得出数字码d

k

,其中1≤k≤n-4,根据数字码d

n-1

和d

k

控制上下电容阵列中电容底极板的连接关系;且重复步骤b4,直至得出数字码d1;

[0081]

情况一:若d

n-1

d

k

=11,dac

p1

的电容c

k-2

解除合并状态并连接到gnd,dac

n1

的电容c

k-2

解除合并状态并连接到v

ref

参考电压,这样整个dac的差分电压将减小2

(k-n+1)

v

ref

;

[0082]

情况二:若d

n-1

d

k

=10,,dac

p1

的电容c

k-2

解除合并状态并连接到v

ref

参考电压,dac

n1

的电容c

k-2

解除合并状态并连接到gnd,这样整个dac的差分电压将增加2

(k-n+1)

v

ref

;

[0083]

情况三:若d

n-1

d

k

=01,dac

p0

的电容c

k-2

解除合并状态并连接到gnd,dac

n0

的电容c

k-2

解除合并状态并连接到v

ref

参考电压,这样整个dac的差分电压将减小2

(k-n+1)

v

ref

;

[0084]

情况四:若d

n-1

d

k

=00,,dac

p0

的电容c

k-2

解除合并状态并连接到v

ref

参考电压,dac

n0

的电容c

k-2

解除合并状态并连接到gnd,这样整个dac的差分电压将增加2

(k-n+1)

v

ref

;

[0085]

步骤b5,根据数字码d

n-1

和d1控制上下电容阵列中电容底极板的连接关系,比较器通过比较此时的上下电容阵列顶极板电压,得出数字码d0。

[0086]

情况一:若d

n-1

d1=11,dac

p1

的dummy电容解除合并状态并连接到gnd,dac

n1

的dummy电容解除合并状态并保持浮置,这样整个dac的差分电压将减少2

(2-n)

v

ref

;

[0087]

情况二:若d

n-1

d1=10,dac

p1

的dummy电容解除合并状态并保持浮置,dac

n1

的dummy电容解除合并状态并连接到gnd,这样整个dac的差分电压将增加2

(2-n)

v

ref

;

[0088]

情况三:若d

n-1

d1=01,dac

p0

的dummy电容解除合并状态并连接到gnd,dac

n0

的dummy电容解除合并状态并保持浮置,这样整个dac的差分电压将减小2

(2-n)

v

ref

;

[0089]

情况四:若d

n-1

d1=00,dac

p0

的dummy电容解除合并状态并保持浮置,dac

n0

的dummy电容解除合并状态并连接到gnd,这样整个dac的差分电压将增加2

(2-n)

v

ref

;1.因此,本发明方法的比较器的差分输出端通过数字控制逻辑后产生控制信号来控制上下电容阵列的底极板开关,使连接到对应的参考电压、合并、分裂和浮置。通过对其核心模块电容阵列的特殊构建并结合所提出的新的两电平开关算法,能够大大降低转换过程中的dac部分的功耗,节省电容面积和减小共模电平漂移。

[0090]

下面结合一个实例对本发明做具体的说明,由于d

n-1

=1和d

n-1

=0两种情况下,msb到lsb位的量化拨电容的过程是完全对称的,为避免叙述累赘,假设d

n-1

=1,图2所示为本发明实施例的6bit saradc的具体转换过程:

[0091]

步骤a、采样阶段

[0092]

输入信号vip和vin通过采样开关分别连接到上电容阵列和下电容阵列的顶极板。此时,复位开关处于打开状态,然后上电容阵列的子电容阵列dac

p1

的所有电容底极板连接到v

ref

参考电压,而上电容阵列的子电容阵列dac

p0

的所有电容底极板连接到gnd;下电容阵列的子电容阵列dac

n1

的所有电容底极板连接到gnd,而下电容阵列的子电容阵列dac

n0

的所有电容底极板连接到v

ref

参考电压;完成上述连接之后,复位开关进入闭合状态,复位开关的断开与闭合是为了实现零复位功耗;

[0093]

步骤b、转换阶段

[0094]

步骤b1,将模数转换器的采样开关断开,然后比较器直接对保持在上下电容阵列顶极板的输入信号vip和vin进行msb位比较,得出数字码d5,根据数字码d5控制上下电容阵列中电容底极板的连接关系;

[0095]

由于d5=1,dac

p0

和dac

n0

的所有电容底极板由gnd和v

ref

变为浮置状态,此次转换过程中不再对dac

p0

和dac

n0

进行其他操作,dac

p1

和dac

n1

的最高位电容和次高位底极板由v

ref

和gnd变为浮置状态,dac

p1

和dac

n1

中其他电容底极板合并。这样整个dac的差分电压将减少v

ref

;

[0096]

步骤b2,比较器通过比较从步骤b1获取的上下电容阵列顶极板电压,得出数字码d4,根据数字码d5d4控制上下电容阵列中电容底极板的连接关系;

[0097]

情况一:若d5d4=11,dac

p1

的次高位电容由浮置连接到gnd,而dac

n1

的次高位电容由浮置连接到v

ref

参考电压。这样整个dac的差分电压将减少0.5v

ref

;

[0098]

情况二:若d5d4=10,dac

p1

的次高位电容由浮置连接到v

ref

参考电压,而dac

n1

的次高位电容由浮置连接到gnd。这样整个dac的差分电压将增加0.5v

ref

;

[0099]

步骤b3,比较器通过比较从步骤b2获取的上下电容阵列顶极板电压,得出数字码d3,根据数字码d5d4和d3控制上下电容阵列中电容底极板的连接关系;

[0100]

情况一:若d5d4d3=111,dac

p1

的最高位电容连接到gnd,dac

n1

的最高位电容连接到v

ref

参考电压,这样整个dac的差分电压将减小0.25v

ref

;

[0101]

情况二:若d5d4d3=110,dac

p1

的最高位电容和dac

n1

的最高位电容底极板合并,这样整个dac的差分电压将增加0.25v

ref

;

[0102]

情况三:若d5d4d3=101,dac

p1

的最高位电容和dac

n1

的最高位电容底极板合并,这

样整个dac的差分电压将减小0.25v

ref

;

[0103]

情况四:若d5d4d3=100,dac

p1

的最高位电容连接到v

ref

参考电压,dac

n1

的最高位电容连接到gnd,这样整个dac的差分电压将增加0.25v

ref

;

[0104]

步骤b4,比较器通过比较从步骤b3获取的上下电容阵列顶极板电压,得出数字码d

k

,其中1≤k≤2,根据数字码d5d

k

控制上下电容阵列中电容底极板的连接关系;且重复步骤b4,直至得出数字码d1;

[0105]

情况一:若d

n-1

d

k

=11,dac

p1

的电容c

k-2

解除合并状态并连接到gnd,dac

n1

的电容c

k-2

解除合并状态并连接到v

ref

参考电压,这样整个dac的差分电压将减小2

(k-5)

v

ref

;

[0106]

情况二:若d

n-1

d

k

=10,,dac

p1

的电容c

k-2

解除合并状态并连接到v

ref

参考电压,dac

n1

的电容c

k-2

解除合并状态并连接到gnd,这样整个dac的差分电压将增加2

(k-5)

v

ref

;

[0107]

步骤b5,根据数字码d5和d1控制上下电容阵列中电容底极板的连接关系,比较器通过比较此时的上下电容阵列顶极板电压,得出数字码d0。

[0108]

情况一:若d5d1=11,dac

p1

的dummy电容解除合并状态并连接到gnd,dac

n1

的dummy电容解除合并状态并保持浮置,这样整个dac的差分电压将减少2

(-4)

v

ref

;

[0109]

情况二:若d5d1=10,dac

p1

的dummy电容解除合并状态并保持浮置,dac

n1

的dummy电容解除合并状态并连接到gnd,这样整个dac的差分电压将增加2

(-4)

v

ref

;

[0110]

如图3所示,是本发明应用于10位sar adc的开关与复位功耗随adc输出码变化的matlab仿真结果图,本发明不但能够降低99.51%的电容dac的功耗,节省75%的电容面积,而且对其他模块的要求也没有提高,进一步提升了sar adc整体的能效。

[0111]

综上,本发明方法利用第一次切换的

±

v

ref

的电压变化,以及复位开关和浮置电容技术,通过灵活的开关切换,降低cdac开关功耗的同时进一步提升了sar adc整体的能效。

[0112]

上面结合附图对本发明的实施方式作了详细说明,但是本发明并不限于上述实施方式,在本领域普通技术人员所具备的知识范围内,还可以在不脱离本发明宗旨的前提下做出各种变化。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1