一种基于预处理和简化存储的极化码译码器、译码方法、电子设备及计算机可读存储介质与流程

1.本发明属于通信技术领域,具体涉及一种基于预处理和简化存储的极化码译码器、译码方法、电子设备及计算机可读存储介质。

背景技术:

2.在通信系统中,信息的正确传递是最基本的一个问题,人们最希望收到的,一定是完完全全发射方发出的原始信息码子,但是由于信息在介质中传播时,不可避免的要受到光、大气等一系列噪声的污染,所以接收方受到的信息,往往与发射方想传递的信息有很大出入。寻找解决噪声在信息传递过程中的恶劣影响的方法,成为了众多研究者工作的目标。随后,研究者们提出了一系列编译码方案,希望能在数学理论上,通过在发射端进行编码操作,对原始信息进行设计,在接收端对受到污染的经过重新设计的信息码子进行相应的译码操作,来改善通信系统的性能。

3.近些年来,信息的编译码问题越来越受到众多研究者的关注。但要在现如今的通信环境下,找到一种实用的编译码算法却挑战十足,具体难点如下:

4.要求算法有良好的通信性能:低的误码率,较高的吞吐率,合适的码率。

5.要求算法适合工程实现:较低的硬件复杂度,适中的硬件面积,较低的译码延时。

6.早期reed和solomon提出了rs(reed

‑

solomon,rs)码,其作为一类特殊的bch(bose ray

‑

chaudhuri hocquenghem,bch)码,有着十分优秀的译码性能,但由于其译码算法中过于复杂的迭代和搜索步骤,导致其工程实现的代价过大,所以rs码虽然性能优越,却并没有得到广泛使用。随后robert gallager提出了低密度校验码(low

‑

density parity

‑

check,ldpc),其编译码复杂度与rs码相比相对较低,且译码性能也符合通信系统的要求,所以得到了长足的发展。而在2008年的信息理论国际研讨会(international symposium on information theory,isit)上,土耳其教授arikan提出了polar码,这是人类已知的第一种能够被严格证明达到信道容量的信道编码方法,由于其对香农线的优秀的逼近能力,polar码的编译码方案,在此后得到了空前的关注与发展。

7.随着5g通信的提出和发展,polar码在与ldpc码的竞争中脱颖而出,成为为5g标准下的码字,所以其译码器的工程实现,被提上日程。

8.其中arikan提出的连续消除译码算法(successive cancellation,sc)由于其适中的复杂度,以及适合工程实现的特点,被广大学者深入研究,并且其硬件上的实现,也随之有了一定的基础与发展。但由于sc算法本身深度优先的特点,导致其译码性能并不理想,误码率较高,硬件利用率较低。所以为了提高sc译码算法的译码性能,tal和vardy在sc算法的基础上,提出了scl算法,该算法是基于广度优先的策略,大大提高了译码性能,降低了误码率,但与此同时,由于其广度优先的特点,提升了计算复杂度,这也将提升硬件面积。

9.由于scl算法出色的译码性能和与硬件的契合特性。现有的polar码硬件译码器,大多是依据scl算法设计的,而随之而来的硬件复杂度,则是众多设计者关注的侧重点。在

scl译码算法硬件实现中,最消耗硬件面积的地方,就是sc模块中复杂的迭代公式的实现和各个阶段迭代完成之后,对得到的对数似然比的存储。现有技术大多都是根据学者们设计出的简化迭代公式,完成译码算法的迭代。尽管迭代公式已被简化,也还是带有如指数运算等不利于硬件实现,或者需要大量硬件面的数学运算。另外,在存储方面,则是选用预先设计好对数似然比的存储矩阵,来完成存储,再额外设计出迭代算法的控制模块,以及对数似然比的存储和读取的地址计算等模块来辅助完成。这些设计都会导致硬件面积的扩大,以及译码延时的提高。

技术实现要素:

10.为了解决现有技术中存在的上述问题,本发明提供了一种基于预处理和简化存储的极化码译码器、译码方法、电子设备及计算机可读存储介质。本发明要解决的技术问题通过以下技术方案实现:

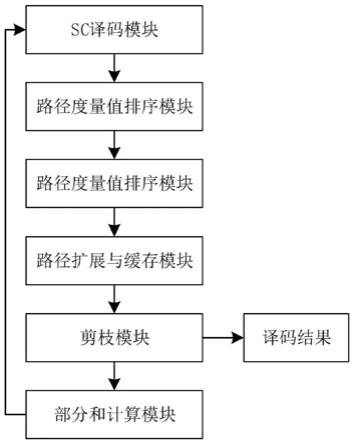

11.一种基于预处理和简化存储的极化码译码器,包括依次连接的sc译码模块、路径度量值计算模块、路径度量值排序模块、路径扩展与缓存模块、剪枝模块和部分和计算模块;

12.所述sc译码模块,用于计算各个路径中每个译码比特对应的对数似然比;

13.所述路径度量值计算模块,用于根据对应路径所译比特的对数似然比,计算相应路径的路径度量值;

14.所述路径度量值排序模块,用于每个所述路径度量值进行排序,得到排序路径信息;

15.所述路径扩展与缓存模块,用于接收到排序路径信息后,将所述排序路径信息按顺序并行保存,同时按照收到的排序信息,对之前存储的路径进行复制和扩展后发送至剪枝模块;

16.所述剪枝模块用于对复制和扩展的路径进行剪枝,根据列表大小保留所需要的路径,并将保留的路径,发送至并行的部分和计算模块;

17.所述部分和计算模块用于将已经译出的码子作为输入,通过异或操作和赋值操作,则可得到相应级数的部分和信号,并将部分和信号输出至所述sc译码模块作为下一轮sc模块的选通信号,直至n次循环结束后,对得到的译码结果进行输入,其中,n为码长。

18.在一个具体实施方式中,所述sc译码模块为树形流水型结构,包括依次连接的第一级fg函数处理电路、第二级fg函数处理电路、第三级fg函数处理电路;

19.所述第一级fg函数处理电路包括四个并行的fg函数处理单元,用于接收量化好的八个对数似然比,处理后将得到的四个13位宽的内部对数似然比输出至第二级fg函数处理电路;

20.所述第二级fg函数处理电路包括两个并行的fg函数处理单元,用于接收四个13位宽的内部对数似然比,处理后将得到的两个14位宽的内部对数似然比输出至第三级fg函数处理电路;

21.所述第三级fg函数处理电路包括一个fg函数处理单元,用于接收两个14位宽的内部对数似然比,处理后将得到的一个15位宽的内部对数似然比输出至路径度量值计算模块。

22.在一个具体实施方式中,每个所述fg函数处理单元均包括:一个fg函数运算电路、延时器、第一选择器和第二选择器;

23.所述fg函数运算电路的f函数输出端连接延时器输入端、fg函数运算电路的g函数输出端连接第一选择器;所述延时器输出端和所述第一选择器输出端连接第二选择器输入端。

24.在一个具体实施方式中,fg函数运算电路包括:第一符号剥离电路、第二符号剥离电路、第一异或门、第二异或门、第三选择器、加减法电路;

25.所述第一符号剥离电路用于对量化好的对数似然比a进行符号位和模值位的分离得到符号位sign(a)和模值mag(a),并将符号位sign(a)输入至第一异或门,将模值mag(a)输出至第三选择器;

26.所述第二符号剥离电路用于对量化好的对数似然比b进行符号位和模值位的分离得到符号位sign(b)和模值mag(b),并将符号位sign(b)输入至第一异或门,将模值mag(b)输出至第三选择器;

27.所述加减法电路用于接收对数似然比a和对数似然比b的输入,处理后将a和b加减法结果的最终的进位位cn和借位位bn输出至第二异或门,并将a和b的差信号作为u

s

取1时g函数的函数值g(u

s

=1)_out,将a和b的和信号作为u

s

取0时g函数的函数值g(u

s

=0)_out;

28.所述第三选择器用于根据模值mag(a)、模值mag(b)、进位位cn和借位位bn,选出值mag(a)和mag(b)中模值较小的一个作为f函数的模值输出mag(f)。

29.在一个具体实施方式中,所述路径度量值计算模块的路径度量值计算公式为:

[0030][0031]

其中,

[0032]

(sign为取符号函数),

[0033][0034]

对于信息比特的半决为:

[0035]

本发明同时提供一种基于预处理和简化存储的极化码译码方法,其特征在于,包括如下步骤:

[0036]

计算各个路径中每个译码比特对应的对数似然比;

[0037]

根据对应路径所译比特的对数似然比,计算相应路径的路径度量值;

[0038]

对每个所述路径度量值进行排序,得到排序路径信息;

[0039]

所述路径扩展与缓存模块,用于接收到排序路径信息后,将所述排序路径信息按顺序并行保存,同时按照收到的排序信息,对之前存储的路径进行复制和扩展后发送至剪枝模块;

[0040]

对复制和扩展的路径进行剪枝,根据列表大小保留所需要的路径,并将保留的路径,发送至并行的部分和计算模块;

[0041]

将已经译出的码子作为输入,通过异或操作和赋值操作,则可得到相应级数的部分和信号,并将部分和信号输出至所述sc译码模块作为下一轮sc译码模块的选通信号,直至n次循环结束后,对得到的译码结果进行输入,其中,n为码长。

[0042]

本发明同时提供一种电子设备,包括处理器、通信接口、存储器和通信总线,其中,处理器,通信接口,存储器通过通信总线完成相互间的通信;

[0043]

存储器,用于存放计算机程序;

[0044]

处理器,用于执行存储器上所存放的程序时,实现权利要求6所述的方法步骤。

[0045]

本发明同时提供一种计算机可读存储介质,所述计算机可读存储介质内存储有计算机程序,所述计算机程序被处理器执行时实现权利要求6所述的方法步骤。

[0046]

本发明的有益效果:

[0047]

本发明的基于预处理和简化存储的极化码译码器利用预处理和树形流水结构等简化方法,设计出的硬件复杂度小,译码延时低,误码率低,硬件面积低,从而能够提高译码性能。

[0048]

以下将结合附图及实施例对本发明做进一步详细说明。

附图说明

[0049]

图1是本发明实施例提供的一种基于预处理和简化存储的极化码译码器模块框图;

[0050]

图2是本发明实施例提供的sc译码模块电路示意图;

[0051]

图3是本发明实施例提供的fg函数处理单元示意图;

[0052]

图4是本发明实施例提供的fg函数运算电路示意图;

[0053]

图5是本发明实施例提供的路径度量值计算模块电路示意图;

[0054]

图6是本发明实施例提供的部分和计算电路示意图;

[0055]

图7是本发明实施例提供的部分和计算模块迭代示意图;

[0056]

图8是本发明实施例提供的部分和计算模块输入输出示意图。

[0057]

图9是本发明实施例提供的一种电子设备示意图。

具体实施方式

[0058]

下面结合具体实施例对本发明做进一步详细的描述,但本发明的实施方式不限于此。

[0059]

实施例一

[0060]

请参见图1,图1是本发明实施例提供的一种基于预处理和简化存储的极化码译码器模块框图,包括依次连接的sc译码模块、路径度量值计算模块、路径度量值排序模块、路径扩展与缓存模块、剪枝模块和部分和计算模块;

[0061]

所述sc译码模块,用于计算各个路径中每个译码比特对应的对数似然比;

[0062]

所述路径度量值计算模块,用于根据对应路径所译比特的对数似然比,计算相应路径的路径度量值;

[0063]

所述路径度量值排序模块,用于每个所述路径度量值进行排序,得到排序路径信息;

[0064]

所述路径扩展与缓存模块,用于接收到排序路径信息后,将所述排序路径信息按顺序并行保存,同时按照收到的排序信息,对之前存储的路径进行复制和扩展后发送至剪枝模块;

[0065]

所述剪枝模块用于对复制和扩展的路径进行剪枝,根据列表大小保留所需要的路径,并将保留的路径,发送至并行的部分和计算模块;

[0066]

所述部分和计算模块用于将已经译出的码子作为输入,通过异或操作和赋值操作,则可得到相应级数的部分和信号,并将部分和信号输出至所述sc译码模块作为下一轮sc模块的选通信号,直至n次循环结束后,对得到的译码结果进行输入,其中,n为码长。

[0067]

本发明的基于预处理和简化存储的极化码译码器利用预处理和树形流水结构等简化方法,设计出的硬件复杂度小,译码延时低,误码率低,硬件面积低,从而能够提高译码性能。

[0068]

在一个具体实施方式中,请参见图2,图2是本发明实施例提供的sc译码模块电路示意图,所述sc译码模块为树形流水型结构,包括依次连接的第一级fg函数处理电路1、第二级fg函数处理电路2、第三级fg函数处理电路3;

[0069]

所述第一级fg函数处理电路1包括四个并行的fg函数处理单元11,用于接收量化好的八个对数似然比,处理后将得到的四个13位宽的内部对数似然比输出至第二级fg函数处理电路2;

[0070]

所述第二级fg函数处理电路2包括两个并行的fg函数处理单元11,用于接收四个13位宽的内部对数似然比,处理后将得到的两个14位宽的内部对数似然比输出至第三级fg函数处理电路3;

[0071]

所述第三级fg函数处理电路3包括一个fg函数处理单元11,用于接收两个14位宽的内部对数似然比,处理后将得到的一个15位宽的内部对数似然比输出至路径度量值计算模块。

[0072]

具体的,将量化后的对数似然比两两输入到第一级fg pe模块,该模块根据输入的两个对数似然比,计算出f函数的输出f_out和g函数分别在u

s

=0和u

s

=1下的两个输出g(u

s

=0)_out和g(u

s

=1)_out,f_out经过延时电路delay,传入到函数选择操作用到的选择器mux。g(u

s

=0)_out和g(u

s

=1)_out则先经过一个选择器mux后,由部分和信号u

s

作为选择信号选出当前的g函数的输出后,再输入到函数选择操作的选择器mux,再由函数选择信号sel选出当前应用的函数输出,传入第二级fg pe单元,重复此操作直到最后一级,得到需要的对数似然比信号llr。

[0073]

在一个具体实施方式中,请参见图3,图3是本发明实施例提供的fg函数处理单元示意图,每个所述fg函数处理单元11均包括:一个fg函数运算电路111、延时器112、第一选择器113和第二选择器114;

[0074]

所述fg函数运算电路111的f函数输出端连接延时器112输入端、fg函数运算电路111的g函数输出端连接第一选择器113;所述延时器112输出端和所述第一选择器113输出端连接第二选择器114输入端。

[0075]

在一个具体实施方式中,请参见图4,图4是本发明实施例提供的fg函数运算电路示意图,fg函数运算电路111包括:第一符号剥离电路1111、第二符号剥离电路1112、第一异或门1113、第二异或门1114、第三选择器1115、加减法电路1116;

[0076]

所述第一符号剥离电路1111用于对量化好的对数似然比a进行符号位和模值位的分离得到符号位sign(a)和模值mag(a),并将符号位sign(a)输入至第一异或门1113,将模值mag(a)输出至第三选择器1115;

[0077]

所述第二符号剥离电路1112用于对量化好的对数似然比b进行符号位和模值位的分离得到符号位sign(b)和模值mag(b),并将符号位sign(b)输入至第一异或门1113,将模值mag(b)输出至第三选择器1115;

[0078]

所述加减法电路1116用于接收对数似然比a和对数似然比b的输入,处理后将a和b加减法结果的最终的进位位cn和借位位bn输出至第二异或门1114,并将a和b的差信号作为u

s

取1时g函数的函数值g(u

s

=1)_out,将a和b的和信号作为u

s

取0时g函数的函数值g(u

s

=0)_out;

[0079]

所述第三选择器1115用于根据模值mag(a)、模值mag(b)、进位位cn和借位位bn,选出值mag(a)和mag(b)中模值较小的一个作为f函数的模值输出mag(f)。

[0080]

具体的,两个输入的对数似然比a,b都先并行的进入符号剥离电路(sign peeling element)中,得到a的符号位sign(a)和mag(a),以及b的符号位sign(b)和mag(b)。将sign(a)和sign(b)送入上方的异或门电路进行异或操作,得到f函数的符号位sign(f)。mag(a)和mag(b)信号,则作为输入,接到下方的01选择器的输入端。而另一方面,a和b信号本身,又作为输入,参与到下方的加减法电路type 1pe电路中,加减运算得到的进位位和借位位的最高位作为输入信号,传入type 1pe上方的异或逻辑电路中,其异或结果min作为上方01选择器的选择信号,选出f函数输出的模值mag(f),并且与sign(f)一同输入到融合处理模块(merge,mer)而加减运算的得出的和信号sum、差信号diff则作为g函数两种结果输出g(u

s

=0)_out和g(u

s

=1)_out。

[0081]

在一个具体实施方式中,所述路径度量值计算模块的路径度量值计算公式为:

[0082][0083]

其中,

[0084]

(sign为取符号函数),

[0085][0086]

对于信息比特的半决为:

[0087]

对于上述公式的具体计算电路,请参见图5,图5是本发明实施例提供的路径度量值计算模块电路示意图,其最大的优势就是可以用一个电路同时计算两条扩展路径的度量值。前一比特的路径度量值和现译比特的对数似然比llr作为输入。llr先进行取模运算后与进行求和运算,得到的和信号作为后边选择器mux 1和mux 2的输入信号。第一个选择器mux 1的另外两个输入为和正无穷+∞。第二个选择器mux 2的另一个

信号为两个选择器都由选通信号sel选择输出信号,得到扩展路径的路径度量值。

[0088]

实施例二

[0089]

本实施例以n=8位polar码,列表宽度为l=4为例,简要说明具体流程:

[0090]

(1)对接收端(信道端)收到的对数似然比信息进行量化,量化方案采用12位的补码,最高位为符号位。得到了如附图2中的码,最高位为符号位。得到了如附图2中的其均为量化过后的对数自然比。

[0091]

(2)将已经量化好的对数似然比,每8个为一组,送入4并行的如附图2的树形流水型结构的sc译码电路的fg函数处理电路(fg process element,fg pe)的数据输入端,并拉高使能电平,开始译码。

[0092]

现有的sc译码模块往往需要大量寄存器来存储内部对数似然比,供给之后每个码子的内部迭代,并且需要额外设计地址计算电路来确定内部对数似然比的存储和读取地址,这给工程实现带来负担。对此,改进的设计技术如下:

[0093]

对于大面积的对数似然比存储模块和需要额外设计的迭代控制、地址计算和读取模块,选用的改进设计方案是缩短码长,用短码长的极化码,缩短迭代计算的级数,并且采用树形流水结构,如附图2,第在i(i=2n

‑

1,n=1,2

……

)次译码时遍历整个树形结构,只将最后一级的得出的最终三个数据保存,通过选择信号,选择正确的一个送入度量值计算模块,其他级得到的数据均不保留。并且利用极化码本身的译码特性,在第i+1次译码时,只需要改动最后一级的选择信号,就可以直接获得此次的结果。此举取消了数据存储电路,由于流水结构,也并不需要地址计算和控制电路。并且,由于短码的作用,即使每第i个码子都需要遍历整个树形结构,但由于树的级数很小,所以相比于长码所需的庞大辅助电路,依旧能带来硬件面积上的缩减。

[0094]

(3)sc译码模块根据输入的8个对数似然比,两两为一组输入参数,输入到附图2中第一级(stage 1)的fg pe中,进行计算,具体的迭代计算公式如下:

[0095]

f(a,b)=sign(a)sign(b)min(|a|,|b|)

[0096][0097]

其中a,b为相应的量化过的对数似然比,u

s

为由附图6示意中反馈回来的部分和信号。

[0098]

f和g函数的详细设计技巧、结构叙述如下:

[0099]

a.对于简化迭代公式的预处理设计迭代中使用的f和g函数如下:

[0100]

f(a,b)=sign(a)sign(b)min(|a|,|b|)

[0101][0102]

发现其中g函数存在指数运算给硬件实现带来困难,改进的方案是使用预处理的方式,在执行g函数时,将g函数的两种取值都预先并行计算,并将参数u

s

视作选择器的选择信号参与函数运算,而不是指数函数。即:当u

s

取0时,g(a,b,u

s

)=a+b,当u

s

取1时,g(a,b,u

s

)=

‑

a+b。

[0103]

b.对于f和g函数的联合简化设计

[0104]

若是单独设计f函数和g函数的运算电路,虽实现起来简单可行,却在硬件效率上

和电路简化上并无优势,改进的技术将f函数的比较电路和g函数的加减法电路联系在一起,将g函数的运算结果中的进位信号和借位信号做异或处理,作为f函数中比较电路的选择信号。

[0105]

具体的f函数和g函数运算模块如附图3。进入的量化好的数据a,b,先进入符号剥离电路(signprocess element,spe),进行符号位和模值位的分离,取a和b的符号位sign(a)、sign(b),送入附图3中最上方的异或门中,得到f函数运算结果的符号位sign(f),而a和b的模值mag(a)、mag(b)则作为下方比较器的输入。

[0106]

另一方面,a和b也作为g函数的输入,连接到最下方的加减法电路type pe1中,输出的和信号u

s

取0和是的g函数值g(u

s

=0)_out,输出的差信号作为u

s

取1时g函数的函数值

[0107]

g(u

s

=1)_out,并从中引出a和b加减法结果的最终的进位位cn和借位位bn,输入到加减法电路上方的异或门中,异或结果作为选择器的选择信号,连接到f函数模块的选择器,选出a和b中模值较小的一个。作为f函数的模值输出mag(f)。

[0108]

至此,就可以得到经过预处理的f函数和g函数的13位宽的函数值,位宽加1是为了防止超出量程。

[0109]

经过第一级的迭代计算过后,根据函数控制逻辑,得到了4个13位宽的内部对数似然比,这四个数据,同样两两为一组,输入到附图2中的第二级的f和g函数的计算电路fgpe中,具体电路设计同第一级,只是位宽加1,防止数据超出量程。随后得到的14位宽的内部对数似然比,输入到如附图2中的第三级的fgpe中,再通过迭代计算,辅以函数选择等逻辑控制信号sel,就可以得到第i(i=2n

‑

1,n=1,2

……

)个15位宽的信息位的对数似然比。

[0110]

(4)将sc译码模块计算出的对数似然比,送入如附图4所示的度量值计算电路中,该电路根据输入的对数似然比信息,是否为冻结比特位信息,以及01路径的扩展信息,和前一位的路径度量值,计算出当前信息位的路径度量值。具体计算公式如下:

[0111][0112]

其中:

[0113]

(sign为取符号函数)

[0114][0115]

对于信息比特的半决为:

[0116]

注意到只有当u

i

的估计值为1时,才会出现无穷大结果,所以在估计值为0时,省去了对其是否为冻结比特的判断。在收到当前比特的对数似然比后,对其进行取模操作,再与前一位的路径度量值做加法运算后,输入到两个并行的选择器中,其中上方的选择器用来计算估计值取1时的路径度量值,下方的选择器用来计算估计值取0时的路径度量值。通过sel信号,选出正确的路径度量值运算结果,送入路径度量值的排序模块。

[0117]

(5)排序模块在收到n(n=2,4,8)个路径度量值之后,进行由小到大的排序,保存当前得出的路径度量值,作为下一个对数似然比输入时的计算参数,同时,保存各个路径度

量值所对应的的u

i

的估计值,按照其代表的路径度量值顺序,送入路径缓存模块。

[0118]

(6)路径缓存模块在接收到排序模块送来的路径信息后,将其按顺序并行保存,同时按照收到的排序信息,对之前存储的路径进行复制和扩展。送入剪枝模块。

[0119]

(7)剪枝模块对步骤6中经历了复制和扩展的路径进行剪枝,根据列表大小保留所需要的路径。并将保留的路径,送入并行的部分和计算模块。

[0120]

(8)部分和计算模块的设计思路如图6所示,将已经译出的码子作为输入,通过异或操作和赋值操作,则可得到相应级数的部分和信号,相应的迭代以及延时电路如图7所示。u

n

‑1结构产生的奇数次信号,输入到延时模块delay中,延时2

n

‑2‑

2个时钟后,输入到u

s pe模块,其中log2n

‑

n+1为此时的级数,偶数次信号,不用经过延时,直接输入到相同uspe模块,经过u

s pe模块处理过后的信号,再经过选择器后,便可得到相应级数的部分和。其中u

s pe模块的局部示意图如图8所示。

[0121]

(9)步骤8中生成的部分和信号,作为下一轮sc模块的运算参数,反馈到附图2中sc模块的选择器上,作为选通信号,参与sc算法的迭代,若此次为第偶数次运算,则只需选通最后一级即可。

[0122]

至此,一轮循环结束,接下来的译码过程同理进行,待n(n为码长)次循环结束后,便可得到译码结果。

[0123]

实施例三

[0124]

本发明同时提供一种译码方法,该方法整体算法如下:

[0125]

对于一个参数为的极化码,n表示极化码的码长,k表示极化码信息位的长度,a表示传输的信息比特的信道位置索引的集合,a

c

表示传输的固定比特的信道位置索引的集合,表示传输的固定比特向量。

[0126]

另:对于向量表示向量的第到b位元素。α

i

表示中的第i位元素。

[0127]

原始信息向量可以分为两个部分,一部分是表示要传输的信息比特向量另一部分是表示要传输的固定比特的向量原始信息向量作为输入信号输入到合成信道w

n

中,合成信道的输出为信道转移概率密度为

[0128]

首先对原始信息向量执行sc算法。sc算法的作用就是通过观测信号来得到原始信息向量的估计值

[0129]

其中信道转移概率函数为:

[0130][0131]

表示码子符号集合,表示信道w

n

中的第i个子信道。

[0132]

对信道序号i从1到n取值,对于i∈{1,2,

…

,n},比特u

i

的估计值可以根据接收信号和部分估计序列通过计算当或时路径的度量值进行判断。各个比特

不会再被简单的估计成0或1中的某一个,而是将其全部都保留。这一步骤成为路径的扩展。而扩展之后的每条路径,都拥有根据其自身的对数似然比计算出的路径度量值。在判决阶段,将l条路径的按照其路径度量值大小进行排序,选择路径度量值最小的一条路径输出。其中l表示scl算法中的列表宽度。

[0133]

定义对数似然比(log

‑

likelihood ratio,llr)为

[0134][0135]

另定义f和g函数如下:

[0136][0137][0138]

其中u

s

∈(0,1),表示部分和信号。

[0139]

llr的递归运算借助f和g函数表示如下:

[0140][0141][0142]

(6)向量信号的下标o和e表示取其奇序号元素或其偶序号元素。符号表示按位模2求和。

[0143]

当n=1时,表示递归到达信道端,递归终止,此时:

[0144][0145]

根据公式(2)~公式(7),可以得到各个扩展比特的对数似然比。根据下式计算相应的路径度量值(path metric,pm):

[0146][0147]

其中l和i为分别为正在译码的路径序号和比特序号,且:

[0148]

(sign为取符号函数)

ꢀꢀꢀ

(9)

[0149][0150]

对于信息比特的半决为:

[0151]

[0152]

上述算法的伪代码可表示为如下:

[0153]

算法伪代码如下:

[0154]

for(i=0;i≤n;i++)

[0155]

{

[0156]

根据sc算法计算信道的对数似然比。

[0157]

对现译比特进行路径扩展。

[0158]

对扩展后的路径计算相应的路径度量值。

[0159]

对得到的路径度量值进行从小到大排序。

[0160]

if路径数量>列表宽度lthen

[0161]

剪枝

[0162]

部分u

s

和计算

[0163]

}

[0164]

输出结果。

[0165]

实施例四

[0166]

本发明实施例还提供了一种电子设备,如图9所示,包括处理器、通信接口、存储器和通信总线,其中,处理器,通信接口,存储器通过通信总线完成相互间的通信;

[0167]

存储器,用于存放计算机程序;

[0168]

处理器,用于执行存储器上所存放的程序时,实现实施例三所述的方法步骤。

[0169]

本发明同时提供一种计算机可读存储介质,所述计算机可读存储介质内存储有计算机程序,所述计算机程序被处理器执行时实现实施例三所述的方法步骤。

[0170]

上述电子设备提到的通信总线可以是外设部件互连标准(peripheral component interconnect,pci)总线或扩展工业标准结构(extended industry standardarchitecture,eisa)总线等。该通信总线可以分为地址总线、数据总线、控制总线等。为便于表示, 图中仅用一条粗线表示,但并不表示仅有一根总线或一种类型的总线。

[0171]

通信接口用于上述电子设备与其他设备之间的通信。

[0172]

存储器可以包括随机存取存储器(randomaccess memory,ram),也可以包括非易失性存储器(non

‑

volatile memory,nvm),例如至少一个磁盘存储器。可选的,存储器还可以是至少一个位于远离前述处理器的存储装置。

[0173]

上述的处理器可以是通用处理器,包括中央处理器(central processing unit,cpu)、网络处理器(network processor,np)等;还可以是数字信号处理器(digital signal processing,dsp)、专用集成电路(application specific integrated circuit,asic)、现场可编程门阵列(field

‑

programmable gate array,fpga)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件。

[0174]

本发明实施例提供的方法可以应用于电子设备。具体的,该电子设备可以为:台式计算机、便携式计算机、智能移动终端、服务器等。在此不作限定,任何可以实现本发明的电子设备,均属于本发明的保护范围。

[0175]

对于装置/电子设备/存储介质实施例而言,由于其基本相似于方法实施例,所以描述的比较简单,相关之处参见方法实施例的部分说明即可。

[0176]

应用本发明实施例所提供的终端设备,可以展示专有名词和/或固定词组供用户

选择,进而减少用户输入时间,提高用户体验。

[0177]

该终端设备以多种形式存在,包括但不限于:

[0178]

(1)移动通信设备:这类设备的特点是具备移动通信功能,并且以提供话音、数据通信为主要目标。这类终端包括:智能手机(例如iphone)、多媒体手机、功能性手机,以及低端手机等。

[0179]

(2)超移动个人计算机设备:这类设备属于个人计算机的范畴,有计算和处理功能,一般也具备移动上网特性。这类终端包括:pda、mid和umpc设备等,例如ipad。

[0180]

(3)便携式娱乐设备:这类设备可以显示和播放多媒体内容。该类设备包括:音频、视频播放器(例如ipod),掌上游戏机,电子书,以及智能玩具和便携式车载导航设备。

[0181]

(4)其他具有数据交互功能的电子装置。

[0182]

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

[0183]

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。此外,本领域的技术人员可以将本说明书中描述的不同实施例或示例进行接合和组合。

[0184]

尽管在此结合各实施例对本申请进行了描述,然而,在实施所要求保护的本申请过程中,本领域技术人员通过查看所述附图、公开内容、以及所附权利要求书,可理解并实现所述公开实施例的其他变化。在权利要求中,“包括”(comprising)一词不排除其他组成部分或步骤,“一”或“一个”不排除多个的情况。单个处理器或其他单元可以实现权利要求中列举的若干项功能。相互不同的从属权利要求中记载了某些措施,但这并不表示这些措施不能组合起来产生良好的效果。

[0185]

本领域技术人员应明白,本申请的实施例可提供为方法、装置(设备)、或计算机程序产品。因此,本申请可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式,这里将它们都统称为“模块”或“系统”。而且,本申请可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、cd

‑

rom、光学存储器等)上实施的计算机程序产品的形式。计算机程序存储/分布在合适的介质中,与其它硬件一起提供或作为硬件的一部分,也可以采用其他分布形式,如通过internet或其它有线或无线电信系统。

[0186]

本申请是参照本申请实施例的方法、装置(设备)和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

[0187]

这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

[0188]

这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

[0189]

以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1