直接调制合成器的高级多增益校准的制作方法

[0001]

本发明涉及锁相环(pll’s,phase-locked loops),特别涉及使用两个增益值的压控振荡器(vco,voltage-controlled oscillator)的增益校准。

背景技术:

[0002]

先进的无线通信系统通常需要精确的时钟,该时钟被调制以携带数据。可以使用带有压控振荡器(vco)的锁相环(pll)来生成时钟,压控振荡器(vco)将输入电压转换成频率取决于输入电压的输出时钟。

[0003]

一些通信标准采用高频率,并且可以从一个频道跳到另一个频道,以避免传输干扰或其它阻碍。因此,vco可能需要运行在一个较宽的频率范围上,并需要一个大增益。大的vco增益通常需要大的芯片面积,因此需要更高的制造成本和功率。

[0004]

pll可用于生成一个时钟,然后通过诸如上变频混频器(up-conversion mixer)和数模转换器(dac,digital-to-analog converter)将数据与pll输出后的时钟混合。但是,dac会引入同相和正交信号不匹配(iq不匹配)。dac和混频器所需的芯片面积增加了成本和功率要求。

[0005]

也可以使用两点调制pll。数据被注入pll本身,使pll输出的是数据调制输出,而不是一个固定时钟。使用两点调制pll时,不再需要上变频混频器及其dac。两点调制pll还可以提高噪声性能。从功率放大器到vco的拉动效应可以减轻。

[0006]

图1显示一种现有技术的两点调制pll。锁相环(pll)由相频检测器42、电荷泵44、环路滤波器46、加法器72、vco 41和多模分频器(multi-mode divider)52组成。来自vco 41的输出时钟fout通过多模分频器52进行分频,并通过相频检测器42与一个参考时钟fref进行比较。比较结果使电荷泵44对环路滤波器46进行充电或放电,从而调整vco 41的输入电压。vco 41通过调整输出时钟fout的频率来响应其输入电压的变化。

[0007]

数据用于调制或编码来自vco 41的fout。数据在两个点注入到pll中。数据in1被施加到多模分频器52,而数据in2被输入到加法器72。相同的数据值施加到in1和in2,但in1可以是数据的数字表示,而in2可以是表示相同数据的模拟电压。in1使多模分频器52对其除数(divisor)进行调制,而in2直接调整vco 41的输入电压。由于in2施加在vco 41的输入端,所以它具有高通特性,而in1较早施加在pll环路中,具有低通特性。由in1引入的多模分频器52中除数的调制必须经过相频检测器42、电荷泵44和环路滤波器46,然后才能到达注入in2的加法器72,因此in1比in2具有更大的固有延迟。

[0008]

图2a-c是频率响应图,突出了两点调制pll中的增益不匹配。由于in2不通过相频检测器42、电荷泵44和环路滤波器46,因此其频率响应受vco 41的增益主导。

[0009]

图2a显示匹配良好的两点调制pll的曲线图。由于多模分频器52、相频检测器42、电荷泵44和环路滤波器46的延迟,in1的频率响应在较高频率时有所下降。这些延迟在in2中是不存在的,in2在高频时有很好的响应,但在低频时响应较差。因此,in1类似于低通滤波器,而in2类似于高通滤波器。

[0010]

由于相同的数据通过in1和in2,所以总频率响应是in1和in2的频率响应曲线的总和。如图2a所示,在增益匹配良好的情况下,该总响应在所有频率上都是比较平坦的。

[0011]

在图2b中,vco的增益k

vco

过高。vco 41的高增益极大地影响了in2的高频响应,而in1则保持不变,因为多模分频器52、相频检测器42、电荷泵44和环路滤波器46并没有因vco 41的增益变化而改变。总频率响应,即in1和in2的频率响应曲线之和,在交叉频率fc之后上升。总响应曲线在高频率时的跳变会导致信号失真。

[0012]

在图2c中,vco的增益k

vco

过低。vco 41的低增益降低了in2的高频响应,而in1的高频响应基本保持不变。总频率响应在交叉频率fc后下降,因为高频响应由通过in2和vco 41注入的数据主导。

[0013]

vco 41的增益取决于工艺,并因芯片而异。工艺、电源电压和温度(pvt,process,power-supply voltage,and temperature)的变化会严重影响vco增益,从而影响频率响应,导致信号失真。在设计阶段,电路的设计可以使in1的低频响应与in2在典型pvt条件下的高频响应相匹配。

[0014]

增益校准通常用于调整pvt条件,并更好地匹配两点调制pll的高频和低频响应。通过对vco 41的增益进行良好的校准,in1的低频响应可以在一定范围的pvt条件下与in2的高频响应很好地匹配。

[0015]

有时会使用大面积电路进行校准,如adc’s、模拟比较器和双环滤波器等。可以使用高频计数器,但这些计数器会在工作频率较高的时候消耗很大的功率。单输入vco在线性度和调谐范围上有一定的限制。校准单元通常使用乘法器和除法器,这些都是大型复杂电路。大型电路的芯片面积较大,增加了成本和功耗,因此不可取。诸如模拟比较器和adc之类的精密电路可能需要大型元件才能达到目标精度。

[0016]

随着系统的升温,pvt可能会继续变化,从而迫使重新校准和更多延迟。有些系统是闭环,在校准期间,pll环路滤波器保持连接到vco输入。这是不可取的,因为环路会有额外的稳定时间。开环系统在校准期间将pll环路滤波器与vco输入断开连接,从而加快了校准时间。

[0017]

当需要高精度时,vco校准中使用的dac可能难以实施。有时需要10位(bit)以上的dac。这些分辨率超过10位的dac非常昂贵,而且难以实施。因此,希望缩小用于校准的dac的尺寸。

[0018]

期望有一种具有开环校准系统的两点调制pll。最好是不使用精密模拟比较器的校准系统。两点调制pll需要的是全数字校准单元。两点调制pll最好是使用双输入vco,以打破线性度和调谐范围之间的权衡。需要一个不使用乘法器和分频器(divider)的校准单元。希望有一个低功耗、低面积的校准单元。

附图说明

[0019]

图1显示一种现有技术的两点调制pll。

[0020]

图2a-c是显示突出两点调制pll中的增益不匹配的频率响应图。

[0021]

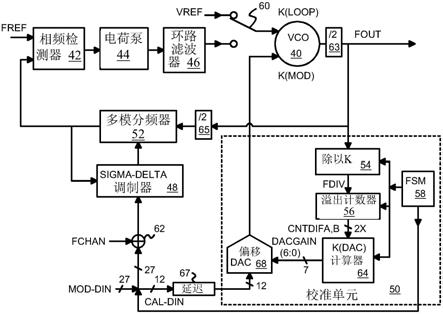

图3是使用一个溢出计数器和一个偏移dac用两个增益值来校准vco增益的两点调制pll的框图。

[0022]

图4是双输入vco的示意图。

[0023]

图5显示一个环路滤波器。

[0024]

图6是突出双增益点校准的曲线图。

[0025]

图7a-7c显示图3的两点调制pll的双增益点校准流程图。

具体实施方式

[0026]

本发明涉及用于pll的增益校准的改进。呈现以下描述以使得本领域普通技术人员能够制造和使用如在特定应用及其要求的上下文中提供的本发明。对优选实施例的各种修改,对于本领域普通技术人员来说,将是显而易见的,并且这里定义的一般原则可以应用于其他实施例。因此,本发明并不打算局限于所示和描述的特定实施例,而是要给予与本发明所披露的原则和新颖特征相一致的最广泛的范围。

[0027]

图3是使用溢出计数器和偏移dac用两个增益值来校准vco增益的两点调制pll的框图。发明人没有使用昂贵的、高精度的dac,而是使用具有可变增益的偏移dac。在校准期间,dac的增益被设置为2个不同的值。本发明人不以单个增益值执行校准,而是以2个不同的增益值执行2次校准。vco具有两个不同的增益值,其中用于pll环路的k

loop

通过电荷泵44,而用于高通调制的k

mod

通过偏移dac 68。pll环路的增益比通过偏移dac 68的调制路径高得多,所以k

loop

比k

mod

大得多。拥有k

loop

和k

mod

两个不同的增益,可以松弛相位噪声和线性度之间的权衡。通过使用来自偏移dac 68的vco 40中的调制路径的较低增益来改善线性度,而通过vco 40中来自相频检测器42、电荷泵44、环路滤波器46的pll路径中的较高增益来改善相位噪声抗扰性。

[0028]

在校准期间,不使用模拟比较器,而是溢出计数器56对vco输出fout的脉冲进行计数。为了降低功耗,在对溢出计数器56进行时钟控制之前,fout首先被分频器54除以k。给定时间段内的脉冲计数的差值(cntdif,counts for a given period of time)输入到k(dac)计算器64,然后计算器64输出一个数字值dacgain(6:0)。dacgain(6:0)是偏移dac 68的增益控制。偏移dac 68将数字数据mod转换为模拟信号,该模拟信号被施加到vco 40的增益控制输入端。校准单元50还包括一个控制器,例如有限状态机(fsm,finite state machine)58,用于控制校准操作,如随后在图7a-c所示。

[0029]

由相频检测器42、电荷泵44、环路滤波器46、开关60、vco40和多模分频器52形成锁相环(pll)。附加的分频器63、65被添加到环路中以进一步除以2。来自vco 40和分频器63的输出时钟fout再次被分频器65、然后被多模分频器52分频。多模分频器52的输出与参考时钟fref通过相频检测器42进行比较。比较结果使电荷泵44对环路滤波器46进行充电或放电,从而调整k

loop

输入电压至vco 40。vco 40通过调整输出时钟fout的频率来响应其k

loop

输入电压的变化。

[0030]

收发器所使用的指定频率fcs由fchan表示。fchan可以是指定频率fcs的载波,其被施加到加法器62上,由mod-din调制,然后将调制后的载波施加到sigma-delta(σ-δ)调制器48。sigma-delta调制器48产生一个信号,使多模分频器52使用的除数抖动,尽管多模分频器52使用整数除数,但因此可以实现分数除数值。整数除数例如n和n+1,可以在几个周期内取平均值,以实现所需的分数除数,允许从fref产生更多的任意的fout值。当两个整数除数的值由sigma-delta调制器48和多模分频器52交替产生时,pll环路会使所产生的变化平滑。

[0031]

当指定一个新的频率时,fchan改变为新频率的载波,并可能使多模分频器52改变其除数,而sigma-delta调制器48改变其抖动周期。

[0032]

两点调制由调制数据mod-din提供,其在多模分频器52和vco 40两点处被注入到pll环路中。一个27位调制值mod-din通过加法器62加入到频率载波fchan中,然后由sigma-delta调制器48进行抖动,再由多模分频器52注入到环路中。

[0033]

27位数据mod-din的12个最高有效位(msbs,most-significant bits)经延迟67延迟,由偏移dac 68转换为模拟电压,然后输入到vco 40的增益控制输入端。vco 40的增益控制kmod输入可以调整延迟元件,例如vco 40的内部节点上的可变电容,或者可以调整vco 40内部各级的电源电压。vco 40的增益控制输入具有较低的增益和较好的线性度,而从环路滤波器46和开关60输入到vco 40的环路输入具有较高的增益,但线性度较差。

[0034]

偏移dac 68有一个接收调制数字数据mod-din的12位数据输入和一个从k(dac)计算器64接收的dacgain(6:0)的7位增益输入。偏移dac 68的增益输入对偏移dac68的输出电压进行缩放。因此,dacgain(6:0)定义了偏移dac68的输出电压的最大波动。接收mod-din的12位数据输入从数字转换为模拟电压,而增益输入对模拟电压进行缩放。

[0035]

当dacgain(6:0)处于最低设定0000000时,偏移dac 68的增益大于0。因此,偏移dac 68具有一个增益偏移,使其增益永远不会是零增益,因此,偏移dac 68总是调制mod-din输入信号。如果偏移dac 68的增益降到零,那么会破坏mod-din输入信号的调制,使这些调制信号无法到达vco 40。在偏移dac 68中有一个非零增益偏移,可以防止这种调制消除问题。

[0036]

在校准期间,开关60将vco40的k

loop

电压输入端连接到参考电压vref。在校准模式期间,来自环路滤波器46的连接被开关60断开。因此,校准是在开环配置中进行的。开环配置是可取的,因为校准稳定时间不依赖于通过整个pll环路的长延时。

[0037]

校准单元50通过计数脉冲来测量fout的频率。分频器54将fout除以k,其中k是一个至少为1的实数。分频器54的除以k的输出比fout慢,使溢出计数器56的工作速度更慢且功耗更低。全数字计数器的面积、功耗和成本均低于模拟比较器,而且不易受工艺变化的影响。

[0038]

有限状态机(fsm)58控制校准模式期间的操作顺序。在校准期间,fsm 58初始设置dacgain为1/4值,如0100000,这样,偏移dac 68的值为1/4k

dac(max)

。

[0039]

mod-din被禁用,取而代之是由校准单元50中的fsm 50作为校准数据cal-din驱动。然后,fsm 58使cal-din被设置至高电平11111111,(cal-din=ff),其通过偏移dac 68来控制vco 40的kmod增益。fsm 58在0.977毫秒(ms)周期过后,从溢出计数器56读取计数值,并存储该值。然后,fsm 58使cal-din被设置至低电平0000 0000,(cal-din=00),其再次通过偏移dac 68来控制vco 40的kmod增益。fsm 58在0.977毫秒期间过后,从溢出计数器56读取计数值,并存储该值。cal-din=ff和cal-din=00的计数值的差值为cntdif_a。fsm 58将cntdif_a输入到k(dac)计算器64。

[0040]

接下来,fsm 58将dacgain设置为四分之三的值,如1100000,使偏移dac68的值为3/4k

dac(max)

。然后重复进行校准,以得到cntdif_b。

[0041]

fsm 58使cal-din被设置至高电平11111111,(cal-din=ff)。fsm 58在0.977毫秒(ms)期间过后,从溢出计数器56读取计数值并存储该值。然后,fsm 58使cal-din被设置至

低电平0000 0000,(cal-din=00),其再次通过偏移dac 68来控制vco 40的kmod增益。fsm 58在0.977毫秒期间过后,从溢出计数器56读取计数值,并存储该值。当设置为3/4k

dac

时,cal-din=ff和cal-din=00计数值的差值为cntdif_b。fsm 58将cntdif_b输入到k(dac)计算器64。

[0042]

k(dac)计算器64接收2个计数差值,在1/4k

dac(max)

产生的cntdif_a和在3/4k

dac(max)

产生的cntdif_b。k(dac)计算器64可以从cntdif_a和cntdif_b,利用移位寄存器和分频器,在适当选择了各种参数的情况下,直接计算出k

dac

的校准值,k

dac(cal)

,如随后所述。因此,k(dac)计算器64可以使用简化逻辑,从两个计数差值cntdif_a、cntdif_b生成k

dac

的校准值k

dac(cal)

。

[0043]

k

dac

的校准值k

dac(cal)

,是应用于偏移dac 68的设置dacgain(6:0)。k(dac)计算器64将两个0.977ms期间的两个计数差直接转换为增益调整值dacgain(6:0)。当使用正确选择的参数时,不需要复杂的算术逻辑单元(alu)。除以2可由移位寄存器执行,且使用一个除法器。

[0044]

一旦校准结束,设置为k

dac(cal)

的dacgain(6:0)被施加到偏移dac 68上,以将mod-din的调制路径中的增益调整到vco 40的kmod输入。开关60闭合,以将环路滤波器46连接到vco 40,使正常的闭环pll操作得以发生。数据调制可以在mod-din上恢复。

[0045]

图4是双输入vco的示意图。vco 40是一个具有n沟道晶体管20、22交叉耦合栅极的差分放大器,其n沟道晶体管20、22的源极连接在一起,并连接到电流槽(current sink)28。上拉电阻24、26提供电流给n沟道晶体管20、22的漏极。由于n沟道晶体管20、22是交叉耦合的,所以它们会振荡。vco 40是双稳态的。

[0046]

振荡频率取决于rc延迟,特别是通过电阻24到晶体管20的漏极上的电荷电容(如变容二极管30、34)的延迟。该延迟通常与通过电阻26到晶体管22的漏极上的电荷电容(如变容二极管32、36)的延迟相匹配。

[0047]

变容二极管30、32用作可变电容器,其中电容由vco 40的loop输入控制,其增益为k

loop

。同样,变容二极管34、36用作可变电容器,其中电容由vco 40的mod输入控制,其增益为k

mod

。

[0048]

变容二极管30、32的尺寸可以大于变容二极管34、36的尺寸,因此,k

loop

比k

mod

大。变容二极管30、32、34、36被反向偏置,因此电流不会流过它们。

[0049]

图5显示一个环路滤波器。环路滤波器46可以以多种方式实现,例如简单的串联电阻和电容接地,或者通过更复杂的网络实现。图5显示了环路滤波器46的一个较复杂实施例。

[0050]

通过环路滤波器46的输入、输出端上的电容94、96,电荷储存在串联电阻90的两边。来自输入节点的电荷也通过电阻98储存在电容器98上。通过有三个电容器,将电荷存储在三个不同的网络节点上,从而增强了环路滤波器46的充放电功能。这种模拟pll的三阶环路滤波器比低阶网络具有更好的噪声和杂散抑制。

[0051]

图6是突出2增益点校准的曲线图。将频率差δfreq绘制为偏移dac 68的增益k

dac

的函数。

[0052]

频率差δfreq是指在dac输入的整个范围(从00到ff)上的vco输出频率fout。通过将cal-din设置为0000 0000来测量vco频率,然后在cal-din设置为1111 1111时再次测量。

[0053]

这个δfreq是偏移dac68的增益k

dac

的函数。较高的dac增益在dac输入范围内有较大的频率差。线77显示了δfreq和k

dac

之间的关系。线77随pvt的变化而变化,校准找到线77的斜率和y轴截距,这样就可以选择一个k

dac

的值,对指定的频率范围或频带产生一个期望的目标δf

t

。产生目标δf

t

的k

dac

就是校准后的增益值k

dac(cal)

。

[0054]

对两个不同的dac增益值重复进行校准。在第一点81,将dac增益设置为1/4k

dac(max)

,校准时测量的脉冲计数差值(δca或cntdif_a)决定了频率差δf

a

。在第二点83,dac增益被设置为3/4k

dac(max)

,校准时测量的脉冲计数差值(δcb或cntdif_b)决定了频率差δf

b

。从这两个点81、83,可以确定线77的斜率和y轴截距(δf

c

)。

[0055]

点81、83是双增益点校准的两个增益点。在每个点81、83处,针对增益输入dacgain的一个值,对dac数据输入cal-din的两个不同值测量频率(脉冲计数)。因此,总共进行了四次测量以进行两点校准。

[0056]

可以重新绘制图6的曲线图,其中dac设置dacgain(6:0)代替x轴上的k

dac

,脉冲计数差值δc代替y轴。

[0057]

双增益点校准原理

[0058]

可以设计两点调制pll,使在典型pvt条件下in1的低频响应与in2的高频响应相匹配。然后,可以加入增益校准,以针对当前pvt条件调整vco 40的增益。不是直接调整vco 40的增益k

mod

,而是调整偏移dac 68的增益k

dac

,因为调制路径的总增益是乘积

[0059]

k

mod

*k

dac

[0060]

特别地,通信协议或规范可规定,对于调制数据mod-din的最大变化而言最大频率偏差是多少。

[0061]

mod-din(max)*kmod*kdac(cal)+δfc=δfnbiot

[0062]

其中,mod-din是调制数据输入的最大值,kmod是环路滤波器变容二极管增益,kdac(cal)是计算出的增益,δfc是当kdac为零时的最小频率偏差,δfnbiot是指定的nb-iot频率偏差为+/-960khz的期望频率偏差。

[0063]

例如,mod-din的最大变化是从mod-din=00到mod-din=ff,通信协议规定,对于蓝牙低能量(ble)标准,频率偏差应为+/-250khz,或总计500khz,对于窄带物联网(nb-iot)标准,频率偏差应为+/-960khz,或总计1.92mhz,对于zigbee标准,频率偏差应为+/-500khz,或总计1mhz。

[0064]

在校准期间,mod-din=00被施加于vco 40,并进行脉冲计数,然后mod-din=ff被施加于vco 40,并进行另一次脉冲计数。脉冲计数的差值为cntdif。对两个增益值1/4k

dac(max)

(dacgain(6:0)=0100000)和3/4k

dac(max)

(dacgain(6:0)=1100000),重复此操作以获得cntdif_a和cntdif_b。

[0065]

然后从cntdif_a和cntdif_b计算出一个调整或校准值。该校准值dacgain(6:0)是一个要施加于偏移dac 68的值,将mod-din=00和mod-din=ff的频率调整到刚好相差1.0mhz(对于zigbee的+/-500khz的规格),或刚好相差500khz(对于蓝牙低能量(ble)的+/-250khz的规格)。当反馈除数和参考频率预设好后,可以用下面的公式(3)直接从cntdif_a和cntdif_b计算dacgain(6:0)。

[0066]

对于pll环路,vco 40的频率为

[0067][0068]

其中f

ref

是输入到相频检测器42的参考频率,k是分频器54的除数,cnt是来自溢出计数器56的脉冲计数,n

time

是计数时间段的参考频率时钟的周期数,例如在0.977毫秒内的fref周期数。2是由于分频器63将vco输出除以2。

[0069]

对应计数之差δc的频率差δf,如cntdif_a,为等式(1)

[0070][0071]

从图6中可以看出,从81点到83点的线77的斜率为:

[0072]

(δf

a-δf

b

)/(1/4k

dacmax

–

3/4k

dacmax

)

[0073]

从中点δf

t

,k

dac(cal)

到点83的线77的斜率为:

[0074]

(δf

t-δf

b

)/(k

dac(cal)

–

3/4k

dacmax

)

[0075]

这两个斜率必须相等。

[0076]

(δf

a-δf

b

)/(1/4k

dacmax

–

3/4k

dacmax

)=(δf

t-δf

b

)/(k

dac(cal)

–

3/4k

dacmax

)

[0077]

重新排列上述等式后,求出校准后的dac值k

dac(max)

,得到等式(2):

[0078][0079][0080]

其中δf

nbiot

是δf

t

,协议规范中的频率设置。

[0081]

对于预设时间段ntime中的选定设置f

ref

、k和周期,使用δf的前面的等式(2),我们可以将值代入等式(1)中,得到δf

a

,作为δc

a

,(cntdif_a)的函数,并得到δf

b

,作为δc

b

,(cntdif_b)的函数。

[0082]

对于7位dac,最大设置为128,所以k

dac(max)

可以设置为127。当输入参考频率f

ref

为38.4mhz,k为8时,时间周期可以选择为0.977ms,这样在这个时间周期内fref的周期数为37500(0.977ms=37500*(1/38.4mhz))。校准周期越长,精度越好,但需要较长的时间进行校准。当选择的频率n

t

为3.84mhz时,我们可以使用前面的等式求解k

dac(cal)

,得到等式(3):

[0083][0084][0085]

其中δc

a

是cntdif_a,δc

b

是cntdif_b。该等式需要乘以26,即2的幂,所以该乘法可以通过移位寄存器而不是全乘法器来实现。因此求解这个等式需要一个除法器、一个移位寄存器和一个加法器/减法器。对于特定的频率设置,当时间周期和k的值选定以得到上述等式(3)中的2的幂,k(dac)计算器64可以大大简化。特别地,2*k*fref/n是2的幂。

[0086]

在这个例子中,对于1.8ghz频段,+/-1.92mhz的调制频率具有两倍的总频差,即3.84mhz,所以δf

t

=3.84m。当k

dac

设定为最大dac设定值127的1/4,即32时,计数差δc

a

,即cntdif_a为184,δf

a

为3.0mhz;当k

dac

设定为最大dac设定值127的3/4,即96时,计数差δc

b

,

即cntdif_b为247,δf

b

为4.5mhz。然后求解上式(3)中的k

dac(cal)

,我们得到67。值67将由k(dac)计算器64产生,并施加到偏移dac 68作为校准的dac增益。这个值67将随着温度、工艺和电源电压的变化而变化,与本例中的标称值不同。

[0087]

对于其他频段,使用上述等式的其他实施例,可以用k(dac)计算器64计算,并且对每个频率设置,可以预选不同值的时间周期和k。

[0088]

图7a-7c是图3的两点调制pll的双增益点校准的流程图。在图7a中,在步骤102,开关60断开,使参考电压vref与vco40的电压输入端连接,打开pll回路。

[0089]

步骤104,fsm 58将dacgain(6:0)设置为0100000,并将cal-din设置为00000000。因此,增益被设置为最大值的1/4,即1/4k

dac(max)

。数据输入被设置为最低值。步骤106,在0.977毫秒的周期内的脉冲数由溢出计数器56计数并存储。该脉冲数由分频器63除以2,再由分频器54除以k。

[0090]

步骤105,fsm 58将cal-din设置为11111111。在步骤107,现在,数据输入被设置为最高值。在0.977毫秒的周期内的(fout/2k)脉冲数由溢出计数器56计数并存储。

[0091]

在步骤108,对于cal-din=00和cal-din=ff,存储的计数之差被计算为δc

a

,cntdif_a。cntdif_a是当增益设定为最大设定值的3/4或1/4k

dac(max)

时的脉冲计数之差。

[0092]

在图7b中,对于不同的增益值,即最大设定值的3/4或3/4k

dac(max)

,重复上述过程。

[0093]

步骤114,fsm 58将dacgain(6:0)设置为1100000,并将cal-din设置为00000000。现在将增益设置为最大值的3/4,即3/4k

dac(max)

。数据输入被设置为最低值。步骤116,在0.977毫秒的周期内的脉冲数再次由溢出计数器56计数并存储。

[0094]

步骤115,fsm 58将cal-din设置为111111 1111。现在,数据输入被设置为最高值。步骤117,在0.977毫秒的周期内的(fout/2k)脉冲数由溢出计数器56再次(第四次)计数并存储。

[0095]

步骤118,对于cal-din=00和cal-din=ff,存储的计数之差被计算为δc

b

,cntdif_b。cntdif_b是将增益设置为最大设定值的3/4或3/4k

dac(max)

时的脉冲计数之差。

[0096]

在图7c中,步骤120,k(dac)计算器64接收计数差值cntdif_a和cntdif_b(也称为δc

a

、δc

b

),使用完全等式(2)或简化等式(3),计算k

dac(cal)

。与计算出的k

dac(cal)

对应的dacgain(6:0)的设置为dacgain(cal),其可以使用k(dac)计算器64中的逻辑直接获得作为7位二进制值。

[0097]

步骤122,dacgain(cal)被施加到偏移dac68。调整通过偏移dac68的增益以进行校准,使调制数据mod-din经历偏移dac68的校准增益以及vco40的固定增益k

mod

,总增益为k

dac(cal)

*k

mod

。

[0098]

步骤110,开关60断开vref,并将来自环路滤波器46的电压施加到vco 40的输入端。使用通过校准调整的总增益,可以开始正常的闭环操作。变型实施方式

[0099]

已经描述了一种偏移dac,当dac校准输入被设置为最小值时,如0000000,其输出振幅为非零。在dac校准输入为0000000时其输出幅度为零的一个常规dac,可以防止0000000施加于dac校准输入。由于需要关闭电流镜源,因此难以在小增益范围内使用常规dac进行设计。常规dac的小幅度输出摆幅很可能没有用处。使用偏移dac可以提高期望输出摆幅上的分辨率。

[0100]

虽然已经描述了溢出计数器56产生计数差值cntdif_a和cntdif_b,但这些差值可以由k(dac)计算器64计算,并且让溢出计数器56只是将四个原始计数值报告给k(dac)计算器64。或者,溢出计数器56可以有减法功能,例如从第一计数值向下计数而不是在第二计数期间向上计数。那么最终的值就是一个差值,而不是第二个计数值。

[0101]

fsm 58可以不存储cal-din=ff和cal-din=00的计数值,而是只存储一个值,然后直接计算cntdif。fsm 58还可以使溢出计数器56在cal-din=ff期间向上(或向下)计数,并在cal-din=00期间向下(向上)计数,以便在第二计数周期结束后直接得到cntdif。

[0102]

本发明人还构思了一些其他实施例。例如,虽然已经显示了多模分频器52,但可以根据所需的输入和输出频率,用常规分频器代替。sigma-delta调制器48可以用整数n分频器代替,或者在某些实施例中可以删除。开关60可以用mos晶体管开关来实现。

[0103]

虽然已经描述了3/4k

dac(max)

和1/4k

dac(max)

的dac增益设置,但也可以选择其他值,如0.9和0.1

×

k

dac(max)

,或0.6和0.4

×

k

dac(max)

等。另外,点81、83不一定关于中心对称。诸如3/4、1/8

×

k

dac(max)

等增益值可以被代替。可以使用两个以上的点,用一条线或其他曲线来拟合这些点。

[0104]

虽然已经使用了完整设定值k

dac(max)

的3/4和1/4,但也可以使用其他更随意的校准点a、b,使用更通用的等式:

[0105][0106]

虽然已经描述了两个增益点,分别为最大增益的1/4和3/4,但可以测试三个或更多的增益点,并使用其中的最佳拟合线。

[0107]

该系统可用于各种应用和标准,如rf采样系统、ble、wifi、rfid标签等。来自k(dac)计算器64的校准增益值可以针对fref、k、n以及最大指定频率偏差(例如500khz、1mhz等)的不同值重新计算。当频道选择的载波fchan发生变化时,新频率的指示符可以使k(dac)计算器64根据新的参数值进行调整,例如,当发生频率变化时(如信道跳变)。

[0108]

cal-din可被限制在一个比校准范围更小的范围内。可对cal-din=00000000 0000和cal-din=1111 1111的整个二进制范围内进行校准,但在正常工作期间,mod-din可在整个范围内运行。mod-din和cal-din可以用二进制或其他排序系统(例如二进制补码)定义。在二进制补码中,最小的mod-din为1001 1001,最大的mod-din为0111111111,因为第一个位是符号位。二进制补码可以在输入到偏移dac68之前转换为二进制。偏移dac 68可以有不同数量的输入位和增益校准位,并且可以根据输入位数来调整其总体分辨率。

[0109]

例如,无线标准可以指定几个可以使用的频率,可以对多个频率进行校准以便在这些频率之间快速跳频。校准新频率时,可以保留先前校准的dacgain(6:0)的测量值,允许收发器在未来的某个时间跳回旧频率及其旧的dacgain(6:0)值,而不需要重新校准。

[0110]

虽然在可变增益vco的实施例中描述了可变电容器,但也可以使用其他可变延迟机制,例如可变电阻器、可变滤波器网络、延迟级的复用等。来自环路滤波器的vco的输入电压可以被施加到逆变器的电源节点上。逆变器的数量和类型可以变化,可以使用一对交叉耦合的逆变级,或者使用一个l-c振荡器,而不是三个或其他奇数个逆变器。

[0111]

变容器30、32、34、36可以是压控变容器、变容二极管、可变电容二极管、可变电抗二极管或其他具有反向偏压p-n结的器件,这些器件的宽度可变,因此耗尽区的大小随反向

偏压的变化而变化。还可以使用其他种类的可变电容器和电路。可以使用pmos反相模式变容器。在图4中,可以并联多个大小不同的变容器34,并且可以使用诸如ctl2(15:0)的配置设置来设置变容器34的标称尺寸和电容值。变容器34、36都可以由ctl2(15:0)控制,从而在切换频带时允许较大的电容变化。类似地,变容器30、32可以有许多并联的变容器,其配置信号ctl1(7:0)设置标称电容。然后,来自环路滤波器46的模拟信号会在该标称值附近改变变容器30、32的电容,以调整vco 40的电容和频率输出。这样,k

loop

和k

mod

可以针对不同的频段选择进行调节,从而使其支持的频段范围更广。

[0112]

虽然已经显示了0.977毫秒的时间段用于计数校准脉冲,但也可以用其他时间段代替。较短的时间段会减少校准时间,但精确度较低。较长的时间段可以进行更精确的测量,但延长了校准时间。

[0113]

可以在储存之前或储存之后修改脉冲计数,例如进行移位、除、乘或取其倒数。计数差可以是正数或负数,也可以定义为countmod1-countmod2或countmod2-countmod1。

[0114]

校准可以每天进行多次,并在温度变化、频率变化后或通过开机程序定期触发。

[0115]

dacgain(6:0)的值可以反转和倒置,或者vco 40可以要求一个正斜率增益值,而不是负斜率增益值。vco或其他元件可以根据这种改变的值定义进行调整。

[0116]

虽然已经显示fsm 58,但也可以使用其他种类的程序控制器(sequencer)或控制器,例如硬件、固件或混合控制器。参考电压vref可以是固定电压,例如vdd/2,或者可以使用带隙参考、分压器或其他参考电压产生器产生。

[0117]

可以在各个节点上增加附加元件,如电阻器、电容器、电感器、晶体管、缓冲器、分压器等,还可以有寄生元件。启用和禁用电路可以使用其他晶体管或其他方式来实现。可以增加传输门晶体管或传输门以实现隔离。可以添加反相器或额外的缓冲器。可以为某些元件使用独立的电源和地线。可以添加各种滤波器。低电平有效信号而不是高电平有效信号可以被取代。

[0118]

可在不同的节点上为各种目的增加额外的元件,如断电模式的切断开关、电压移位器、用于设置交流工作点的偏置电流等。逆变器可以用差分放大器来代替。可以使用各种参考电压或虚拟电源,而不是硬接地。

[0119]

虽然已经描述了二进制值,但也可以用其他编码方式代替,如十进制或格雷码等。数字值可以在这些其他数字系统中,如八进制数而不是二进制数。数值可以取补或取反。位数可以调整。可以用各种类型的计数器来代替,如波纹计数器或同步计数器。

[0120]

发明背景部分可以包含关于本发明的问题或环境的背景资料,而不是描述他人的现有技术。因此,在背景部分包含材料并不是申请人对现有技术的承认。

[0121]

本文描述的任何方法或过程都是机器实现或计算机实现的,意在由机器、计算机或其他装置执行,而不是在没有机器协助的情况下仅由人类执行。产生的有形结果可以包括报告或显示装置(例如计算机显示器、投影装置、音频产生装置和相关媒体装置等)上其他机器生成的显示,并且可以包括也是由机器产生的硬拷贝打印输出。其他机器的计算机控制是另一种有形结果。

[0122]

所描述的任何优点和好处可能并不适用于本发明的所有实施例。当在权利要求要素中使用"手段(means)"单词时,申请人希望该权利要求要素属于35usc第112条第6段。通常情况下,在"手段(means)"一词之前通常有一个或多个词的标签。在"手段(means)"之前

的一个或多个词的目的是为了方便引用权利要求要素,而不是为了传达结构上的限制。这样的手段加功能的权利要求不仅意在涵盖本文所描述的用于执行功能的结构及其结构等同物,而且还包括等同结构。例如,虽然钉子和螺钉具有不同的结构,但它们是等同结构,因为它们都执行紧固功能。不使用"手段(means)"一词的权利要求不属于35usc第112条第6款的规定。信号通常是电子信号,但也可以是光信号,例如可以通过光纤线路传输的光信号。

[0123]

出于说明和描述的目的,以上已经给出了本发明实施例的描述。其并不旨在穷举或将本发明限制为所公开的精确形式。鉴于上述教导,许多修改和变化是可能的。本发明的范围不受该详细描述的限制,而是受所附权利要求书的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1