部分脉冲电位能调的栅极驱动电路及装置的制作方法

1.本发明涉及一种驱动电路及装置,特别是涉及一种应用于元件特性测试的部分脉冲电位能调的栅极驱动电路及装置。

背景技术:

2.第三代半导体材料是基于宽带隙复合材料(wide bandgap compound material),以碳化硅(sic)以及氮化镓(gan)为代表,由于其卓越的材料性能、高载子迁移率(carrier mobility)和高带隙(band-gap),例如,gan元件的fom比si元件高5到10倍,这使它们具有在高电压和高功率应用中替代si元件的巨大潜力,而能应用在更高阶的高压功率元件以及高频通讯元件领域。

3.尽管gan元件已经通过了基于si元件的jedec可靠性标准,但仍需要花费时间来建立系统现场测试的信心,并证明gan元件在应用中的稳固性。由于第三代半导体材料的元件从静态(static condition)到动态(dynamic conditions)的表现不同,目前,关于gan元件的系统级可靠性(system-level reliability)的各种测试设备及方法,仍是业界主要发展目标。

技术实现要素:

4.本发明的目的在于提供一种能供第三代半导体材料的元件作为通用测试装置的部分脉冲电位能调的栅极驱动电路。

5.本发明的部分脉冲电位能调的栅极驱动电路,适用于接收第一驱动信号及第二驱动信号,并输出相应的栅极驱动信号,包含低电位端、第一驱动模块、第二驱动模块、第一驱动输入端、第二驱动输入端、驱动输出端,及单向模块。

6.所述第一驱动模块与所述第二驱动模块,各自包括输入端、输出端、输入电容、输入电阻、第一二极管,及可调电源。所述输入电容与所述输入电阻两者并联,且其中一端电连接所述输入端,另一端电连接所述输出端。所述第一二极管及所述可调电源两者串联于所述输出端及所述低电位端间。

7.所述第一驱动输入端及所述第二驱动输入端,分别用于接收所述第一驱动信号与所述第二驱动信号,且分别电连接所述第一驱动模块的所述输入端与所述第二驱动模块的所述输入端。

8.所述驱动输出端电连接所述第一驱动模块的所述输出端与所述第二驱动模块的所述输出端,并用于输出所述栅极驱动信号。

9.所述单向模块电连接于所述第二驱动模块的所述输出端与所述驱动输出端间,用于供所述第二驱动模块输出的正向信号单向通过。

10.本发明的部分脉冲电位能调的栅极驱动电路,所述第一驱动模块还包括第二二极管,所述第二二极管的阳极端电连接所述低电位端,其阴极端电连接所述输出端。

11.本发明的部分脉冲电位能调的栅极驱动电路,所述单向模块包括单向二极管,所

述单向二极管的阳极端电连接所述第二驱动模块的所述输出端,所述单向二极管的阴极端电连接所述驱动输出端。

12.本发明的部分脉冲电位能调的栅极驱动电路,所述单向模块还包括并联所述单向二极管的单向电容、串联所述单向二极管的调整电阻,及两端分别电连接所述单向二极管的阳极端与所述调整电阻远离所述单向二极管的一端的单向电阻。

13.本发明的部分脉冲电位能调的栅极驱动电路,于所述第一驱动模块与所述第二驱动模块中,所述第一二极管的阳极端电连接所述输出端,所述第一二极管的阴极端电连接所述可调电源的正端,所述可调电源的负端电连接所述低电位端。

14.本发明的部分脉冲电位能调的栅极驱动电路,所述第一驱动模块与所述第二驱动模块各自还包括两端分别电连接于所述可调电源的正端与所述低电位端的限流电阻。

15.本发明的部分脉冲电位能调的栅极驱动电路,所述第一驱动模块与所述第二驱动模块各自还包括两端分别电连接于所述可调电源的正端与所述低电位端的稳压电容。

16.本发明的目的在于提供一种能供第三代半导体材料的元件作为通用测试装置的部分脉冲电位能调的栅极驱动装置。

17.本发明的部分脉冲电位能调的栅极驱动装置,适用于接收第一控制信号及第二控制信号,并对应所述第一控制信号与所述第二控制信号驱动待测件的栅极,包含高电位端、低电位端、第一控制输入端、第二控制输入端、栅极驱动端、第一驱动器、第二驱动器,及如上述的栅极驱动电路。

18.所述第一控制输入端及所述第二控制输入端分别用于接收所述第一控制信号与所述第二控制信号。

19.所述栅极驱动端适用于输出对应所述第一控制信号与所述第二控制信号的栅极驱动信号至所述待测件的栅极。

20.所述第一驱动器电连接所述高电位端、所述低电位端与所述第一控制输入端,由所述第一控制输入端接收所述第一控制信号并输出相应的第一驱动信号。

21.所述第二驱动器电连接所述高电位端、所述低电位端与所述第二控制输入端,由所述第二控制输入端接收所述第二控制信号并输出相应的第二驱动信号。

22.所述栅极驱动电路的所述第一驱动输入端与所述第二驱动输入端分别电连接所述第一驱动器与所述第二驱动器,所述栅极驱动电路的所述驱动输出端与所述低电位端分别电连接所述栅极驱动端与上述的所述低电位端。

23.本发明的部分脉冲电位能调的栅极驱动装置,还包含两端分别电连接于所述栅极驱动端与所述待测件的栅极的调速电阻。

24.本发明的有益效果在于:通过上述电路设置,可以仅动态调整所述栅极驱动信号中的部分信号(例如,仅动态调整所述第一控制信号的对应部分,或仅动态调整所述第二控制信号的对应部分),如此,能适用于供第三代半导体材料的元件作为通用测试装置。

附图说明

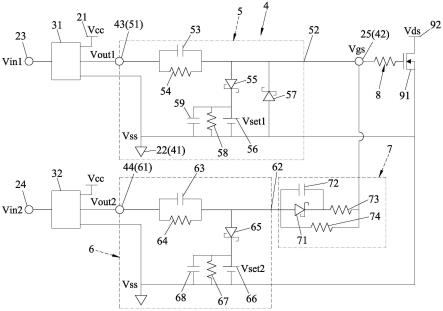

25.图1是本发明部分脉冲电位能调的栅极驱动装置的实施例的电路图;及

26.图2是所述实施例中,第一控制信号、第二控制信号、第一驱动信号、第二驱动信号及栅极驱动信号的波形示意图。

具体实施方式

27.参阅图1与图2,本发明部分脉冲电位能调的栅极驱动装置的实施例,适用于接收由一个控制电路(图未示)输出的一个第一控制信号vin1及一个第二控制信号vin2,并输出一个对应所述第一控制信号vin1与所述第二控制信号vin2的栅极驱动信号vgs至一个待测件91的栅极以控制驱动所述待测件91。所述待测件91是电连接于一个待测电源端92与一个低电位端22间,所述待测电源端92提供一个待测电压vds。其中,本发明适用于应用于测试第三代半导体材料的功率元件,或应用于其他需要动态调整部分脉冲电位的测试作业。

28.其中,所述第一控制信号vin1为部分脉波经屏蔽的主要脉波(pulse)信号,所述第二控制信号vin2则是将所述第一控制信号vin1的脉波屏蔽的部分脉波信号,即,所述第一控制信号vin1与所述第二控制信号vin2能组合为完整连续的脉波信号。例如,当应用于正常开关操作(normal switching operation)下提取动态阈值电压(dynamic threshold voltage,缩写为dynamic vth)的测试时,所述第一控制信号vin1较佳是配合使用屏蔽1%(或更低的比例)的脉波的脉波信号,而所述第二控制信号vin2则搭配为补偿所述1%的脉波的脉波信号(即,屏蔽其余99%的脉波的脉波信号),如此,以使测试状态接近实际使用的状况。

29.所述栅极驱动装置的所述实施例包含一个高电位端21、所述低电位端22、一个第一控制输入端23、一个第二控制输入端24、一个栅极驱动端25、一个第一驱动器31、一个第二驱动器32,及一个栅极驱动电路4。

30.所述高电位端21提供一个高电压vcc,所述低电位端22提供一个低电压vss,于本实施例中,所述低电压vss以接地电压(gnd,0v)说明。

31.所述第一控制输入端23及所述第二控制输入端24分别用于接收所述第一控制信号vin1与所述第二控制信号vin2。

32.所述栅极驱动端25适用于输出对应所述第一控制信号vin1与所述第二控制信号vin2的所述栅极驱动信号vgs至所述待测件91的栅极(gate)。

33.所述第一驱动器31电连接所述高电位端21、所述低电位端22与所述第一控制输入端23,由所述第一控制输入端23接收所述第一控制信号vin1并输出一个相应的第一驱动信号vout1。所述第二驱动器32电连接所述高电位端21、所述低电位端22与所述第二控制输入端24,由所述第二控制输入端24接收所述第二控制信号vin2并输出一个相应的第二驱动信号vout2。所述第一驱动器31与所述第二驱动器32能使用栅极驱动器(gate driver)实施,用于分别将所述第一控制信号vin1与所述第二控制信号vin2的驱动能力放大,以输出为相位分别对应于所述第一控制信号vin1与所述第二控制信号vin2的所述第一驱动信号vout1与所述第二驱动信号vout2。

34.所述栅极驱动电路4适用于接收所述第一驱动信号vout1及所述第二驱动信号vout2,并输出相对应的所述栅极驱动信号vgs,并包括一个低电位端41、一个驱动输出端42、一个第一驱动输入端43、一个第二驱动输入端44、一个第一驱动模块5、一个第二驱动模块6,及一个单向模块7。

35.所述低电位端41电连接于上述的所述低电位端22,同样是以接地电压(gnd,0v)说明。所述驱动输出端42电连接于所述栅极驱动端25,用于输出所述栅极驱动信号vgs。

36.所述第一驱动输入端43与所述第二驱动输入端44分别电连接所述第一驱动器31

与所述第二驱动器32,并分别用于接收所述第一驱动信号vout1与所述第二驱动信号vout2。

37.所述第一驱动模块5具有一个输入端51、一个输出端52、一个输入电容53、一个输入电阻54、一个第一二极管55、一个可调电源56及一个第二二极管57。

38.所述输入端51电连接所述第一驱动输入端43,用于接收所述第一驱动信号vout1。所述输出端52电连接所述驱动输出端42。

39.所述输入电容53与所述输入电阻54并联,其中一端电连接所述输入端51以接收所述第一驱动信号vout1,另一端电连接所述输出端52。其中,所述输入电容53用于提供暂态(transient)信号路径,所述输入电阻54用于提供静态(static)信号路径。

40.所述第一二极管55及所述可调电源56串联于所述输出端52及所述低电位端22间,且所述第一二极管55的阳极端电连接所述输出端52。所述第一二极管55较佳是使用萧特基二极管(schottky diode)实施,以获得较快的切换速度及较低的导通电压。

41.所述可调电源56的正端电连接所述第一二极管55的阴极端,所述可调电源56的负端电连接所述低电位端22。所述可调电源56能使用一个电源供应器(power supply)实施,用于提供一个能调整电压值的第一可调电压vset1。

42.所述第二二极管57的阳极端电连接所述低电位端22,其阴极端电连接所述输出端52,所述第二二极管57的作用在于将所述驱动输出端42的低电位电压限制于接近所述低电压vss。所述第二二极管57同样较佳是使用萧特基二极管实施,以获得较快的切换速度及较低的导通电压。

43.所述第一驱动模块5较佳是还包括一个限流电阻58及一个稳压电容59。

44.所述限流电阻58两端分别电连接于所述可调电源56的正端与所述低电位端22,用于提供所述第一二极管55与所述可调电源56的电流的分流路径,其电阻值大小会限制所述第一二极管55能流经的最大电流。

45.所述稳压电容59两端分别电连接于所述可调电源56的正端与所述低电位端22,用于提供稳压效果。

46.所述第二驱动模块6具有一个输入端61、一个输出端62、一个输入电容63、一个输入电阻64、一个第一二极管65,及一个可调电源66。

47.所述输入端61电连接所述第二驱动输入端44,用于接收所述第二驱动信号vout2。所述输出端62经所述单向模块7电连接所述驱动输出端42。

48.所述输入电容63与所述输入电阻64并联,其中一端电连接所述输入端61以接收所述第二驱动信号vout2,另一端电连接所述输出端62。其中,所述输入电容63用于提供暂态(transient)信号路径,所述输入电阻64用于提供静态(static)信号路径。

49.所述第一二极管65及所述可调电源66串联于所述输出端62及所述低电位端22间,且所述第一二极管65的阳极端电连接所述输出端62。所述第一二极管65较佳是使用萧特基二极管实施,以获得较快的切换速度及较低的导通电压。

50.所述可调电源66的正端电连接所述第一二极管65的阴极端,所述可调电源66的负端电连接所述低电位端22。所述可调电源66能使用一个电源供应器实施,用于提供一个能调整电压值的第二可调电压vset2。

51.所述第二驱动模块6较佳是还包括一个限流电阻67及一个稳压电容68。

52.所述限流电阻67两端分别电连接于所述可调电源66的正端与所述低电位端22,用于提供所述第一二极管65与所述可调电源66的电流的分流路径,其电阻值大小会限制所述第一二极管65能流经的最大电流。

53.所述稳压电容68两端分别电连接于所述可调电源66的正端与所述低电位端22,用于提供稳压效果。

54.所述单向模块7电连接于所述第二驱动模块6的所述输出端62与所述驱动输出端42间,用于供所述第二驱动模块6输出的正向信号单向通过。

55.所述单向模块7包括一个单向二极管71、一个并联所述单向二极管71的单向电容72、一个串联所述单向二极管71的调整电阻73,及一个两端分别电连接所述单向二极管71的阳极端与所述调整电阻73远离所述单向二极管71的一端的单向电阻74。所述单向二极管71的阳极端电连接所述第二驱动模块6的所述输出端62,所述单向二极管71的阴极端电连接所述驱动输出端42。所述单向二极管71较佳是使用萧特基二极管实施,以获得较快的切换速度及较低的导通电压。

56.所述实施例较佳是还包括一个调速电阻8。所述调速电阻8两端分别电连接于所述栅极驱动端25与所述待测件91的栅极,其电阻值的大小用于调整所述待测件91的切换(switching)速度,即,用于调整所述待测件91的压摆率(slew rate)。

57.于实际应用时,将相互配合的所述第一控制信号vin1与所述第二控制信号vin2分别输入所述第一驱动器31与所述第二驱动器32,并经所述第一驱动器31与所述第二驱动器32分别输出为相位对应于所述第一控制信号vin1与所述第二控制信号vin2的所述第一驱动信号vout1与所述第二驱动信号vout2,所述第一驱动信号vout1与所述第二驱动信号vout2的最高电压是固定趋近于所述高电位端21的电压vcc,而最低电压是固定趋近于所述低电位端22的电压vss。其中,电压值的大小排序为vcc》vset1》vset2》vss,所述待测电压vds的值则是相关于所述待测件91的参数,与上述排序不相关。

58.接着,所述第一驱动信号vout1经所述第一驱动模块5传递至所述栅极驱动端25,并与经所述第二驱动模块6传递至所述栅极驱动端25的所述第二驱动信号vout2组合而成所述栅极驱动信号vgs。

59.当所述第一驱动信号vout1为高电位,所述第二驱动信号vout2为低电位时,此时于所述第一驱动模块5中,所述第一二极管55导通,所述栅极驱动信号vgs的电压为所述可调电源56所提供的所述第一可调电压vset1加上所述第一二极管55的导通电压,以萧特基二极管为例,其导通电压约为0.3v左右,因此,其电压为vset1+0.3v。此时流经所述第一二极管55的电流与所述可调电源56所提供的电流皆会经由所述限流电阻58流至所述低电位端22。同时,在所述第二驱动模块6中,由于所述第二驱动信号vout2为低电位,所述第一二极管65不导通,所述输出端62的电压会低于所述栅极驱动端25的电压值(vset1+0.3v),因此不会通过所述单向模块7而影响所述栅极驱动信号vgs的电压。并且,此时所述栅极驱动端25的高电压(vset1+0.3v)也会受所述单向模块7阻挡,而不会传入所述第二驱动模块6。

60.当所述第二驱动信号vout2为高电位,所述第一驱动信号vout1为低电位时,此时所述第二驱动模块6中,所述第一二极管65导通,所述输出端62的电压为所述可调电源66所提供的所述第二可调电压vset2加上所述第一二极管65的导通电压,以萧特基二极管为例,其导通电压约为0.3v左右,因此,其电压为vset2+0.3v,接着,此电压通过所述单向模块7传

递至所述栅极驱动端25,所以须再扣掉所述单向二极管71的导通电压,同样以萧特基二极管为例,所述栅极驱动信号vgs的电压即为vset2+0.3v-0.3v=vset2。此时流经所述第一二极管65的电流与所述可调电源66所提供的电流皆会经由所述限流电阻67流至所述低电位端22。同时,在所述第一驱动模块5中,由于所述栅极驱动信号vgs的电压vset2低于vset1+0.3v且大于所述低电压vss,因此,所述第一二极管55不导通,所述第二二极管57不导通,所以不会影响所述栅极驱动信号vgs的电压。

61.当所述第一驱动信号vout1与所述第二驱动信号vout2皆为低电位时,此时于所述第一驱动模块5中,所述第一二极管55不导通,所述第二二极管57导通,所述栅极驱动信号vgs的电压会受所述第二二极管57箝制而为所述低电压vss减去所述第二二极管57的导通电压,以萧特基二极管为例,其电压约为vss-0.3v。此时,于所述第二驱动模块6中,所述第一二极管65不导通,所述输出端62的电压会接近所述低电压vss,减去所述单向二极管71的跨压(0.3v),传递至所述栅极驱动端25时也为vss-0.3v。

62.借此,可以将所述第一控制信号vin1与所述第二控制信号vin2的脉波进行类似于或栅(or gate)的整合,并且,可以通过分别调整所述第一可调电压vset1与所述第二可调电压vset2的大小,以分别动态调整所述栅极驱动信号vgs中,所述第一控制信号vin1与所述第二控制信号vin2所对应的脉波的峰值,以供驱动所述待测件91切换导通状态而进行动态表现测试。

63.借此,在测试应用时,可以例如仅动态调整所述第二控制信号vin2所对应的脉波的峰值,即,可以仅调整所述栅极驱动信号vgs中仅1%(或更低的比率)的脉波的电压值,如此,能提供第三代半导体材料的元件于实际系统(real system)或特性测试电路(characterization test circuit)中进行部分脉冲电位的调整。

64.综上所述,本发明部分脉冲电位能调的栅极驱动装置,确实能达成本发明的目的。

65.以上所述者,仅为本发明的实施例而已,当不能以此限定本发明实施的范围,即凡依本发明权利要求书及说明书内容所作的简单的等效变化与修饰,皆仍属本发明的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1