一种高速接口发射机电路、芯片和电子设备

1.本发明涉及集成电路技术领域,尤其涉及一种高速接口发射机电路、芯片和电子设备。

背景技术:

2.云计算服务、物联网应用和人工智能技术的快速发展带动了网络传输容量的飞速增长,互联数据的瞬间交换速度可以达到tbit/s。通信数据率的不断攀升为高速互连技术带来了巨大挑战,数据传输速度成为限制系统性能的关键因素。高速串行接口技术凭借高带宽、低延迟和良好的可扩展性等特性成为了高速数据传输的有效解决方案,并广泛应用于处理器与外设互连、多芯片间互连、高速硬盘接口、串行网络接口、光纤通信等领域。高速串行接口相关技术涉及半定制、全定制以及模拟电路等多种设计方法,是一个数模混合系统,其处理的信号速率通常高达几十至百gbps以上。

3.高速接口发射机芯片的关键性能指标包括传输速率、数据抖动、信号幅度、均衡能力、系统功耗等。传输速率是系统的核心指标,也是发射机芯片的设计难点。随着通信速率提升,高速接口发射机芯片的设计面临一系列信号完整性问题,如码间干扰、串扰、噪声、信道反射等。

4.采用均衡技术可以针对性地解决上述串行数据传输中的信号衰减问题。但是,通信频率地提升对高速接口发射机芯片的设计也产生巨大挑战,例如芯片内部信号抖动严重,导致串行数据眼开减小,严重恶化系统性能。

技术实现要素:

5.有鉴于此,本发明提供一种高速接口发射机电路、芯片和电子设备,以解决现有技术中高速接口发射机芯片内部信号抖动严重,导致的串行数据眼开减小,进而严重恶化系统性能的问题。

6.为实现上述目的,本发明提供如下技术方案:

7.一种高速接口发射机电路,包括:

8.至少一组数据串化电路、至少一组均衡驱动电路、一个时钟生成与匹配电路和两个负载电阻;

9.每组所述数据串化电路包括形成差分信号的正数据串化电路和负数据串化电路;每组所述均衡驱动电路包括正均衡驱动电路和负驱动电路;所述正数据串化电路的输出端与所述正均衡驱动电路的输入端相连;所述负数据串化电路的输出端与所述负均衡驱动电路的输入端相连;

10.所述均衡驱动电路的输出端均与两个负载电阻的一端相连,作为所述高速接口发射机电路的输出端;两个负载电阻的另一端均与电源相连;

11.所述正数据串化电路和所述负数据串化电路均与所述时钟生成与匹配电路相连,所述时钟生成与匹配电路产生时钟信号,传递至所述数据串化电路的正数据串化电路和负

数据串化电路;

12.其中,所述时钟生成与匹配电路产生的时钟信号用于与所述数据串化电路中的串化数据进行时钟匹配。

13.优选地,所述时钟生成与匹配电路包括:第一缓冲器、多相时钟信号生成器、时钟延时器、偏置信号生成器;

14.其中,所述第一缓冲器的输入端用于接收时钟输入信号,用于对所述时钟输入信号进行延迟;

15.所述第一缓冲器的输出端与所述多相时钟信号生成器的输入端相连;所述多相时钟信号生成器用于根据预设的采样时钟间的相位差产生多相位时钟;

16.所述多相时钟信号生成器的输出端与所述正数据串化电路和所述负数据串化电路中的同步电路相连;

17.所述多相时钟信号生成器的输出端还用于与所述时钟延时器相连;

18.所述时钟延时器与所述偏置信号生成器相连,接收偏置信号控制,并输入延时时钟信号至所述正数据串化电路和所述负数据串化电路的选择器中。

19.优选地,所述时钟延时器包括:

20.第二缓冲器、第三缓冲器、第四缓冲器、第五缓冲器、第六缓冲器、第七缓冲器、第八缓冲器、第九缓冲器、第十缓冲器、第十一缓冲器和第一可变电容、第二可变电容、第三可变电容、第四可变电容;

21.所述第二缓冲器、所述第三缓冲器和所述第四缓冲器依次串联;所述第二缓冲器的输入端接收第一时钟输入信号;所述第二缓冲器的输出端与所述第一可变电容的一端相连;所述第三缓冲器的输出端与所述第二可变电容的一端相连;所述第一可变电容的另一端和所述第二可变电容的另一端均接地;所述第四缓冲器的输出端输出第一时钟信号;

22.所述第五缓冲器和所述第六缓冲器依次串联;所述第五缓冲器的输入端接收第二时钟输入信号,所述第六缓冲器的输出端输出第二时钟信号;

23.所述第七缓冲器、所述第八缓冲器和所述第九缓冲器依次串联;所述第七缓冲器的输入端接收第三时钟输入信号;所述第七缓冲器的输出端与所述第三可变电容的一端相连;所述第八缓冲器的输出端与所述第四可变电容的一端相连;所述第三可变电容的另一端和所述第四可变电容的另一端均接地;所述第九缓冲器的输出端输出第三时钟信号;

24.所述第十缓冲器和所述第十一缓冲器依次串联;所述第十缓冲器的输入端接收第四时钟输入信号,所述第十一缓冲器的输出端输出第四时钟信号。

25.优选地,所述正数据串化电路和所述负数据串化电路结构相同,均包括:

26.依次相连的随机数据生成器、同步电路和选择器;

27.所述随机数据生成器生成并行数据,经过所述同步电路进行数据同步和采样,通过所述选择器将所述并行数据根据采样时钟采样生成多个串行数据。

28.优选地,所述数据串化电路还包括逻辑均衡电路;所述逻辑均衡电路连接在所述选择器和所述均衡驱动电路之间;

29.所述逻辑均衡电路包括并联的多个逻辑均衡单元;

30.每个所述逻辑均衡单元均包括:选择开关、反相器和逻辑门电路;

31.其中,所述选择开关与所述反相器的输入端相连;

32.所述反相器的输出端与所述逻辑门电路相连;

33.所述逻辑门电路用于接收前级串行差分数据和后级串行差分数据,并输出主级串行差分数据。

34.优选地,所述逻辑门电路包括:第一与非门、第一或非门、第二与非门和第二或非门,以及多个晶体管;

35.所述第一与非门和所述第二与非门的第一端均与所述反相器的输出端相连;

36.所述第一与非门的第二端与所述第一或非门的第一端均用于接收所述前级串行差分数据;

37.所述第二与非门的第二端与所述第二或非门的第一端均用于接收所述后级串行差分数据;

38.所述第一或非门和所述第二或非门的第二端均与所述反相器的输入端相连;

39.多个晶体管包括第一晶体管、第二晶体管、第三晶体管和第四晶体管;

40.所述第一晶体管的控制端与所述第一与非门的输出端相连;所述第二晶体管的控制端与所述第一或非门的输出端相连;所述第一晶体管的第一端与电源相连;所述第一晶体管的第二端与所述第二晶体管的第一端相连,且用于输出所述主级串行差分数据;所述第二晶体管的第二端接地;

41.所述第三晶体管的控制端与所述第二与非门的输出端相连;所述第四晶体管的控制端与所述第二或非门的输出端相连;所述第三晶体管的第一端与电源相连;所述第三晶体管的第二端与所述第四晶体管的第一端相连,且用于输出所述主级串行差分数据;所述第四晶体管的第二端接地。

42.优选地,所述正均衡驱动电路与所述负均衡驱动电路接收的差分信号相反,所述正均衡驱动电路具体包括:

43.前级均衡控制电路、后级均衡控制电路、主级均衡控制电路和第一电容、第二电容;

44.所述前级均衡控制电路包括第五晶体管、第六晶体管、第七晶体管和第八晶体管;

45.所述主级均衡控制电路包括第九晶体管、第十晶体管、第十一晶体管和第十二晶体管;

46.所述后级均衡控制电路包括第十三晶体管、第十四晶体管、第十五晶体管和第十六晶体管;

47.所述第五晶体管和所述第六晶体管的控制端均接收前级偏置电压输入;所述第五晶体管的第一端用于与所述第九晶体管和所述第十三晶体管的第一端相连,并用于与第一负载电阻的一端相连;

48.所述第六晶体管的第一端用于与所述十晶体管和所述第十四晶体管的第一端相连,并用于与第二负载电阻的一端相连;

49.所述第五晶体管的第二端与所述第七晶体管的第一端相连,所述第七晶体管的控制端用于接收前级串行差分数据的负差分数据;

50.所述第六晶体管的第二端与所述第八晶体管的第一端相连,所述第八晶体管的控制端用于接收前级串行差分数据的正差分数据;

51.所述第九晶体管和所述第十晶体管的控制端均接收主级偏置电压输入;所述第九

晶体管的第二端与所述第十一晶体管的第一端相连,所述第十一晶体管的控制端用于接收主级串行差分数据的正差分数据;

52.所述第十晶体管的第二端与所述第十二晶体管的第一端相连,所述第十二晶体管的控制端用于接收主级串行差分数据的负差分数据;

53.所述第十三晶体管和所述第十四晶体管的控制端均接收后级偏置电压输入;所述第十三晶体管的第二端与所述第十五晶体管的第一端相连,所述第十五晶体管的控制端用于接收后级串行差分数据的负差分数据;

54.所述第十四晶体管的第二端与所述第十六晶体管的第一端相连,所述第十六晶体管的控制端用于接收后级串行差分数据的正差分数据;

55.所述第七晶体管的第二端、所述第八晶体管、所述第十一晶体管、所述第十二晶体管、所述第十五晶体管和所述第十六晶体管的第二端均接地;

56.所述第一电容的一端与所述第十晶体管的第二端相连,所述第一电容的另一端与所述第十一晶体管的控制端相连;

57.所述第二电容的一端与所述第九晶体管的第二端相连,所述第二电容的另一端与所述第十二晶体管的控制端相连。

58.优选地,所述数据串化电路包括并联的两组,所述均衡驱动电路的个数也是两组。

59.本发明还提供一种高速接口发射机芯片,包括上面任意一项所述的高速接口发射机电路。

60.本发明还提供一种电子设备,包括上面所述的高速接口发射机芯片。

61.经由上述的技术方案可知,本发明提供的高速接口发射机电路,包括:至少一组数据串化电路、至少一组均衡驱动电路、一个时钟生成与匹配电路和两个负载电阻;所述时钟生成与匹配电路与数据串化电路相连,时钟生成与匹配电路产生的时钟信号用于与数据串化电路中的串化数据进行时钟匹配,使得时钟信号与数据串化电路中的串行数据精确匹配,进而大大改善数据性能,降低了串化电路的输出的抖动,从而增大了眼开,改善系统性能。

附图说明

62.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

63.图1为不同时序匹配下串化电路输出信号眼开对比图;

64.图2为为本发明提供一种高速接口发射机电路结构示意图;

65.图3为本发明实施例提供的一种高速接口发射机电路的具体结构示意图;

66.图4为本发明实施例提供的一种时钟延时器结构示意图;

67.图5为本发明实施例提供的选择器结构示意图;

68.图6为本发明实施例给出的数据频域特性对比图;

69.图7为本发明实施例提供的另一种高速接口发射机电路结构示意图;

70.图8为本发明实施例提供的逻辑均衡电路结构示意图;

71.图9为本发明实施例提供的一种高速接口发射机电路结构示意图;

72.图10为本发明实施例提供的正均衡驱动电路的结构示意图;

73.图11为本发明实施例提供的另一种高速接口发射机电路结构示意图;

74.图12为本发明实施例提供的电子设备的结构示意图。

具体实施方式

75.正如背景技术部分所述,现有技术中高速接口发射机芯片内部信号抖动严重,导致串行数据眼开减小,从而严重恶化系统性能。

76.发明人发现,出现上述现象的原因是,如图1所示,图1为不同时序匹配下数据串化电路输出信号眼开对比图;通过图中可以看出,最优的时钟位置应当位于数据中心(上面的时钟信号时序图),此时数据串化电路输出的数据抖动最小,如果时钟信号的边沿偏离数据中心(下面的时钟信号时序图),在选通输出信号时会引入额外抖动,且该抖动不可通过芯片外电路进行抵消,抖动的增大会导致数据眼开的减小,严重恶化系统性能。

77.基于此,本发明提供一种高速接口发射机电路,包括:

78.至少一组数据串化电路、至少一组均衡驱动电路、一个时钟生成与匹配电路和两个负载电阻;

79.每组所述数据串化电路包括形成差分信号的正数据串化电路和负数据串化电路;每组所述均衡驱动电路包括正均衡驱动电路和负驱动电路;所述正数据串化电路的输出端与所述正均衡驱动电路的输入端相连;所述负数据串化电路的输出端与所述负均衡驱动电路的输入端相连;

80.所述均衡驱动电路的输出端均与两个负载电阻的一端相连,作为所述高速接口发射机电路的输出端;两个负载电阻的另一端均与电源相连;

81.所述正数据串化电路和所述负数据串化电路均与所述时钟生成与匹配电路相连,所述时钟生成与匹配电路产生时钟信号,传递至所述数据串化电路的正数据串化电路和负数据串化电路;

82.其中,所述时钟生成与匹配电路产生的时钟信号用于与所述数据串化电路中的串化数据进行时钟匹配。

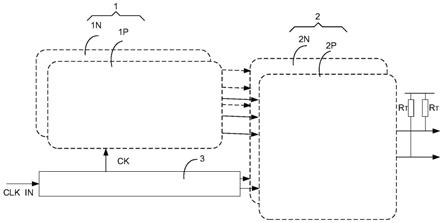

83.本发明提供的高速接口发射机电路,包括:至少一组数据串化电路、至少一组均衡驱动电路、一个时钟生成与匹配电路和两个负载电阻;所述时钟生成与匹配电路与数据串化电路相连,时钟生成与匹配电路产生的时钟信号用于与数据串化电路中的串化数据进行时钟匹配,使得时钟信号与数据串化电路中的串行数据精确匹配,进而大大改善数据性能,降低了串化电路的输出的抖动,从而增大了眼开,改善系统性能。

84.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

85.需要说明的是,当元件被称为“固定于”或“设置于”另一个元件,它可以直接在另一个元件上或者间接在该另一个元件上。当一个元件被称为是“连接于”另一个元件,它可以是直接连接到另一个元件或间接连接至该另一个元件上。

86.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。“若干”的含义是一个或一个以上,除非另有明确具体的限定。

87.在本发明的描述中,需要理解的是,术语“上”、“下”、“前”、“后”、“左”、“右”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

88.在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

89.请参见图2,图2为本发明提供一种高速接口发射机电路结构示意图,所述高速接口发射机电路包括:至少一组数据串化电路1、至少一组均衡驱动电路2、一个时钟生成与匹配电路3和两个负载电阻r

t

;每组数据串化电路1包括形成差分信号的正数据串化电路1p和负数据串化电路1n;每组均衡驱动电路2包括正均衡驱动电路2p和负驱动电路2n;正数据串化电路1p的输出端与正均衡驱动电路2p的输入端相连;负数据串化电路1n的输出端与负均衡驱动电路2n的输入端相连。

90.均衡驱动电路2的输出端均与两个负载电阻r

t

的一端相连,作为高速接口发射机电路的输出端dout;两个负载电阻r

t

的另一端均与电源vdd相连。正数据串化电路1p和负数据串化电路1n均与时钟生成与匹配电路3相连,时钟生成与匹配电路3产生时钟信号,传递至数据串化电路1的正数据串化电路1p和负数据串化电路1n。其中,时钟生成与匹配电路3产生的时钟信号ck用于与数据串化电路1中的串化数据进行时钟匹配。

91.需要说明的是,本发明实施例中不限定时钟生成与匹配电路3的具体结构,只要能够实现与串化数据进行精确匹配的功能,使得串化数据的抖动减小,增大眼开即可,具体的,如图3所示,图3为本发明实施例提供的一种高速接口发射机电路的具体结构示意图。其中,时钟生成与匹配电路3包括:第一缓冲器31、多相时钟信号生成器32、时钟延时器33、偏置信号生成器34。

92.其中,第一缓冲器31的输入端用于接收时钟输入信号clkin,用于对时钟输入信号进行延迟;第一缓冲器31的输出端与多相时钟信号生成器32的输入端相连;多相时钟信号生成器32用于根据预设的采样时钟间的相位差产生多相位时钟ck;多相时钟信号生成器32的输出端与正数据串化电路1p和负数据串化电路1n中的同步电路12相连;多相时钟信号生成器32的输出端还用于与时钟延时器33相连;时钟延时器33与偏置信号生成器34相连,接收偏置信号v

ctrl

控制,并输入延时时钟信号至正数据串化电路1p和负数据串化电路1n的选择器13中。

93.本发明实施例中通过多相时钟信号生成器32生成时钟信号ck,此时的时钟信号ck能够与串化数据中的同步电路12中的数据进行同步,然后与选择器13中的串化数据的传输进行精确匹配,从而使得数据传输过程中抖动减小,进而增大眼开,提升系统性能。

94.请参见图4,图4为本发明实施例提供的一种时钟延时器结构示意图;本实施例中实现时钟信号与串化数据精确匹配的时钟延时器33的具体结构包括:

95.第二缓冲器331、第三缓冲器332、第四缓冲器333、第五缓冲器334、第六缓冲器335、第七缓冲器336、第八缓冲器337、第九缓冲器338、第十缓冲器339、第十一缓冲器3310和第一可变电容c331、第二可变电容c332、第三可变电容c333、第四可变电容c334;

96.第二缓冲器331、第三缓冲器332和第四缓冲器333依次串联;第二缓冲器331的输入端接收第一时钟输入信号ck

in0

;第二缓冲器331的输出端与第一可变电容c331的一端相连;第三缓冲器332的输出端与第二可变电容c332的一端相连;第一可变电容c331的另一端和第二可变电容c332的另一端均接地;第四缓冲器333的输出端输出第一时钟信号ck0;

97.第五缓冲器334和第六缓冲器335依次串联;第五缓冲器334的输入端接收第二时钟输入信号ck

in90

,第六缓冲器335的输出端输出第二时钟信号ck

90

;

98.第七缓冲器336、第八缓冲器337和第九缓冲器338依次串联;第七缓冲器336的输入端接收第三时钟输入信号ck

in180

;第七缓冲器336的输出端与第三可变电容c333的一端相连;第八缓冲器337的输出端与第四可变电容c334的一端相连;第三可变电容c333的另一端和第四可变电容c334的另一端均接地;第九缓冲器338的输出端输出第三时钟信号ck

180

;

99.第十缓冲器339和第十一缓冲器3310依次串联;第十缓冲器339的输入端接收第四时钟输入信号ck

in270

,第十一缓冲器3310的输出端输出第四时钟信号ck

270

。

100.本实施例中,通过在时钟通路上,通过在不同时钟信号延时过程中,增加缓冲器和可变电容,使得多个时钟信号的延时不同,从而够通过调节缓冲器的大小以及可变电容的容值,来匹配串化电路中的传输的串化数据,从而实现时钟与数据的精准匹配,极大改善数据性能,显著降低串化电路的输出抖动。

101.与上面时钟信号延时过程中进行匹配的串化电路如图3所示,所述数据串化电路包括:依次相连的随机数据生成器11、同步电路12和选择器13;其中,随机数据生成器11生成并行数据,经过同步电路12进行数据同步和采样,然后再通过选择器13将并行数据根据采样时钟采样生成多个串行数据。串行数据包括主级串行数据。其中,随机数据生成器11和同步电路12可以采用现有公知结构进行实现,本实施例中对此不作限定。

102.在实际应用中,以发射机电路传输四电平脉冲幅度调制信号为例。如图3所示,传输数据称为主级数据dm

main

,主级数据dm

main

经过同步电路后,根据主级数据dm

main

生成与主级数据具有正负时间差的前级数据dm

pre

和后级数据dm

post

。当采用传统的整数架构前馈均衡器进行均衡补偿时,多相时钟生成电路对输入时钟进行驱动、分频后,使得主级数据与前级数据、后级数据的采样时钟的相位差为90

°

,即主级数据与前级数据、后级数据的采样时钟的相位差为

±

1u i。

103.如图3所示,考虑到要根据主级数据产生具有正负时间差的前级数据和后级数据,选择器则需要3个,但是实际应用中也可以产生具有更多时间差的各级数据,此时需要更多个选择器,本发明并不限定选择器的个数。4位并行数据经过同步电路后获得四分之一速的主级数据,以及与主级数据相差分别小于

±

1ui的前级数据、后级数据,由于是4位并行数据,则要经过4:1选择器生成前级串化数据、主级串化数据和后级串化数据,若是8位并行数据,则为8:1选择器,同理其他位数的并行数据对应相应的选择器。可以理解为,通过同步电路先产生4位并行的主级数据、前级数据和后级数据,再通过选择器将并行数据串化.

104.需要说明的是,本实施例中提供的高速接口发射机电路不只适用于不归零码信号传输,还适用于多电平脉冲调制信号的传输。本实施例中,高速接口发射机电路可以仅包括一组数据串化电路和一组均衡驱动电路,在其他实施例中,还可以包括两组数据串化电路和两组均衡驱动电路,例如高4位并行数据经过同步电路后进行串化传输,同样的,低4位并行数据的传输原理与高4位的传输原理一致,在后续实施例中进行详细说明。

105.本实施例中数据串化电路可选的,如图5所示,为本发明实施例提供的选择器结构示意图;本实施例中以选择器为4:1选择器为例进行说明。

106.所述选择器包括第十二缓冲器至第十八缓冲器和多个时钟开关。

107.其中,第十二缓冲器131、第十三缓冲器132、第十四缓冲器133、第十五缓冲器134的输入端分别用接收并行数据输入信号;第十二缓冲器131的输出端通过第一时钟开关k1、第十三缓冲器132的输出端通过第二时钟开关k2与第十六缓冲器135的输入端相连;第十六缓冲器135的输出端通过第三时钟开关k3与第十八缓冲器137的输入端相连;第十四缓冲器133的输出端通过另一组第二时钟开关k2、第十五缓冲器134的输出端通过第一时钟开关k1与第十七缓冲器136的输入端相连;第十七缓冲器136的输出端通过第四时钟开关k4与第十八缓冲器137的输入端相连;第十八缓冲器137的输出端作为选择器的输出端dout。

108.第一时钟开关k1接收第二时钟信号ck

90

的控制,第二时钟开关k2接收第四时钟信号ck

270

的控制,第三时钟开关k3接收第三时钟信号ck

180

的控制,第四时钟开关k4接收第一时钟信号ck0的控制。

109.本发明实施例中提供的选择器,通过增加第十六缓冲器135和第十七缓冲器136,使得数据串化传输过程中串行数据出现延时,也即,本实施例中提供的选择器采用两级串化结构,差分时钟ck

270

与ck

90

进行第一级串化,差分时钟ck

180

与ck0完成第二级串化。

110.串化电路中,时钟与数据的时序关系保障电路基本功能,此外,第二级时钟与数据的匹配关系决定了串化器最终输出的数据抖动。通过时钟与数据精确匹配,使得输出的数据抖动较小,结合附图1所示的眼开图,可以得知,通过本发明实施例提供的时钟生成与匹配电路的作用,能够增大眼开,减小抖动,提高系统的性能。

111.而且在时钟生成与匹配电路中引入可变电容作为缓冲器负载,微调时钟ck

180

与ck0的延迟,用以匹配串化开关选通过程需要的传输时间,从而实现时钟与数据的精准匹配,极大改善数据性能,可显著降低串化电路的输出抖动。

112.需要说明的是,在实际应用中,除了数据串化传输过程中,由于时钟不匹配造成的数据输出抖动,会引起眼开较小之外,当电路传输带宽不足时,也会引起数据的抖动,具体的,传统的发射机均衡均在输出驱动电路进行均衡计算,从而优化芯片输出信号质量,补偿芯片外部封装和走线可能产生的信号衰减。但是,当数据速率大幅提升后,不仅芯片外部信号品质下降严重,芯片内部电路带宽也会严重制约信号质量。图3所示的发射机电路结构中,主级(main-tap)数据为实际的发送数据,在驱动电路中相应驱动管因设计需要通常会选取较大尺寸,因此,其前级的mux输出负载会随之加重,导致信号传输时上升与下降沿变缓,恶化信号眼开及抖动性能。

113.基于此,本发明另一实施例还提供一种对主级数据衰减进行针对性补偿的逻辑前馈均衡(logic ffe)技术,基本原理是,在pre-tap和post-tap的数据输出端增加一条驱动能力可调支路,直连至main-tap的数据输出端,根据去加重前馈均衡的原理,对码间串扰导

致的数据拖尾衰减进行补偿,从而提升主级数据信号质量,在进入均衡驱动电路前预先进行数据抖动优化,降低数据相关抖动(dcd)。图6给出的数据频域特性可以看出,采用逻辑前馈均衡技术,可以有效扩展电路带宽,改善数据的上升沿及下降沿的边沿特性,提升数据驱动能力。

114.请参见图7,图7为本发明实施例提供的另一种高速接口发射机电路结构示意图,在数据串化电路内还设置有逻辑均衡电路。而且,本实施例中,高速接口发射机电路包括两组数据串化电路,上方为高4位数据的传输,下方为低4位数据的传输,两组数据串化电路和均衡驱动电路的结构都相同。

115.以上方的数据串化电路为例进行说明,与图3所示的数据串化电路不同的是,本实施例中提供的高速接口发射机电路中的数据串化电路还包括逻辑均衡电路14,所述逻辑均衡电路连接在所述选择器和所述均衡驱动电路之间;

116.请参见图8,图8为本发明实施例提供的逻辑均衡电路结构示意图;其中,逻辑均衡电路包括并联的多个逻辑均衡单元;每个逻辑均衡单元均包括:选择开关swm(其中m取值为1、2、3

……

n)、反相器141和逻辑门电路142;其中,选择开关swm与反相器141的输入端相连;反相器141的输出端与逻辑门电路142相连;逻辑门电路142用于接收前级串行差分数据dm

pre

和后级串行差分数据dm

post

,并输出主级串行差分数据dm

main

。

117.具体的,请参见图8,逻辑门电路包括:第一与非门1421、第一或非门1422、第二与非门1423和第二或非门1424,以及多个晶体管(t1、t2、t3、t4);第一与非门1421和第二与非门1423的第一端均与反相器141的输出端相连;第一与非门1421的第二端与第一或非门1422的第一端均用于接收前级串行差分数据dm

pre

;第二与非门1423的第二端与第二或非门1424的第一端均用于接收后级串行差分数据dm

post

;第一或非门1422和第二或非门1424的第二端均与反相器141的输入端相连。

118.多个晶体管包括第一晶体管t1、第二晶体管t2、第三晶体管t3和第四晶体管t4;第一晶体管t1的控制端与第一与非门1421的输出端相连;第二晶体管t2的控制端与第一或非门1422的输出端相连;第一晶体管t1的第一端与电源相连;第一晶体管t1的第二端与第二晶体管t2的第一端相连,且用于输出主级串行差分数据dm

main

;第二晶体管t2的第二端接地;第三晶体管t3的控制端与第二与非门1423的输出端相连;第四晶体管t4的控制端与第二或非门1424的输出端相连;第三晶体管t3的第一端与电源相连;第三晶体管t3的第二端与第四晶体管t4的第一端相连,且用于输出主级串行差分数据dm

main

;第四晶体管t4的第二端接地。

119.本实施例中为了增强设计完整性,提升技术灵活性,本实施例中提供的逻辑均衡电路为补偿能力可调节的逻辑均衡电路,如图8所示。通过选择开关的不同导通,能够选择不同倍数的驱动单元,例如选择sw0与sw1用来进行选择导通,输入控制信号后,分别控制一倍驱动单元和两倍驱动单元,根据信号速率衰减完成补偿强度地调整,在本发明的其他实施例中,逻辑均衡电路的驱动单元可以根据实际应用需求进一步扩展至n位。

120.本发明实施例提出的逻辑均衡电路为主级数据逻辑均衡技术,基于系统级设计优化思想,采用内部数据实现主级数据的前馈均衡优化,解决芯片内部数据衰减问题,优化数据边沿上升下降时间,提升芯片内部信号质量,改善系统内部节点性能。另一方面,能够扩展电路带宽,进而削弱输出信号的抖动,使得系统眼开增大,系统性能得到优化。

121.在本发明的另一实施例中,还可以通过将驱动带宽扩展,实现减弱输出数据抖动的目的。请参见图9,图9为本发明实施例提供的一种高速接口发射机电路结构示意图;

122.与图7不同的是,本实施例中提供的高速接口发射机电路中均衡驱动电路21为非传统结构,其中,每组均衡驱动电路包括正均衡驱动电路和负均衡驱动电路,本实施例中正均衡驱动电路和负均衡驱动电路的结构相同,只是输入信号为正负相反的差分信号。

123.本实施例中以正均衡驱动电路为例进行说明,负均衡驱动电路的结构与正均衡驱动电路的结构一致,本实施例中对此不作限定。

124.请参见图10,图10为本发明实施例提供的正均衡驱动电路的结构示意图;所述正均衡驱动电路具体包括:

125.前级均衡控制电路211、后级均衡控制电路212、主级均衡控制电路213和第一电容c1、第二电容c2;

126.前级均衡控制电路211包括第五晶体管t5、第六晶体管t6、第七晶体管t7和第八晶体管t8;

127.主级均衡控制电路213包括第九晶体管(图中213模块左上角所示)、第十晶体管(图中213模块右上角所示)、第十一晶体管(图中213模块左下角所示)和第十二晶体管(图中213模块右下角所示);

128.后级均衡控制电路212包括第十三晶体管t13、第十四晶体管t14、第十五晶体管t15和第十六晶体管t16;

129.第五晶体管t5和第六晶体管t6的控制端均接收前级偏置电压输入vb

pre

;第五晶体管t5的第一端用于与第九晶体管和第十三晶体管t13的第一端相连,并用于与一个负载电阻r

t

的一端相连,也即节点on,作为均衡驱动电路的一个输出端;

130.第六晶体管t6的第一端用于与十晶体管和第十四晶体管t14的第一端相连,并用于与另一负载电阻r

t

的一端相连,也即节点op,作为均衡驱动电路的另一个输出端;

131.第五晶体管t5的第二端与第七晶体管t7的第一端相连,第七晶体管t7的控制端用于接收前级串行差分数据的负差分数据dm

pre_n

;

132.第六晶体管t6的第二端与第八晶体管t8的第一端相连,第八晶体管t8的控制端用于接收前级串行差分数据的正差分数据dm

pre_p

;

133.第九晶体管和第十晶体管的控制端均接收主级偏置电压输入vb

main

;第九晶体管的第二端与第十一晶体管的第一端相连,第十一晶体管的控制端用于接收主级串行差分数据的正差分数据dm

main_p

;

134.第十晶体管的第二端与第十二晶体管的第一端相连,第十二晶体管的控制端用于接收主级串行差分数据的负差分数据dm

main_n

;

135.第十三晶体管t13和第十四晶体管t14的控制端均接收后级偏置电压输入vb

post

;第十三晶体管t13的第二端与第十五晶体管t15的第一端相连,第十五晶体管t15的控制端用于接收后级串行差分数据的负差分数据dm

post_n

;

136.第十四晶体管t14的第二端与第十六晶体管t16的第一端相连,第十六晶体管t16的控制端用于接收后级串行差分数据的正差分数据dm

post_p

;

137.第七晶体管t7的第二端、第八晶体管t8、第十一晶体管、第十二晶体管、第十五晶体管t15和第十六晶体管t16的第二端均接地;

138.第一电容c1的一端与第十晶体管的第二端相连,第一电容c1的另一端与第十一晶体管的控制端相连;

139.第二电容c2的一端与第九晶体管的第二端相连,第二电容c2的另一端与第十二晶体管的控制端相连。

140.本实施例中提供的均衡驱动电路(msb combiner),电路整体采用电流模输出驱动方式,当输出负载电阻rt阻值固定时,输入对管的偏置电流决定了输出信号幅度;pre-tap数据与post-tap数据用于进行输出均衡,因此与main-tap数据的输出反相连接;msb combiner与lsmcombiner共同作用,产生最终的调制脉冲即发射的pam4数据(根据数据编码方式的差异,也可产生nrz数据)。本发明实施例与之前实施例不同的是:引入了一对跨接在输入差分对管栅极与漏极间的电容,其功能是提供一条输出信号快速建立通路,从而加快输出信号建立过程,等效提升驱动电路的整体带宽,提升电路的驱动负载能力,显著优化输出信号眼图的眼开与抖动性能,实现系统优化。也即通过跨接的交叉电容加速驱动电路输出信号建立,在不增加额外电流开销的前提下实现电路带宽性能地有效提升,可以有效优化芯片输出信号质量。

141.在本发明的另一实施例中,还可以如图11所示,图11为本发明实施例提供的另一种高速接口发射机电路结构示意图;本实施例中提供的高速结构发射机电路结构,时钟生成与匹配电路以及均衡驱动电路均为本发明实施例中提供的结构,而数据串化电路并未进行改进,包括现有技术中的结构,并未增加设置逻辑均衡电路。

142.也即,本发明实施例中提供的高速接口发射机电路,通过时钟生成与匹配电路使得数据与时钟精确匹配,减小输出信号的抖动;另外,通过跨接的交叉电容加速懂电路输出信号建立,有效提升电路带宽性能,同样也可以减小输出信号的抖动,增大眼开,从而提升系统性能。

143.综上所述,本发明基于系统级设计,提出一系列发射机芯片内部带宽扩展及抖动优化技术,包含主级数据逻辑均衡技术、串化时序匹配技术、驱动带宽扩展技术。上述技术弥补了现有的发射机芯片电路设计中的缺失,从信号源头实现设计优化,可以大大改善发射机数据抖动性能,提升通信速率。提出的技术对于百g以上高速串行发射机芯片设计具有重要价值,不仅通过提升带宽实现了传输速率的提升,还通过信号匹配实现了内部数据传输抖动的优化,能够实现信号传输品质的有效改进;并且具有良好的设计兼容性,不仅可以应用于nrz与pam4的数据传输模式,还可以扩展至高速模拟电路设计领域,优化高速数模混合芯片内部关键设计。

144.基于相同的发明构思,本发明还提供一种高速接口发射机芯片,所述高速接口发射机芯片包括上面任意实施例中所述的高速接口发射机电路。

145.在本发明的另一实施例中,作为一种可能的实现方式,图12示例出本发明实施例提供的电子设备的结构示意图,如图12所示,上述电子设备100还包括与存储器102通信的处理器101。

146.在一些情况下,如图11所示,上述电子设备100所包括的存储器102和处理器101可以与通信接口等装置集成在一起,并封装成芯片,构成应用于电子设备的芯片。

147.与现有技术相比,本发明实施例提供的电子设备的有益效果与存储器的有益效果相同,在此不做赘述。

148.需要说明的是,本说明书中的各个实施例均采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似的部分互相参见即可。

149.还需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括上述要素的物品或者设备中还存在另外的相同要素。

150.对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1