无限串接拓扑结构与通信方法与流程

1.本发明涉及一种拓扑结构与通信方法,特别涉及一种无限串接拓扑结构与通信方法。

背景技术:

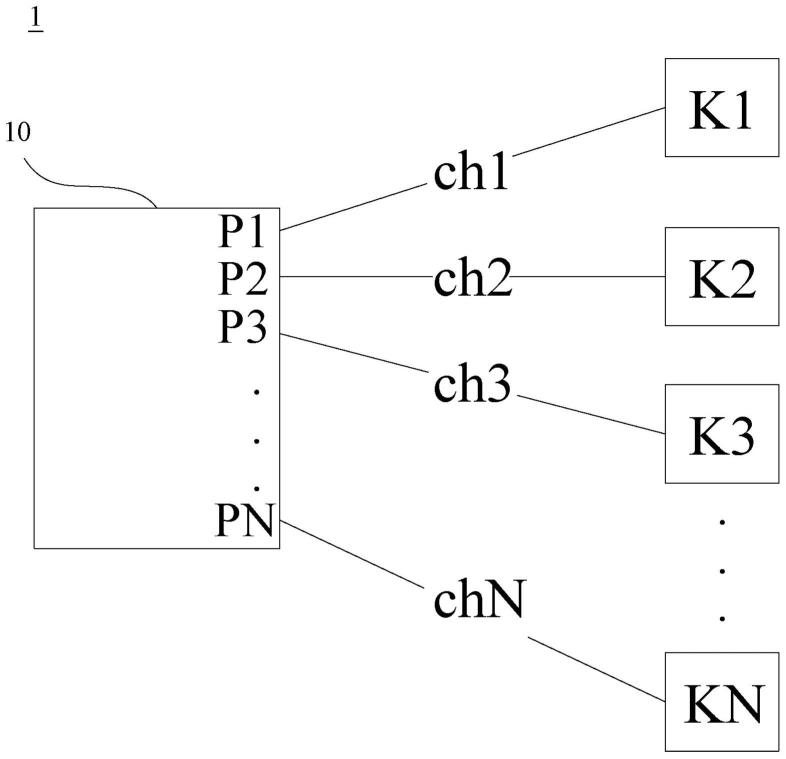

2.请参照图1,图1用于触控装置的现有拓扑结构1。如图1所示,微处理器10的引脚p1~pn分别通过通道ch1~chn对应地连接感测元件k1~kn。虽然可同时控制感测元件k1~kn,然而却因为处理器引脚数量使得连接的感测元件数量受限。

3.另外,通道ch1~chn之间也会彼此干扰,像是有线连接的通道ch1~chn因接线缠绕造成的触控误判,而有线连接的通道ch1~chn也会因接线的长度过长导致各通道的负载差异过大,造成触控演算感应失败。

4.因此,需要提出一种改进的拓扑结构,以解决上述数量受限与连接感测元件感测错误等问题。

技术实现要素:

5.为达到有效解决上述问题的目的,本发明提出一种无限串接拓扑结构,包括一微处理器以及多个感测元件。该微处理器包含一数据输出引脚、一时钟输出引脚以及一数据输入引脚。该多个感测元件按序串接至该微处理器,且每一该多个感测元件包含一处理单元、一信息感测单元、一输入序列单元、一输出序列单元以及一选择单元。其拓扑结构实现于触控装置,则感测元件的信息感测单元即为触控单元,该信息感测单元耦接该处理单元。该输入序列单元耦接该处理单元并接收一输入数据序列与一时钟输入。该输出序列单元耦接该处理单元并输出一输出数据序列。该选择单元耦接该输入序列单元与该输出序列单元,并接收一时钟输入与一切换信号,以根据该切换信号决定是否输出一时钟输出。该多个感测元件中最后一个按序串接的感测元件的一输出数据序列为传送至该数据输入引脚的一数据反馈序列。

6.根据本发明一实施例,当该选择单元根据该切换信号决定不输出该时钟输出时,该多个感测元件个别接收的该时钟输入皆相同且是由该时钟输出引脚所传出。

7.根据本发明一实施例,每一该多个感测元件的该选择单元根据该切换信号决定输出该时钟输出,且按序串接至该微处理器的该多个感测元件中的第一个感测元件的一时钟输入是从该时钟输出引脚所传出,其余的该感测元件个别接收的时钟输入皆为上一感测元件的时钟输出。

8.根据本发明一实施例,该微处理器还包含一时钟输入引脚,且该最后一个按序串接的感测元件的该时钟输出为传送至该时钟输入引脚的一时钟反馈。

9.根据本发明一实施例,该最后一个按序串接的感测元件不会传送时钟输出至该处理器。

10.本发明还提出一种无限串接拓扑通信方法,包括:将多个感测元件按序串接至一

微处理器;从该微处理器接收一输入数据序列与一时钟输入;在每一该感测元件输出一输出数据序列;以及在每一该感测元件接收一时钟输入与一切换信号,以根据该切换信号决定是否输出一时钟输出。该多个感测元件中最后一个按序串接的感测元件的一输出数据序列为传送至该微处理器的一数据反馈序列。

11.本发明的无限串接拓扑结构的串接方式不会有因接线缠绕造成触控误判、接线的长度过长导致负载差异过大与感测元件感应失败等问题,同时串接的感测元件(按键)不会有数量限制。

附图说明

12.图1是用于触控装置的现有拓扑结构示意图;

13.图2是依据本发明第一实施例的拓扑结构示意图;

14.图3是依据本发明第二实施例的拓扑结构示意图;

15.图4是依据本发明第三实施例的拓扑结构示意图;

16.图5是依据本发明一实施例的感测元件方框图;

17.图6是图2的拓扑结构的时序图;

18.图7是图4的拓扑结构的时序图;

19.图8是图2的拓扑结构的符号示意图;以及

20.图9是图3的拓扑结构的符号示意图。

21.符号说明

22.1、2、3、4:拓扑结构

23.10、20、30、40:微处理器

24.100:信息感测单元

25.101:输入序列单元

26.102:输出序列单元

27.103:处理单元

28.104:选择单元

29.k1~kn:感测元件

30.p1~pn:引脚

具体实施方式

31.请参照图2,图2是依据本发明第一实施例的拓扑结构2示意图。如图2所示,该拓扑结构2包括一微处理器20以及n个感测元件k1~kn。该微处理器20包含一数据输出引脚dout、一时钟输出引脚cout以及一数据输入引脚din。该n个感测元件按序串接至该微处理器20。如图5所示,每一感测元件包含一处理单元103、一信息感测单元100、一输入序列单元101、一输出序列单元102以及一选择单元104。该信息感测单元100耦接该处理单元103。该输入序列单元101耦接该处理单元103并接收一输入数据序列di(如图2中的di1~din)与一时钟输入ci。该输出序列单元102耦接该处理单元103并输出一输出数据序列do。该选择单元104耦接该输入序列单元101与该输出序列单元102,并接收一时钟输入ci与一切换信号sx,以根据该切换信号sx决定是否输出一时钟输出co。在此第一实施例中该选择单元104是

根据该切换信号sx选择m1模式决定不输出该时钟输出co,该n个感测元件k1~kn个别接收的该时钟输入ci皆为ck且是由该时钟输出引脚cout所传出。该n个感测元件中最后一个按序串接的感测元件kn的一输出数据序列为传送至该数据输入引脚din的一数据反馈序列dfb。

32.请参照图3,图3是依据本发明第二实施例的拓扑结构3示意图。如图3所示,该拓扑结构3包括一微处理器30以及n个感测元件k1~kn。该微处理器30包含一数据输出引脚dout、一时钟输出引脚cout以及一数据输入引脚din。该n个感测元件按序串接至该微处理器20。如图5所示,每一感测元件包含一处理单元103、一信息感测单元100、一输入序列单元101、一输出序列单元102以及一选择单元104。该信息感测单元100耦接该处理单元103。该输入序列单元101耦接该处理单元103并接收一输入数据序列di与一时钟输入ci。该输出序列单元102耦接该处理单元103并输出一输出数据序列do。该选择单元104耦接该输入序列单元101与该输出序列单元102,并接收一时钟输入ci与一切换信号sx,以根据该切换信号sx决定是否输出一时钟输出co。在此第二实施例中该选择单元104是根据该切换信号sx选择m2模式决定输出该时钟输出co,且按序串接至该微处理器30的该n个感测元件中的第一个感测元件k1的一时钟输入ci是从该时钟输出引脚cout所传出,其余的该感测元件个别接收的时钟输入ci皆为上一感测元件的时钟输出co。该n个感测元件中最后一个按序串接的感测元件kn的一输出数据序列为传送至该数据输入引脚din的一数据反馈序列dfb。该最后一个按序串接的感测元件kn不会传送时钟输出至该处理器30。

33.请参照图4,图4是依据本发明第三实施例的拓扑结构4示意图。如图4所示,该拓扑结构4包括一微处理器40以及n个感测元件k1~kn。该微处理器30包含一数据输出引脚dout、一时钟输出引脚cout以及一数据输入引脚din。该n个感测元件按序串接至该微处理器20。

34.请参照图5,图5是依据本发明一实施例的感测元件方框图。如图5所示,每一感测元件包含一处理单元103、一信息感测单元100、一输入序列单元101、一输出序列单元102以及一选择单元104。该信息感测单元100耦接该处理单元103。该输入序列单元101耦接该处理单元103并接收一输入数据序列di与一时钟输入ci。该输出序列单元102耦接该处理单元103并输出一输出数据序列do。该选择单元104耦接该输入序列单元101与该输出序列单元102,并接收一时钟输入ci与一切换信号sx,以根据该切换信号sx决定是否输出一时钟输出co。在此第三实施例中该选择单元104是根据该切换信号sx选择m2模式决定输出该时钟输出co,且按序串接至该微处理器30的该n个感测元件中的第一个感测元件k1的一时钟输入ci是从该时钟输出引脚cout所传出,其余的该感测元件个别接收的时钟输入ci皆为上一感测元件的时钟输出co。该n个感测元件中最后一个按序串接的感测元件kn的一输出数据序列为传送至该数据输入引脚din的一数据反馈序列dfb。该处理器40还包含一时钟输入引脚cin,该最后一个按序串接的感测元件kn的该时钟输出co为传送至该时钟输入引脚cin的一时钟反馈cfb。

35.请参照图6,图6是图2的拓扑结构的时序图。如图6所示,第一实施例的拓扑结构中有四个感测元件k1~k4(n=4),输入数据序列di1~di4分别输入感测元件k1~k4的输入序列单元101,其中输入数据序列di2~di4分别是感测元件k1~k3的输出数据序列,而感测元件k4的输出数据序列,也就是数据反馈序列dfb被传至该处理器20的该数据输入引脚din。

输入数据序列di1~di4中的符号req与end间包含了感测元件k1~k4的触控信号,因此可看到从感测元件k1~k3的输出数据序列di2~di4中分别包含了感测元件k1、感测元件k1和k2以及感测元件k1~k3的触控信号,而感测元件k4回传至该处理器20的数据反馈序列dfb包含了感测元件k1~k4的触控信号。

36.请参照图8,图8是图2的拓扑结构的符号示意图,与图6同样是n=4的情形,当中符号req以0代表、符号end以6代表、符号null以f代表。

37.请参照图7,图7是图4的拓扑结构的时序图。如图7所示,在四个感测元件k1~k4的情形下,第三实施例不同于图6第二实施例在于第三实施例中按序串接至该微处理器30的该四个感测元件中的第一个感测元件k1的一时钟输入ci是从该时钟输出引脚cout所传出的co1,其余的该感测元件k2~k4个别接收的时钟输入分别是上一感测元件k1~k3的时钟输出co2~co4,该最后一个按序串接的感测元件k4的该时钟输出为传送至该时钟输入引脚cin的一时钟反馈。因此,输入数据序列di1~di4与数据反馈序列dfb的符号序列对比于图6的情形会按序向右延迟。

38.请参照图9,图9是图3的拓扑结构的符号示意图,与图6~图8同样是n=4的情形,当中符号req以0代表、符号end以6代表、符号null以f代表。

39.本发明的无限串接拓扑结构的串接方式不会有因接线缠绕造成触控误判、接线的长度过长导致负载差异过大与感测元件感应失败等问题,同时感测元件(按键)不会有数量限制。

40.本发明不限于上述实施例,对于本技术领域的技术人员显而易见的是,在不脱离本发明的构思或范围的情况下,可对本发明作出各种修改和变化。

41.因此,本发明旨在涵盖对本发明或落入所附权利要求及其均等范围内所作的修改与变化。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1