一种高能效高速并行LDPC编码方法及编码器

一种高能效高速并行ldpc编码方法及编码器

技术领域

1.本发明涉及卫星超高速信息传输、信道编码技术领域,特别涉及一种高能效高速并行ldpc编码方法及编码器。

背景技术:

2.随着天基信息港、卫星互联网、分布式星群等技术的快速发展,星间、星地数据传输的需求急剧上升。空间通信载荷资源受限与高速、大容量通信需求直接的矛盾日益突出,如何在平台资源、体积、功耗严格受约束的前提下开展高性能信号处理理论和实现技术研究,具有重要的应用价值。

3.低密度奇偶校验(ldpc,low density parity check)码具有可逼近香农限的纠错能力,是保障通信可靠性的重要手段,在深空探测、卫星通信等领域得到了广泛应用。借助校验矩阵的稀疏特性,ldpc译码可得到高效的实现,但其生成矩阵往往没有规律性,导致编码复杂度很高。准循环ldpc码作为一种结构化的ldpc码,较好地解决了这一问题。其校验矩阵和生成矩阵由大小相同的循环移位子矩阵构成,便于硬件实现。目前,国际空间数据系统咨询委员会(ccsds,consultative committee for space date system)制定的深空通信和近地通信标准中均采用此类ldpc码。

4.为设计符合超高速通信需求的ldpc编码器,需采用高并行度的实现方法。准循环ldpc(n,k)码的生成矩阵可表示为g=[i|p]的形式,其中i表示单位矩阵,由k

×

k个单位矩阵i

m

×

m

组成;部分校验矩阵p由m

×

m维的循环矩阵b

ij

(1≤i≤k,1≤j≤n

‑

k)组成;因此码字长度为n=n

·

m,其中信息位长度为k=k

·

m。编码过程为c1×

n

=u1×

k

·

g

k

×

n

,利用子矩阵的结构特性,可将信息序列分段然后采用移位寄存器累加单元实现多路并行编码。但由于编码矩阵p的非稀疏特性,并行编码过程中存在硬件资源占用多、功耗大等问题。

[0005]

现有技术中,国内li等提出了一种生成矩阵的推导公式,由此设计出基于移位寄存器累加(shift register adder accumulator,sraa)方法的准循环ldpc码的编码器架构,可实现结构简单、低复杂度的编码器。但是,串行sraa编码器处理时延大、吞吐量低,不适用于高速设计;并行sraa编码器使用的寄存器太大,消耗资源多,应用受限。张仲明等人针对并行sraa结构组帧延时大的问题提出了改进,不需一帧数据完全采集到就可进行编码,但是编码器受限于ldpc码准循环矩阵尺寸的整数因子分解情况,当阶数为素数时,就不可以使用这种方法进行编码。以上编码方案都是基于sraa编码方法及其改进。因此,研究设计一种低复杂度、高能效的ldpc编码方法具有重要的应用价值。

技术实现要素:

[0006]

本发明的目的在于提供一种高能效高速并行ldpc编码方法及编码器,在信息序列与生成矩阵的相乘运算过程中,根据生成矩阵p矩阵部分非零元素的位置选择出相应的信息比特进行处理,从而达到降低编码实现复杂度的目的。

[0007]

为解决上述技术问题,本发明的实施例提供如下方案:

[0008]

一方面,提供了一种高能效高速并行ldpc编码方法,包括以下步骤:

[0009]

将输入的串行或并行信息序列,按照准循环ldpc码循环移位子矩阵大小分为多段,并转换为全并行数据模式;

[0010]

对分段信息序列进行循环移位;

[0011]

根据循环移位子矩阵第一列中非零元素的位置,选择相应位置的信息比特;

[0012]

将多段选择后的信息比特进行合并;

[0013]

采用流水线处理方式将合并后的信息比特进行模二累加,得到相应的校验比特;

[0014]

将串行校验比特转换为全并行数据模式;

[0015]

输出编码结果。

[0016]

优选地,所述编码方法具体包括:

[0017]

将输入的信息序列按照循环移位子矩阵的大小分成k段u={u1,u2,

…

,u

k

},其中u

i

={u

(i

‑

1)m+1

,u

(i

‑

1)m+2

,

…

,u

im

},1≤i≤k;

[0018]

将生成矩阵中的p矩阵划分为循环移位子矩阵b

ij

(1≤i≤k,1≤j≤n

‑

k),校验位分段表示为:v={v1,v2,

…

,v

n

‑

k

}且v

j

={v

(j

‑

1)m+1

,v

(j

‑

1)m+2

,

…

,v

jm

},其计算过程表示为:

[0019]

重复上述过程得到所有校验向量v

j

(j=1,2,

…

,n

‑

k),则编码输出为{u,v1,v2,

…

,v

n

‑

k

}。

[0020]

优选地,所述校验向量计算过程包括:

[0021]

逐项计算u

i

·

b

ij

:

[0022]

取b

ij

矩阵中的第一列从这个m

×

1向量中找出b

ij

非零元素的位置集合其中β

l

(1≤l≤d

ij

)表示第l个非零元素的位置,d

ij

表示b

ij

中非零元素的数量;

[0023]

根据位置集合λ

ij

选择u

i

中的有效比特{u

i

(β

l

),β

l

∈λ

ij

},对其模二累加求和得到等效于计算u

i

·

b

ij

;

[0024]

对第i段信息序列u

i

进行循环移位,得到共计m

‑

1个信息向量,利用上述步骤得到h

ij

(1),h

ij

(2),

…

,h

ij

(m

‑

1),并得到h

ij

={h

ij

(0),h

ij

(1),

…

,h

ij

(m

‑

1)}=u

i

·

b

ij

;

[0025]

计算所有的h

ij

(i=1,2,

…

,k),对向量h

ij

进行模二累加,即得到相应的校验向量

[0026]

一方面,提供了一种高能效高速并行ldpc编码器,包括:

[0027]

数据预处理模块,用于将输入的串行或并行信息序列,按照生成矩阵中循环移位子矩阵大小分为多段,并转换为全并行数据模式;

[0028]

多个循环移位模块,用于对分段信息序列进行循环移位;

[0029]

多个比特选择模块,用于根据循环移位子矩阵第一列中非零元素的位置,选择相应位置的信息比特;

[0030]

多个比特合并模块,用于将多个比特选择模块的输出进行合并;

[0031]

流水累加模块,用于采用流水线处理方式将合并后的信息比特进行模二累加,得

到相应的校验比特;

[0032]

串并转换模块,用于将串行校验比特转换为全并行数据模式;

[0033]

编码输出模块,用于输出编码结果。

[0034]

优选地,所述数据预处理模块具体用于:

[0035]

将输入的串行或并行信息序列,按照循环移位子矩阵大小分为k段u={u1,u2,

…

,u

k

},其中u

i

={u

(i

‑

1)m+1

,u

(i

‑

1)m+2

,

…

,u

im

},1≤i≤k,并转化为全并行数据模式,每段数据均为m比特并行数据流。

[0036]

优选地,所述多个循环移位模块具体用于:

[0037]

将分段后的信息序列u={u1,u2,

…

,u

k

}分别送到k个循环移位网络中,其中,仅分段信息序列进入循环移位网络的第一个时钟周期不进行移位操作,接下来的m

‑

1个时钟周期信息序列依次右移一位,在m个时钟周期内每段信息序列u

i

均得到共计m个移位之后的信息向量。

[0038]

优选地,将校验位分段为v={v1,v2,

…

,v

n

‑

k

}且v

j

={v

(j

‑

1)m+1

,v

(j

‑

1)m+2

,

…

,v

jm

},同时计算n

‑

k段校验位;

[0039]

所述多个比特选择模块具体用于:

[0040]

将比特选择模块分为(n

‑

k)组,每组比特选择模块分别根据相应k个循环移位子矩阵的首列非零元素对k段信息序列进行比特选择,共需要k(n

‑

k)个比特选择模块;

[0041]

将循环移位子矩阵b

ij

的第一列非零元素位置集合分别加载到对应的比特选择模块中,非零元素位置寄存器s也初始化为相同的值;将上一步骤中k个循环移位网络的输出作为每组比特选择模块的输入,根据非零元素寄存器s选择中的有效比特,每个比特选择模块在m个时钟周期内均得到共计m个信息向量,向量长度为d

ij

,分别对应第i行第j列循环移位子矩阵非零元素的长度。

[0042]

优选地,所述多个比特合并模块具体用于:

[0043]

每个比特合并模块用于将一组比特选择模块的k个输出进行拼接,p矩阵是一个稠密矩阵,密度为0.5,每段信息序列经过比特选择模块之后的输出为m/2,经过比特合并模块后的长度约为k

·

m/2,共需要(n

‑

k)个比特合并模块。

[0044]

优选地,所述流水累加模块具体用于:

[0045]

采用流水线处理方式将合并后的信息比特进行累加,得到校验位v

j

(1≤j≤n

‑

k);编码中采用模二加法,共需要个异或门,完成累加需要个处理时钟。

[0046]

优选地,所述编码输出模块具体用于:将信息位和校验位组合输出。

[0047]

本发明实施例提供的技术方案带来的有益效果至少包括:

[0048]

本发明针对准循环ldpc的编码过程,生成矩阵的非稀疏性导致信息序列与其直接相乘复杂度较高的问题,提出了一种简化实现方法,根据生成矩阵中非零元素位置,对信息序列先进行比特选择,然后再进行编码计算,能够有效避免无效信息比特的运算,减少编码计算所需的运算数,将比特异或运算所需的逻辑电路减少至原来的一半,从而显著降低编码器的整体硬件资源消耗。

附图说明

[0049]

为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

[0050]

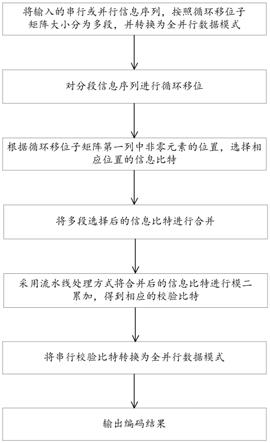

图1是本发明实施例提供的一种高能效高速并行ldpc编码方法的流程图;

[0051]

图2是本发明实施例提供的一种高能效高速并行ldpc编码器的整体架构示意图;

[0052]

图3是本发明实施例提供的循环移位模块和比特选择模块的示意图;

[0053]

图4是本发明实施例提供的流水累加模块的示意图。

具体实施方式

[0054]

为使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明实施方式作进一步地详细描述。

[0055]

实施例一

[0056]

本发明的实施例提供了一种高能效高速并行ldpc编码方法,如图1所示,所述方法包括以下步骤:

[0057]

将输入的串行或并行信息序列,按照准循环ldpc码循环移位子矩阵大小分为多段,并转换为全并行数据模式;

[0058]

对分段信息序列进行循环移位;

[0059]

根据循环移位子矩阵第一列中非零元素的位置,选择相应位置的信息比特;

[0060]

将多段选择后的信息比特进行合并;

[0061]

采用流水线处理方式将合并后的信息比特进行模二累加,得到相应的校验比特;

[0062]

将串行校验比特转换为全并行数据模式;

[0063]

输出编码结果。

[0064]

本发明方法根据生成矩阵中非零元素位置,对信息序列先进行比特选择,然后再进行编码计算,能够有效避免无效信息比特的运算,减少编码计算的复杂度。

[0065]

进一步地,所述编码方法具体包括:

[0066]

将输入的信息序列按照循环移位子矩阵的大小分成k段u={u1,u2,

…

,u

k

},其中u

i

={u

(i

‑

1)m+1

,u

(i

‑

1)m+2

,

…

,u

im

},1≤i≤k;

[0067]

将生成矩阵中的p矩阵划分为循环移位子矩阵b

ij

(1≤i≤k,1≤j≤n

‑

k),校验位分段表示为:v={v1,v2,

…

,v

n

‑

k

}且v

j

={v

(j

‑

1)m+1

,v

(j

‑

1)m+2

,

…

,v

jm

},其计算过程表示为:

[0068]

重复上述过程得到所有校验向量v

j

(j=1,2,

…

,n

‑

k),则编码输出为{u,v1,v2,

…

,v

n

‑

k

}。

[0069]

其中,所述校验向量计算过程包括:

[0070]

逐项计算u

i

·

b

ij

:

[0071]

取b

ij

矩阵中的第一列从这个m

×

1向量中找出b

ij

非零元素的位置集合其中β

l

(1≤l≤d

ij

)表示第l个非零元素的位置,d

ij

表示b

ij

中

非零元素的数量;

[0072]

根据位置集合λ

ij

选择u

i

中的有效比特{u

i

(β

l

),β

l

∈λ

ij

},对其模二累加求和得到等效于计算u

i

·

b

ij

;

[0073]

对第i段信息序列u

i

进行循环移位,得到共计m

‑

1个信息向量,利用上述步骤得到h

ij

(1),h

ij

(2),

…

,h

ij

(m

‑

1),并得到h

ij

={h

ij

(0),h

ij

(1),

…

,h

ij

(m

‑

1)}=u

i

·

b

ij

;

[0074]

计算所有的h

ij

(i=1,2,

…

,k),对向量h

ij

进行模二累加,即得到相应的校验向量

[0075]

下面以ccsds近地空间通信标准中的ldpc(7154,8176)码为例,对提出的ldpc编码方法的实现过程进行详细说明。

[0076]

所述ldpc编码方法的具体实施步骤如下:

[0077]

步骤1:本实施例中的ldpc码生成矩阵

[0078][0079]

由14

×

16个511

×

511的循环移位子矩阵组成,其中i表示单位矩阵,b

ij

(1≤i≤14,1≤j≤2)为非稀疏的循环移位矩阵,校验位的计算是通过信息序列u与g的后2列相乘得到的。根据分块计算的原则,可先将信息序列u分成14段u

i

={u

(i

‑

1)

×

511+1

,u

(i

‑

1)

×

511+2

,

…

,u

i

×

511

};

[0080]

步骤2:生成矩阵的p矩阵部分b

ij

(1≤i≤14,1≤j≤2)为循环移位矩阵,为b

lj

的首列元素。校验位可以分段表示为v={v1,v2}且v

j

={v

(j

‑

1)

×

511+1

,v

(j

‑

1)

×

511+2

,

…

,v

j

×

511

},校验位的计算过程可以表示为

[0081]

逐项计算u

l

·

b

lj

,具体包括以下步骤:

[0082]

步骤2.1:取b

lj

矩阵中的第一列从这个511

×

1向量中找出b

ij

非零元素的位置集合其中β

l

(1≤l≤d

ij

)表示第l个非零元素的位置,d

ij

表示b

ij

中非零元素的数量;

[0083]

步骤2.2:根据位置集合λ

ij

选择u

i

中的有效比特{u

i

(β

l

),β

l

∈λ

ij

},对其模2累加求和即可得到等效于计算u

i

·

b

ij

;

[0084]

步骤2.3:对第i段信息序列u

i

进行循环移位,得到共计510个信息向量,利用步骤2.1~2.2可以得到h

ij

(1),h

ij

(2),

…

,h

ij

(510);于是,得到h

ij

={h

ij

(0),h

ij

(1),

…

,h

ij

(510)}=u

i

·

b

ij

;

[0085]

步骤2.4:根据步骤2.1~2.3计算得到所有的h

ij

(i=1,2,

…

,14,j=1,2),对向量

h

ij

进行模2累加,即可得到相应的校验向量

[0086]

步骤3:重复步骤2即可得到所有的校验向量v

j

(j=1,2),于是编码输出为{u,v1,v2}。

[0087]

实施例二

[0088]

相应地,本发明还提供了一种基于上述高能效高速并行ldpc编码方法的ldpc编码器,如图2所示,所述编码器包括:

[0089]

数据预处理模块,用于将输入的串行或并行信息序列,按照生成矩阵中循环移位子矩阵大小分为多段,并转换为全并行数据模式;

[0090]

多个循环移位模块,用于对分段信息序列进行循环移位;

[0091]

多个比特选择模块,用于根据循环移位子矩阵第一列中非零元素的位置,选择相应位置的信息比特;

[0092]

多个比特合并模块,用于将多个比特选择模块的输出进行合并;

[0093]

流水累加模块,用于采用流水线处理方式将合并后的信息比特进行模二累加,得到相应的校验比特;

[0094]

串并转换模块,用于将串行校验比特转换为全并行数据模式;

[0095]

编码输出模块,用于输出编码结果;具体地,用于将信息位和校验位组合输出。

[0096]

进一步地,所述数据预处理模块具体用于:

[0097]

将输入的串行或并行信息序列,按照循环移位子矩阵大小分为k段u={u1,u2,

…

,u

k

},其中u

i

={u

(i

‑

1)m+1

,u

(i

‑

1)m+2

,

…

,u

im

},1≤i≤k,并转化为全并行数据模式,每段数据均为m比特并行数据流。

[0098]

进一步地,如图3所示,所述多个循环移位模块具体用于:

[0099]

将分段后的信息序列u={u1,u2,

…

,u

k

}分别送到k个循环移位网络中,其中,仅分段信息序列进入循环移位网络的第一个时钟周期不进行移位操作,接下来的m

‑

1个时钟周期信息序列依次右移一位,在m个时钟周期内每段信息序列u

i

均得到共计m个移位之后的信息向量。

[0100]

进一步地,将校验位分段为v={v1,v2,

…

,v

n

‑

k

}且v

j

={v

(j

‑

1)m+1

,v

(j

‑

1)m+2

,

…

,v

jm

},同时计算n

‑

k段校验位。

[0101]

所述多个比特选择模块具体用于:

[0102]

将比特选择模块分为(n

‑

k)组,每组比特选择模块分别根据相应k个循环移位子矩阵的首列非零元素对k段信息序列进行比特选择,共需要k(n

‑

k)个比特选择模块;

[0103]

将循环移位子矩阵b

ij

的第一列非零元素位置集合分别加载到对应的比特选择模块中,非零元素位置寄存器s也初始化为相同的值;将上一步骤中k个循环移位网络的输出作为每组比特选择模块的输入,根据非零元素寄存器s选择中的有效比特,每个比特选择模块在m个时钟周期内均得到共计m个信息向量,向量长度为d

ij

,分别对应第i行第j列循环移位子矩阵非零元素的长度。

[0104]

进一步地,所述多个比特合并模块具体用于:

[0105]

每个比特合并模块用于将一组比特选择模块的k个输出进行拼接,由于p矩阵是一

个稠密矩阵,密度约为0.5,所以每段信息序列经过比特选择模块之后的输出大约为m/2,经过比特合并模块后的长度约为k

·

m/2,共需要(n

‑

k)个比特合并模块。

[0106]

进一步地,如图4所示,所述流水累加模块具体用于:

[0107]

采用流水线处理方式将合并后的信息比特进行累加,得到校验位v

j

(1≤j≤n

‑

k);编码中采用模二加法,共需要个异或门,完成累加需要个处理时钟。

[0108]

本发明的优势在于考虑到信息比特与生成矩阵模二加运算的特性,对传统的信息序列与生成矩阵直接相乘后累加的操作进行了简化,使用比特选择模块来代替信息序列与p矩阵部分直接相乘运算,节约了一半异或门的数量,显著降低了资源消耗。

[0109]

下面以ccsds近地空间通信标准中的ldpc(7154,8176)码为例,对提出的ldpc编码方法的实现过程进行详细说明。

[0110]

所述ldpc编码器,包括数据预处理模块、循环移位模块、比特选择模块、比特合并模块、流水累加模块、串并转换模块和编码输出模块。

[0111]

所述循环移位模块,用于对分段信息序列u

i

(1≤i≤14)进行循环移位,进而计算校验位。所述比特选择模块,用于加载生成矩阵p矩阵部分的循环移位子矩阵b

ij

第一列非零元素的位置,根据非零元素的位置来选择u

i

中相应位置的信息比特。所述比特合并模块,用于将28个比特选择模块的输出进行合并,送到流水累加模块去进行求和。所述流水累加模块,采用流水线方式将合并后的比特信息进行累加,得到相应的校验比特。所述串并转换模块,将串行校验比特转换为并行数据。所述输出编码模块,用于输出编码的最终码字,包括信息比特向量u和校验向量v。

[0112]

编码步骤如下:

[0113]

步骤1.信息位分段。对编码输入数据进行预处理,将信息序列按照循环移位子矩阵大小分为14段u={u1,u2,

…

,u

14

},其中u

i

={u

(i

‑

1)

×

511+1

,u

(i

‑

1)

×

511+2

,

…

,u

i

×

511

},1≤i≤14,每段数据均为511比特并行数据流。

[0114]

步骤2.信息位循环移位。将分段后的信息序列u={u1,u2,

…

,u

14

}分别送到14个循环移位网络中,有且只有分段信息序列进入循环移位网络的第一个时钟周期不进行移位操作,接下来的510个时钟周期信息序列依次右移一位,在511个时钟周期内每段信息序列u

i

都可以得到共计511个移位之后的信息向量。

[0115]

步骤3.信息位比特选择。将校验位分段为v={v1,v2}且v

j

={v

(j

‑

1)

×

511+1

,v

(j

‑

1)

×

511+2

,

…

,v

j

×

511

},本发明中的并行ldpc编码器考虑同时计算2段校验位。

[0116]

步骤3.1将比特选择模块分成2组,每组包含14个。将b

ij

矩阵的第一列非零元素位置集合分别加载到对应的比特选择模块中,非零元素位置寄存器s也初始化为相同的值。

[0117]

步骤3.2将步骤2得到的移位后的信息序列分别送到相应的2组比特选择模块中,根据非零元素寄存器s来选择中的有效比特,每个比特选择模块在511个时钟周期内都可以得到共计511个信息向量,向量长度为d

ij

。

[0118]

步骤4.将比特选择模块的输出进行比特合并,一共需要2个比特合并模块,将每组

的14个比特选择模块输出拼接到一起。每一个比特合并模块在511个时钟周期之内可以得到共计511个信息向量,用来计算校验位v

j

(1≤j≤2),本实施例中使用的ldpc(7154,8176)码每段信息序列经过比特合并模块之后的长度为3522。

[0119]

步骤5.流水累加,得到校验位v。流水累加模块采用流水线方式完成累加,编码中采用的都是模二加法,所以一共需要3521个异或门,共需要个处理时钟。

[0120]

步骤6.编码输出。首先通过串并转换模块将串行校验信息转换为全并行数据模式,然后使用编码输出模块将信息位和校验位组合输出。

[0121]

综上所述,本发明针对准循环ldpc的编码过程,生成矩阵的非稀疏性导致信息序列与其直接相乘复杂度较高的问题,提出了一种简化实现方法,根据生成矩阵中非零元素位置,对信息序列先进行比特选择,然后再进行编码计算,能够有效避免无效信息比特的运算,减少编码计算所需的运算数,将比特异或运算所需的逻辑电路减少大约50%,从而显著降低编码器的整体硬件资源消耗。

[0122]

以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1