主从D触发器和包括主从D触发器的集成电路的制作方法

主从d触发器和包括主从d触发器的集成电路

技术领域

1.本公开内容涉及主从d触发器。

背景技术:

2.在各种电路中使用基于触发器的寄存器以用于存储状态。为了减少这样的电路的电流消耗,电路可以包括以下数据处理模式:在该数据处理模式下,电路执行其期望的功能。此外,这样的设备或电路可以包括所谓的数据保留模式或者睡眠或待机模式,在数据保留模式或者睡眠或待机模式下,设备的数据处理被中断。在数据保留模式下,通常应该仅允许低静态泄漏电流。此外,期望确保在从数据保留模式改变为数据处理模式之后,设备(例如,ic(集成电路))可以立即继续进行数据处理。另外,对于在这样的设备中使用的触发器,即使在数据保留模式下,也应保存存储在触发器中的状态。

3.可以使用附加电路来实现这样的功能,以例如用于在数据保留模式期间存储触发器的数据。然而,可以期望以尽可能小的附加成本(例如,就附加电路和芯片面积而言)提供这样的功能。

技术实现要素:

4.根据实施方式,提供了一种主从d触发器,该主从d触发器包括:主电路,其被配置成接收输入信号并且根据输入信号产生两个第一中间信号;传输电路,其连接至主电路,并且包括至少两个逻辑门和用于将时钟信号施加到多个门中的每个门的一个输入的时钟连接,其中,多个门被配置成根据第一中间信号和时钟信号提供两个第二中间信号;以及从电路,其连接至传输电路以从第二中间信号形成触发器的至少一个输出信号。从电路被配置成在第二中间信号具有在先前的状态对之后的预定状态对的情况下,维持由先前的状态对给出的至少一个输出信号,并且传输电路具有控制输入并被配置成响应于控制输入处的预定控制信号状态而生成具有预定状态对的第二中间信号。

附图说明

5.在附图中,贯穿不同的视图,相似的附图标记通常指代相同的部分。附图不一定按比例绘制,而是通常将重点放在说明本发明的原理上。在以下描述中,将参照以下附图描述各个方面,在附图中:

6.图1示出了包括具有多个寄存器的电路的数据处理设备。

7.图2示出了主从d触发器。

8.图3示出了根据实施方式的主从d触发器。

9.图4示出了说明相关信号随时间变化的表现的时序图。

10.图5示出了根据实施方式的主从d触发器。

具体实施方式

11.下面的详细描述参照附图,附图以说明的方式示出了可以实践本发明的本公开内容的具体细节和方面。在不脱离本发明的范围的情况下,可以利用其他方面并且可以进行结构、逻辑和电气改变。本公开内容的各个方面不一定相互排斥,因为本公开内容的一些方面可以与本公开内容的一个或更多个其他方面结合以形成新的方面。

12.图1示出了包括具有多个寄存器102的集成电路101的数据处理设备100。

13.电路101(即集成电路)可以例如包括寄存器102,作为数据处理元件(例如,微处理器或任何种类的微控制器)的寄存器、作为任何种类的控制或配置寄存器、用于存储数据处理设备100的(状态机的)状态等的寄存器。因此,电路101还可以包括实现电路105例如顺序电路和组合电路的逻辑。

14.数据处理设备100具有工作模式控制器106,工作模式控制器106可以在数据处理模式(正常模式)与数据保留模式或者睡眠或待机模式之间切换数据处理设备100(例如,电路101)的一部分,在数据保留模式或者睡眠或待机模式下,数据处理设备100的数据处理被中断以节省功耗。为此,工作模式控制器106具有至寄存器102和逻辑电路105(以及电路101和/或设备100的可能的其他部件)的信令连接103,工作模式控制器106可以利用该信令连接103传送(工作模式)控制信号以设置寄存器102和逻辑电路105的工作模式。

15.在许多应用中,期望在从数据保留模式改变为数据处理模式之后数据处理设备可以立即继续进行数据处理,并且期望寄存器在数据保留模式期间保存存储在其中的数据。

16.因此,每个寄存器102由多个触发器104形成,并且每个触发器104被配置成在数据保留模式期间维持其状态(即,存储在触发器中的逻辑状态),即在数据保留模式期间状态不应该丢失。

17.寄存器102例如由具有可隔离的输入接口(例如可隔离的数据输入以及时钟输入和复位输入)并且在数据保留模式或者睡眠模式或待机模式下具有数据保留的时钟沿控制的触发器104形成,在数据保留模式或者睡眠模式或待机模式下或者利用所述模式可以中断正常模式(数据处理模式),从而在数据保留模式下,集成电路101仅吸收非常低的静态泄漏电流。

18.如以上所提及的,还可能需要集成电路101应该能够在从数据保留模式转换为数据处理模式之后立即恢复数据处理。还期望具有可隔离输入接口的这样的寄存器102可以无缝地或以尽可能少的工作被结合到ic的现有设计过程和实现中。这尤其适用于针对数据处理模式与数据保留模式之间的转换要进行观察的相关寄存器的接口信号的时间特性。

19.为了满足数据保留模式的那些要求,通常期望首先以高阻抗可切换方式将尽可能多的集成在ic 101上的顺序电路和组合电路105(即组合逻辑和顺序逻辑)与电源电压(来自高(正)电源电位vdd或来自低电源电位(接地)vss)分开。然而,由于存储在寄存器102中的信息中的至少一部分应该保留在寄存器102中(即,保留在这些寄存器中),因此一定数量的这些寄存器102必须在数据保留模式下仍然连接至电源电压。在数据保留模式下这些寄存器102与ic 101的与电源电压断开连接的那些部分电隔离,否则不希望的且不可控的交叉电流将流过这些寄存器102的输入接口。

20.通常期望的另一状况是,对于数据处理模式与数据保留模式之间的转换,寄存器的时钟信号在即将更改为数据保留模式之前以及在恢复数据处理模式之后应立即具有布

204、反相器ivm 208和ndsq 207形成的锁存器保存该值,因为由于sq=0,nddm 205为dm提供值1,并且由于rq=1,ndmn 204用作dm的反相器。因此只要ck=1,则维持内部节点dm、mn、m、sq、rq、s和qn的该状态以及q的状态,并且数据输入dn对这些节点没有影响。

31.此外,认为在进入待机或数据保留模式之前时钟停止,这意味着在典型的ic实现中,所有受影响寄存器的时钟输入ck均保持为0,并且在恢复数据处理模式之后可能仅再次显示上升沿或值ck=1。这意味着在即将进入数据保留模式之前,由nds 203和ndqn 202形成的从锁存器由于ck=0并且因此rq=sq=1而与主锁存器隔离,并保存先前在ck=1的情况下采用的数据,而anrdn 201和(由于rq=sq=1)nddm 205、ndmn 204、ivm 208、ndsq 207和anrrq 206对数据输入d的可能变化做出反应。因此,如果提供数据输入d的(组合)逻辑门如数据保留模式下所预期的那样与电源电压断开连接,则所有这些数据输入d至少在较长的时间段内呈现未定义的值,这会在门anrdn201、nddm 205、ndmn 204、ivm 208、ndsq 207和anrrq 206中引起交叉电流。

32.根据各种实施方式,还通过将门anrdn 201、nddm 205、ndmn204和ivm 208与电源电压隔离以及引入附加控制信号isn以及用于隔离门anrrq 206和ndsq 207的输入信号ck、r、mn和m的附加晶体管功能来解决此问题。以下参照图3对此进行描述。

33.图3示出了根据实施方式的主从d触发器300。

34.类似于图2的主从d触发器200,主从d触发器300包括门anrdn301、ndqn 302、nds 303、ndmn 304、nddm 305、aondrq 306(对应于anrrq 206)、ndsq 307、ivm 308和ivq 309。

35.主从d触发器300与主从d触发器200之间的唯一区别与门ndsq207和anrrq 206有关:nand2门(即具有两个输入的nand门)ndsq207被扩展为具有用于控制信号isn的附加输入的nand3门ndsq 307(即具有三个输入的nand门),并且andnor门anrrq 206被扩展为具有用于控制信号isn的附加nand输入的andornand门aondrq 306。

36.对于isn=0,认为门ndsq 307和aondrq 306的输出sq和rq被设置为1,而与mn、m、ck和r的值无关。在isn=0的情况下,从mn、m、ck和r的值对通过触发器300的门ndsq 307和aondrq 306的电流没有影响的意义来说,节点sq和rq被隔离。

37.这意味着(如以上在图2的上下文中所描述的)对于r=ck=0,在rq=sq=1的情况下,可知由两个nand门ndqn 302和nds 303形成的sr触发器,即所谓的寄存器的从锁存器,保存先前通过具有上升沿的ck写入的值(象征性地:q=q(t

‑

1))或者通过有效复位信号r=1设置的值qn=1、s=0(由于sq=1)和q=0。

38.因此,对于数据保留,门ndsq 307和aondrq 306需要保持连接至较高电源电压vdd,而较低电源电压vss可以断开连接,并且门nds303和ndqn 302需要保持连接至两个电源电压vdd和vss两者以将数据留在从锁存器中。另一方面,输出反相器ivq 309可以与vss和/或vdd以及anrdn 301、nddm 305、ndmn 304和ivm 308断开连接。

39.这意味着在isn的值为0(其在整个数据保留模式下均稳定在该值)的情况下,生成时钟信号ck的时钟树和提供数据输入d、ti和te的(组合)逻辑门二者都可以如所预期的与电源电压断开连接,以最小化数据保留模式下的泄露电流,而不会丢失存储在触发器300的从锁存器中的信息。

40.图4示出了说明相关信号在时间上的行为的时序图400。首先,在系统级别(例如,设备100或电路101的级别)上,(例如,通过工作模式控制器106)确保在进入数据保留模式

之前,所有触发器104(假定具有图3的形式)的时钟输入ck停在零处(其可以被视为无效电平)。此外,(例如,通过工作模式控制器106)确保在进入数据保持模式之前r是无效的(即在图3所示的实现示例中等于0)。

41.因此,只要一方面从锁存器保持“在线”并且另一方面内部值rq和sq保持其值,则所涉及的每个触发器104都可以与其输入接口隔离,而不会丢失存储在触发器中的信息。内部值rq和sq保持其值是通过工作模式控制器106实现的,该工作模式控制器106在系统级别上激活isn信号,即利用isn的下降沿(并且贯穿数据保留模式isn的稳定值为0)。因此,rq=sq=1,这确保从锁存器不能更改为复位状态,并确保从锁存器保留已存储的数据。

42.在isn的下降沿之后,数据保留模式下不需要的ic 101的所有部分都与电源电压断开连接。工作模式控制器106通过在系统级别上去激活信号pw(即利用pw的下降沿并且贯穿数据保留模式pw的稳定值为0)来执行该操作。这又意味着寄存器的所有输入信号(isn除外)可以采用未定义的值(由时序图400中的交叉阴影线指示),而不会造成集成电路101的故障。

43.为了重新进入数据处理模式,工作模式控制器106首先在系统级别上激活pw,即,启动pw的上升沿。这意味着先前与电源电压断开连接的所有电路部分现在重新在线。结果是,在重新进入数据处理模式之后,所有触发器104的数据输入d、ti和te处的值再次是之前(即,在即将离开数据处理模式之前)在数据输入处存在的那些值。其原因是,数据输入d处的值是由寄存器输出值q的布尔组合产生的。然而,所有q仍具有其旧值(因为假定所有相关寄存器均未与电源断开连接)。在达到稳定值d之后,然后可以利用isn的上升沿来取消触发器104的“隔离”,因为现在寄存器输入ck和r已经恢复了其在即将离开数据处理模式之前已经具有的值(二者均回到到0)。因此,所有寄存器都准备好再次进行工作,并且通过所有寄存器整个ic准备好再次进行工作。

44.因此,主从d触发器300在数据保留模式下实际上完全允许禁用触发器外部的时钟和复位树。由于这些驱动器级(其主要由快速反相器构成)吸收了特别大量的泄漏电流,因此将其关断实现泄漏电流的显著降低。相比之下,isn(和pw)的(很少的)驱动器不必很强,从而产生低泄漏电流。

45.图3的示例是具有扫描和复位功能的触发器。应当注意,实施方式不限于这种情况,并且隔离输入信号的原理也可以应用于具有置位输入、没有复位输入并且没有扫描功能等的触发器。

46.总之,根据各种实施方式,如图5所示,提供了主从d触发器。

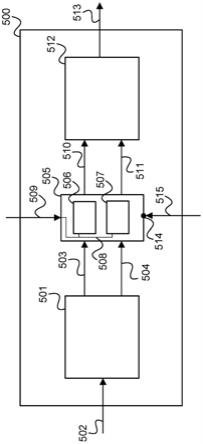

47.图5示出了根据实施方式的主从d触发器500。

48.主从d触发器500包括主电路501(例如主锁存器),主电路501被配置成接收输入信号502并根据输入信号502产生两个第一中间信号503、504。

49.主从d触发器500还包括传输电路505,传输电路505连接至主电路501,并且包括至少两个逻辑门506、507和用于将时钟信号509施加到门506、507中的每个门的一个输入的时钟连接508,其中,门506、507被配置成根据第一中间信号503、504和时钟信号509提供两个第二中间信号510、511。

50.此外,主从d触发器500包括从电路(例如,从锁存器)512,从电路512连接至传输电路505,以从第二中间信号510、511形成触发器500的至少一个输出信号513。

51.从电路512被配置成在第二中间信号510、511具有在先前的状态对之后的预定状态对的情况下,维持由先前的状态对给出(即,由先前的状态对形成)的至少一个输出信号513。

52.传输电路505具有控制输入514,并且被配置成响应于控制输入514处的(控制信号515的)预定控制信号状态而生成具有预定状态对的第二中间信号510、511。

53.根据各个实施方式,换句话说,主从触发器设置有控制输入,该控制输入在有效时将从锁存器的输入切换到使从锁存器维持其当前状态(即由至从锁存器的先前输入即第二中间信号的先前状态对给出的状态)的状态(即第二中间信号的预定状态对)。对于从锁存器为rs触发器的情况,rs触发器的这个输入可以是将其置位输入和复位输入二者均设置为无效。在图3的示例中,这对应于rq和sq二者都等于1,这是isn=0的情况。

54.主电路、传输电路和从电路各自由一个或更多个门例如nand门、或非(nor)门复合门(如上述示例中的andornand)和反相器形成。

55.例如,从电路512由ndqn 302和nds 303形成,主电路由ndmn304、nddm 305和ivm 308形成,并且传输电路由aondrq 306和ndsq 307形成。因此,在图3的示例中,第一中间信号是m和mn,并且第二中间信号是rq和sq。控制信号对应于isn,并且预定控制信号状态对应于isn=0。

56.d触发器也被称为“数据”或“延迟”触发器。d触发器在时钟周期的限定部分(例如时钟的上升沿)处捕获d输入的值。该捕获的值成为q输出。d触发器可以被看作存储单元、零阶保持或延迟线。

57.以下描述了各种示例:

58.示例1是参照图5描述的主从d触发器。

59.示例2是根据示例1的主从d触发器,其中,第二中间信号被反馈回主电路的输入。

60.示例3是根据示例1或2的主从d触发器,其中,传输电路的第一门的另一输入连接至主电路以直接接收由主电路提供的第一中间信号中的一个第一中间信号,并且传输电路的第二门的另一输入连接至主电路以接收该第一中间信号的补码。

61.示例4是根据示例1至3中任一项的主从d触发器,其中,传输电路的门均不具有连接至传输电路的门中的任何其他门的输入的输出。

62.示例5是根据示例1至4中任一项的主从d触发器,其中,传输电路连接至主电路,使得第二中间信号被馈送到主电路,并且主电路被配置成根据第二中间信号产生第一中间信号。

63.示例6是根据示例1至5中任一项的主从d触发器,其中,从电路由sr锁存器形成。

64.示例7是根据示例1至6中任一项的主从d触发器,其中,从电路由交叉耦接的与非门的sr锁存器形成,或者由交叉耦接的或非门的sr锁存器形成。

65.示例8是根据示例6或7的主从d触发器,其中,两个第二中间信号分别被提供给从锁存器的r输入和s输入。

66.示例9是根据示例6至8中任一项的主从d触发器,其中,预定状态对是从锁存器的置位输入和复位输入二者均被设置为无效。

67.示例10是根据示例1至9中任一项的主从d触发器,其中,传输电路的每个门被配置成通过控制输入处的状态与门的一个或更多个其他输入处的状态的组合的与组合来生成

第二中间信号中的相应第二中间信号。

68.示例11是根据示例1至10中任一项的主从d触发器,其中,预定控制信号状态是数据保留模式的激活状态。

69.示例12是根据示例1至11中任一项的主从d触发器,其中,第一中间信号是互补信号对,并且第二中间信号是互补信号对。

70.示例13是包括多个寄存器的集成电路,每个寄存器包括根据示例1至示例12中的任一项的多个触发器。

71.示例14是示例13的集成电路,包括工作模式控制器,工作模式控制器被配置成将触发器的控制输入设置成预定控制信号状态以进入数据保留模式。

72.示例15是示例13或14的集成电路,其中,每个触发器包括提供有复位信号和/或置位信号的复位输入和/或置位输入以及提供有时钟信号的时钟输入,并且工作模式控制器被配置成将触发器的控制输入设置成预定控制信号状态,以在复位信号和/或置位信号和时钟信号已经被设置成无效电平之后进入数据保留模式。

73.尽管本文已经说明和描述了特定实施方式,但本领域的技术人员将理解,可以在不脱离本发明的范围的情况下用各种替选实现方式和/或等效实现方式来替代所示出并且描述的特定实施方式。本技术意在覆盖本文讨论的特定实施方式的任何改变或变型。因此,本发明旨在仅由其权利要求书及其等同物限制。

74.附图标记

75.100 数据处理设备

76.101 集成电路

77.102 寄存器

78.103 信令连接

79.104 触发器

80.105 逻辑电路系统

81.106 操作模式控制器

82.201 anrdn门

83.202 ndqn门

84.203 nds门

85.204 ndmn门

86.205 nddm门

87.206 anrrq门

88.207 ndsq门

89.208 ivm门

90.209 ivq门

91.301 anrdn门

92.302 ndqn门

93.303 nds门

94.304 ndmn门

95.305 nddm门

96.306 aondrq门

97.307 ndsq门

98.308 ivm门

99.309 ivq门

100.400 时序图

101.500 主从d触发器

102.501 主电路

103.502 输入信号

104.503、504 第一中间信号

105.505 传输电路

106.506、507 逻辑门

107.508 时钟连接

108.509 时钟信号

109.510、511 第二中间信号

110.512 从电路

111.513 输出信号

112.514 控制输入

113.515 控制信号

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1