电流源驱动电路、模数转换器及接收机的制作方法

1.本说明书实施例涉及电子电路技术领域,尤其涉及一种电流源驱动电路、模数转换器及接收机。

背景技术:

2.接收机基于结构的不同可以分为超外差结构、零中频结构和低中频结构。目前常用的是零中频接收机和低中频接收机,零中频接收机和低中频接收机各有优缺点。其中wifi通信通常使用零中频接收机,蓝牙(bluetooth)或者一些窄带通信通常使用低中频接收机。

3.参照图1所示的一种低中频接收机的结构示意图,可以应用于蓝牙/低功耗蓝牙(bt/ble)模块中,其中,低中频接收机10可以由低噪声放大器(low-noise amplifier,lna)、跨导(gm)、混频器(mixer)、跨阻放大器(tia)及复数滤波器(complex filter)1a和模数转换器(analog-to-digital converter,adc)组成,低中频接收机10可以与物理层(phy)耦接,射频信号经天线接收后,经过lna放大,经解调后得到两路正交信号:同相(in-phase,i)路输入信号及正交(quadrature)路输入信号。对于i路及q路输入信号,分别通过gm将电压输入信号转换为电流输出信号,通过混频器将电流形式的射频信号先下变频到低中频,并由tia将下变频后的电流信号转换为电压输出信号,由复数滤波器1a滤除带外噪声信号及干扰,接着由adc将接收到的模拟信号转换为数字信号,并输出至phy进行信号的调制解调及其他处理。其中,adc一般有两种实现方式,一种是逐次逼近型模数转换器(successive approximation analog-to-digital converter,sar adc),另一种是σ-δ(sigma-delta,sd)调制型adc,综合考虑功耗和复杂度,常选用sar adc。

4.随着物联网(the internet of things,iot)、真正无线立体声(true wireless stereo,tws)等应用的兴起,对bt/blt产品的功耗提出了更高的要求。为了降低功耗,常对图1所示结构的低中频接收机进行改进。如图2所示的另一种低中频接收机的结构示意图,与图1不同之处在于,可以将图1中的复数滤波器1a和sar adc用复数连续时间sdadc(complex ct sdadc)2a实现,能够节省复数滤波器1a。

5.虽然使用复数连续时间sdadc能够降低系统功耗,然而同相正交(in-phase quadrature,iq)两路的失配是一个比较严重的问题,失配会在负频率处产生一个和信号对应的镜像信号,进而会降低系统解调性能。在iq两路的所有失配中,用于反馈的模数转换器(digital-to-analog converter,dac)的失配影响占比最大。

6.为解决iq两路的失配问题,可以进一步对电路进行优化设计,其中,常用的消除iq两路反馈dac失配的方式是按照一定的规律,交换iq两路的dac电流源。

7.多比特反馈dac在低功耗sd adc设计时十分常用,多比特dac本身的失配也是一个严重的问题,致使调制器的性能严重下降。因此对于i路或者q路本身的dac,也是需要按照一定的要求随机选择dac单元,从而将失配打散成噪声,然后通过噪声整形推到高频处,达到提升调整器性能的效果。因此除了iq两路的dac需要交换之外,i路和q路本身的dac单元

之间也需要切换。电流舵dac是常见的dac实现方式之一。

8.然而,上述实现方式存在的一个问题是,难以保证在任何输入下和每一个电流源连接的开关都不同时关闭,因此可能导致电流源需要重新建立,进而导致复数连续时间sdadc的性能下降。

技术实现要素:

9.有鉴于此,本说明书实施例提供了一种电流源驱动电路、模数转换器及接收机,能够实现在任何情况下电流源均无须重新建立,提高电流源驱动电路的稳定性,进而可以提高应用其的模数转换器和接收机的性能。

10.首先,本说明书实施例提供了一种电流源驱动电路,适于驱动电流源,所述电流源驱动电路包括:

11.锁存电路模块,适于基于第一路输入信号,输出第一锁存信号和第一锁存反相信号,基于第二路输入信号,输出第二锁存信号和第二锁存反相信号;

12.差分互补电路模块,包括:互补的两个开关组子模块,其中:任一开关组子模块分别与第一电流源支路和第二电流源支路中其中一路电流源支路耦接,所述开关组子模块包括耦接的多个开关;

13.驱动电路模块,分别与所述锁存电路模块和所述差分互补电路模块耦接,适于基于所述第一锁存信号、所述第一锁存反相信号、所述第二锁存信号和所述第二锁存反相信号,输出多路开关控制信号至所述差分互补电路模块的开关组子模块,使得任一时刻所述任一电流源支路对应的开关组子模块中均有开关处于导通状态,以驱动相应电流源支路中的电流源。

14.本说明书实施例还提供了一种模数转换器,包括:第一输入通路、第二输入通路和反馈通路,其中:

15.所述第一输入通路,适于基于第一输入信号和所述反馈通路输出的第一反馈信号,得到第一路输出信号;

16.所述第二输入通路,适于基于第二输入信号和所述反馈通路输出的第二反馈信号,得到第二路输出信号;

17.所述反馈通路,与所述第一输入通路和第二输入通路分别耦接,包括:

18.第一电流源支路;

19.第二电流源支路;

20.本说明书任一实施例所述的电流源驱动电路,其第一输入端与所述第一输入通路的输出端耦接,将所述第一输入通路所输出的第一路输出信号作为反馈通路的第一路输入信号;其第二输入端与所述第二输入通路的输出端耦接,将所述第二输入通路所输出的第二路输出信号作为反馈通路的第二路输入信号,基于所述第一路输入信号和所述第二路输入信号,导通第一反馈通路数模转换器和所述第一电流源支路,以及导通所述第二反馈通路数模转换器和所述第二电流源支路;

21.反馈通路数模转换装置,适于基于所述电流源驱动电路的开关控制,输出所述第一反馈信号至所述第一输入通路,以及输出所述第二反馈信号至所述第二输入通路。

22.本说明书实施例还提供了一种接收机,包括:

23.解调装置,适于对射频输入信号进行解调处理,得到同相正交的第一输入信号和第二输入信号;

24.本说明书任一实施例所述的模数转换器,适于对所述第一输入信号和所述第二输入信号进行模数转换,得到第一通路输出信号和第二通路输出信号。

25.采用本说明书实施例提供的电流源驱动电路,所述电流源驱动电路包括锁存电路模块、驱动电路模块和差分互补电路模块,其中,所述差分互补电路模块包括互补的两个开关组子模块,任一开关组子模块分别与第一电流源支路和第二电流源支路中其中一路电流源支路耦接,所述开关组子模块包括耦接的多个开关,通过锁存电路模块基于第一路输入信号,输出第一锁存信号和第一锁存反相信号,及基于第二路输入信号,输出第二锁存信号和第二锁存反相信号,进而由驱动电路模块基于所述第一锁存信号、所述第一锁存反相信号、所述第二锁存信号和所述第二锁存反相信号,输出多路开关信号至差分互补电路模块的开关组子模块,使得任一时刻所述任一电流源支路对应的开关组子模块中均有开关处于导通状态,以驱动相应电流源支路中的电流源,换言之,所有与电流源相连的开关均不会同时关闭,因此,在任何情况下电流源均无须重新建立,进而可以提高应用其的模数转换器及接收机的性能。

26.进一步地,所述驱动电路模块包括逻辑控制子模块,以及分别与所述逻辑控制子模块耦接且结构相同的两个互不交叠时钟子模块,其中,通过所述逻辑控制子模块基于所述第一锁存信号和所述第二锁存信号,进行预设的逻辑运算,输出第一控制信号和第二控制信号,进而由所述两个互不交叠时钟子模块,分别基于输入的所述第一锁存信号、所述第一锁存反相信号、所述第一控制信号和所述第二控制信号,输出多路开关控制信号至相应的开关组子模块,因此通过控制所述逻辑控制子模块的运算逻辑,能够使所述两个互不交叠时钟子模块在任一时刻均有开关处于导通状态,因此可以使所述第一电流源支路和所述第二电流源支路中总有电流源处于导通状态,使得任何情况下电流源均无须重新建立,对于应用本说明书实施例中的电流源驱动电路模数转换器,通过所述电流源驱动电路驱动电流源,由于所述第一电流源支路和所述第二电流源支路中总有电流源处于导通状态,因此在通过交换所述模数转换器的反馈通路中的第一电流源和第二电流源来消除所述模数转换器失配过程中,可以避免电流源重建,因此可以提高所述模数转换器及应用其的接收机的性能。

27.进一步地,由于所述任一电流源支路均包括耦接于电源和地之间的流向相反的第一电流源和第二电流源,所述电流源支路均包括电流流向相反的两个输出端,所述开关组子模块包括耦接于相应电流源支路上的所述第一电流源和所述第二电流源之间的控制开关,因此在任一时刻,对于任一电流源支路,均可以实现电流流向的双向切换。

28.进一步地,所述逻辑控制子模块包括依次耦接的异或门单元、第一延时单元和第二延时单元,其中,所述异或门单元,其第一输入端适于输入所述第一锁存信号,其第二输入端适于输入所述第二锁存信号,其输出端分别与所述第一延时单元的输入端和所述第二延时单元的第一输入端耦接,所述第一延时单元的输出端适于输出所述第一控制信号,所述第二延时单元的输出端适于输出所述第二控制信号,且所述第二延时单元的延时时长小于所述第一延时单元的延时时长,由于所述第一控制信号与所述第二控制信号具有所述第二延时单元的延时时长,因而由所述第一控制信号和所述第二控制信号控制所述两个互不

交叠时钟子模块,可以使相应电流源支路的开关组子模块中在任一时刻均有开关处于导通状态,导通与之耦接的电流源。

29.进一步地,所述互不交叠时钟子模块包括两个结构相同且相互耦合的互不交叠时钟单元,其中,任一互不交叠时钟单元包括第三延时单元、第二与非门单元、第一或非门单元和第四非门,一方面,通过所述第一控制信号和所述第三延时单元的输出信号输入所述第二与非门单元,由所述第二与非门单元的输出端输出对应的开关控制信号控制与其耦接的电流源支路的控制开关的通断;另一方面,由所述第二控制信号和所述第三延时单元的输出信号输入所述第一或非门单元,并由所述第一或非门单元与所述第四非门耦接,由所述第四非门向与其耦接的控制开关输出开关控制信号控制与其耦接的电流源支路的控制开关的通断,这样,任一时刻所述第一电流源支路和所述第二电流源支路中均有与所述互不交叠时钟子模块耦接的开关处于导通状态,导通相应的电流源,从而可以避免模数转换器在所述第一路输入信号和所述第二路输入信号交换过程中出现电流源重建的情况。

30.进一步地,在所述第一电流源支路和第二电流源支路分别包括流向相反的第一电流源和第二电流源,所述电流源支路均包括电流流向相反的两个输出端时,所述互不交叠时钟单元还包括第五非门和第六非门,其中,所述第五非门与所述第二与非门的输出端耦接,所述第六非门与所述第四非门的输出端耦接,通过所述互不交叠时钟单元分别向耦接于相应的电流源支路的电流源和电流源支路输出端之间的控制开关输出控制信号,可以控制相应电流源支路中电流源的通断及流向,使得在模数转换器的第一路输入信号和所述第二路输入信号交换过程中,所述第一电流源支路和所述第二电流源支路也均有电流源处于导通状态,从而可以避免进行电流源重建。

31.进一步地,所述第三延时单元包括依次耦接的与门、第四延时单元和第七非门,其中所述第七非门的输出端作为所述第一延时单元的第一输出端,所述第四延时单元的输出端作为所述第三延时单元的输出端,使得所述互不交叠时钟单元中的第二与非门单元和所述第四非门输出的开关控制信号的时序更加同步,使得任一时刻与一个电流源耦接的开关组子模块中至少有一个开关处于导通状态。

32.进一步地,通过设置所述第一延时单元的延时时长大于所述第四延时单元的延时时长,并可以根据实际应用调节所述第一延时单元和第四延时单元的延时时间,可以获得不同的导通交叠时间。

33.进一步地,驱动电路中延时的相对时长仅取决于逻辑门的个数,从而不易受电压、温度和工艺角的影响,具有更好的鲁棒性。

34.进一步地,通过分别与所述第一延时单元和所述第四延时单元耦接的时延校准模块,初始设置所述第四延时单元的延时时长为固定值,且所述第一延时单元的延时调节步长为总调节步长的1/2n,并将预设的测试时钟信号输入所述时延校准模块,使所述第一延时单元进行累积计数,直至所述时延校准模块的输出满足预设条件时所述第一延时单元对应的时长作为所述电流源驱动电路中所述第一延时单元的延时时长,可以使所述第一延时单元和所述第四延时单元的延时时长之差的绝对值最小,从而可以减小整个电流源驱动电路的时延。

附图说明

35.为了更清楚地说明本说明书实施例的技术方案,下面将对本说明书实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面所描述的附图仅仅是本说明书的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

36.图1示出了一种低中频接收机的结构示意图;

37.图2示出了另一种低中频接收机的结构示意图;

38.图3示出了一种复数连续时间sdadc的结构示意图;

39.图4示出了本说明书实施例中一种电流源驱动电路的结构示意图;

40.图5示出了本说明书实施例中一种锁存电路模块的结构示意图;

41.图6示出了本说明书实施例中一种电流源驱动电路的各模块之间的连接关系示意图;

42.图7示出了本说明书实施例中一种差分互补电路模块的结构示意图;

43.图8示出了本说明书实施例中一种驱动电路模块的结构示意图;

44.图9a-图9d示出了本说明书实施例中输入信号切换过程与相应的开关组子模块的开关控制信号的波形图;

45.图10示出了本说明书实施例中一种时延校准模块的结构示意图;

46.图11示出了本说明书实施例中一种图10所示的时延校准模块对应的自动校准流程图;

47.图12示出了本说明书实施例中一种模数转换器的结构示意图;

48.图13示出了本说明书实施例中另一种模数转换器的结构示意图;

49.图14示出了本说明书实施例中一种接收机的结构示意图。

具体实施方式

50.如背景技术所述,目前复数连续时间sdadc的iq两路的失配问题是一个比较严重的问题,失配会在负频率处产生一个和信号对应的镜像信号,进而会降低系统解调性能。在iq两路的所有失配中,用于反馈的dac的失配的影响占比最大。

51.图3示出了一种复数连续时间sdadc的结构示意图,其中,sdadc 30包括同相信号输入通路31、正交信号输入通路32和反馈通路33,其中:

52.所述同相信号输入通路31,适于基于第一输入信号ini和所述反馈通路输出的第一反馈信号i,得到第一路输出信号outi;

53.所述正交信号输入通路32,适于基于第二输入信号inq和所述反馈通路输出的第二反馈信号q,得到第二路输出信号outq;

54.更具体地,所述同相输入通路31和正交信号输入通路32均包括加法器、滤波器和量化器,其中:

55.在同相信号输入通路31,由加法器对第一输入信号ini和反馈通路反馈的第一反馈信号i进行累加,由滤波器在环路中,和其他模块一起,进行滤波,消除量化噪声;由量化器将滤波器输出的连续信号量化成离散信号,完成模数转换的基本功能。

56.所述反馈通路33,与所述同相信号输入通路31和正交信号输入通路32分别耦接,

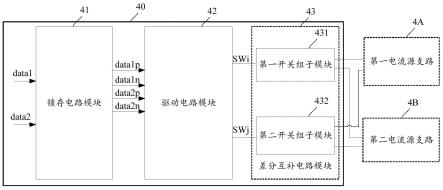

包括数据加权平均(data weighted averaging,dwa)模块、驱动电路和i路和q路共用的反馈数模转换装置daci+dacq,其中:

57.所述dwa模块,主要将量化器输出的数字信号进行一定的变换后输送至所述daci+dacq,所述反馈数模转换装置daci+dacq在驱动电路的控制下,分别向所述同相信号输入通路31反馈第一反馈信号i,向所述正交信号输入通路32反馈第二反馈信号q。

58.常用的消除iq两路反馈dac失配的方式是按照一定的规律交换iq两路的dac电流源(未示出),一种具体做法是当iq两路反馈dac输入信号相同时,交换iq两路电流源,iq两路反馈输入信号不同时,则不交换iq两路的电流源。

59.多比特反馈dac在低功耗sd adc设计时十分常用,多比特dac本身的失配也是一个严重的问题,致使调制器的性能严重下降。因此对于i路或者q路本身的dac,也是需要按照一定的要求随机选择dac单元,从而达到将失配打散成噪声,然后通过噪声整形推到高频处。因此除了iq两路的dac需要交换之外,i路和q路本身的dac单元之间也需要切换。电流舵dac是常见的dac实现方式之一。

60.然而,上述实现方式带来一个问题是,iq两路电流源本身的开关和交换电流源的开关,会增加开关的个数,同时难以保证在任何输入下和每一个电流源连接的开关都不会同时关闭,导致电流源需要重新建立,进而导致复数连续时间sdadc的解调性能下降。

61.为实现在任何情况下电流源均无须重新建立,提高电流源驱动电路的稳定性,进而提高adc的性能,本说明书实施例提供一种电流源驱动电路,其中包括依次耦接的锁存电路模块、驱动电路模块和差分互补电路模块,其中所述差分互补电路模块包括互补的两个开关组子模块,任一开关组子模块分别与第一电流源支路和第二电流源支路中其中一路电流源支路耦接,所述开关组子模块包括耦接的多个开关,通过锁存电路模块基于第一路输入信号,输出第一锁存信号和第一锁存反相信号,及基于第二路输入信号,输出第二锁存信号和第二锁存反相信号,进而由驱动电路模块基于所述第一锁存信号、所述第一锁存反相信号、所述第二锁存信号和所述第二锁存反相信号,输出多路开关信号至差分互补电路模块的开关组子模块,使得任一时刻所述任一电流源支路对应的开关组子模块中均有开关处于导通状态,以驱动相应电流源支路中的电流源,换言之,所有与电流源相连的开关均不会同时关闭,因此,在任何情况下电流源均无须重新建立,进而可以提高应用其的模数转换器及接收机的性能。

62.为使本领域技术人员更好地理解和实施本说明书实施例,以下参照附图,并结合具体的应用电路,详细介绍其实现原理。

63.参照图4所示的电流源驱动电路的结构示意图,在本说明书实施例中,如图4所示,电流源驱动电路40适于驱动电流源,更具体地,可以分别驱动所述第一电流源支路4a和所述第二电流源支路4b上的电流源,所述电流源驱动电路40可以包括:锁存电路模块41、差分互补电路模块43和驱动电路模块42,其中:

64.所述锁存电路模块41,适于基于第一路输入信号data1,输出第一锁存信号data1p和第一锁存反相信号data1n,基于第二路输入信号data2,输出第二锁存信号data2p和第二锁存反相信号data2n;

65.差分互补电路模块43,包括:互补的两个开关组子模块(例如第一开关组子模块431和第二开关组子模块432),其中:任一开关组子模块分别与第一电流源支路4a和第二电

流源支路4b中其中一路电流源支路耦接,所述开关组子模块包括耦接的多个开关;

66.驱动电路模块42,分别与所述锁存电路模块41和所述差分互补电路模块43耦接,适于基于所述第一锁存信号data1p、所述第一锁存反相信号data1n、所述第二锁存信号data2p和所述第二锁存反相信号data2n,输出多路开关控制信号(例如多路开关控制信号swi、swj)至所述差分互补电路模块43的开关组子模块例如第一开关组子模块431和第二开关组子模块432),使得任一时刻所述任一电流源支路(例如所述第一电流源支路4a和所述第二电流源支路4b)对应的开关组子模块中均有开关处于导通状态,以驱动相应电流源支路(例如所述第一电流源支路4a或所述第二电流源支路4b)中的电流源。

67.采用上述电流源驱动电路,通过锁存模块41基于所述第一路输入信号data1和第二路输入信号data2,输出所述第一锁存信号data1p、所述第一锁存反相信号data1n、所述第二锁存信data2p和所述第二锁存反相信号data2n,并由所述驱动电路模块42基于所述第一锁存信号data1p、所述第一锁存反相信号data1n、所述第二锁存信号data2p和所述第二锁存反相信号data2n,输出多路开关控制信号至所述差分互补电路模块43中的开关组子模块,由于所述差分互补电路模块43中的互补的两个开关组子模块中的任一开关组子模块分别与所述第一电流源支路和所述第二电流源支路中其中一路电流源支路耦接,所述开关组子模块包括耦接的多个开关,因此不论所述第一路输入信号data1和所述第二路输入信号data2相同、相异、或者所述第一路输入信data1和所述第二路输入信号data2在切换过程中,通过所述驱动电路模块42与所述锁存电路模块41和所述差分互补电路模块43配合,均可以使所述第一电流源支路和所述第二电流源支路对应的开关组子模块中均有开关处于导通状态,也即在任何时刻,在所述第一路输入信号和所述第二路输入信号为任何信号的情况下,所述电流源驱动电路40所驱动的任一个电流源支路上的电流源均不会关闭,因而可以避免电流源重新建立,从而可以增强应用其的adc的性能。

68.为使本领域技术人员更好地理解和实施,以下示出一些能够实现任一时刻所述任一电流源支路对应的开关组子模块中均有开关处于导通状态,以驱动相应电流源支路中的电流源的具体电路结构。以下分别对锁存电路模块、差分互补电路模块和驱动电路模块的电路结构进行示例说明。

69.在具体实施中,所述锁存电路模块可以包括:两个结构相同的锁存子模块,其中任一锁存子模块,其输入端适于输入所述第一路输入信号或所述第二路输入信号,其第一输出端适于输出与相应路的输入信号同相的锁存信号,其第二输出端适于输出与相应路的输入信号反相的锁存反相信号。

70.在本说明书一具体示例中,所述锁存子模块包括:依次耦接的第一非门、第二非门和锁存器,其中:所述锁存器的第一输入端与所述第一非门的输出端耦接,所述锁存器的第二输入端与所述第二非门的输出端耦接,所述锁存器的第一输出端适于输出所述相应路的锁存信号,所述锁存器的第二输出端适于输出所述相应路的锁存反相信号。

71.参照图5所示的一种锁存电路模块的电路结构示意图,锁存电路模块50包括:两个结构相同的第一锁存子模块51和第二锁存子模块52,其中:

72.所述第一锁存子模块51包括:依次耦接的第一非门not11、第二非门not12和第一锁存器51a,其中:所述第一非门not11基于所述第一路输入信号data1,延时反相输出第一延时反相信号m;所述第二非门not12基于所述第一延时反相信号m,延时反相输出第二延时

反相信号n;所述第一锁存器51a的第一输入端与所述第一非门not11的输出端耦接,所述第一锁存器51a的第二输入端与所述第二非门not12的输出端耦接,所述第一锁存器51a的第一输出端适于输出所述相应路的锁存信号,即第一锁存信号data1p,所述第一锁存器51a的第二输出端适于输出所述相应路的锁存反相信号,即第一锁存反相信号data1n。

73.作为一具体示例,所述第一锁存器51a具体可以包括:第一pmos晶体管pm1、第二pmos晶体管pm2、第一nmos晶体管nm1、第二nmos晶体管nm2、第三nmos晶体管nm4和第四nmos晶体管nm4,其中:所述第三nmos晶体管的栅极作为所述第一锁存器51a的第一输入端,适于输入所述第一延时反相信号m;所述第四nmos晶体管nm4的栅极作为所述第一锁存器51a的第二输入端,适于输入所述第二延时反相信号n;所述第一pmos晶体管pm1的源极和所述第二pmos晶体管pm2的源极均与电源vcc耦接;所述第一nmos晶体管nm1、所述第二nmos晶体管nm2、所述第三nmos晶体管nm3和所述第四nmos晶体管nm4的漏极均与地耦接;所述第一nmos晶体管nm1的源极、所述第三nmos晶体管nm3的源极和所述第一pmos晶体管pm1的漏极以及所述第二nmos晶体管nm2的栅极和所述第二pmos晶体管pm2的栅极交叉耦合,并适于输出所述第一锁存信号data1p;所述第二nmos晶体管nm2的源极、所述第四nmos晶体管nm4的源极和所述第二pmos晶体管pm2的漏极以及所述第一nmos晶体管nm1的栅极和所述第一pmos晶体管pm1的栅极交叉耦合,并适于输出所述第一锁存反相信号data1n。

74.类似地,所述第二锁存子模块52可以包括与第一锁存子模块51相同的结构电路。作为一具体示例,所述第二锁存子模块52可以包括:依次耦接的第三非门not21、第四非门not22和第二锁存器52a,其中:所述第三非门not21基于所述第二路输入信号data2,延时反相输出第三延时反相信号x;所述第四非门not22基于所述第三延时反相信号x,延时反相输出第四延时反相信号y;所述第二锁存器52a的第一输入端与所述第三非门not21的输出端耦接,适于输入所述第三延时反相信号x,所述第二锁存器52a的第二输入端与所述第四非门not22的输出端耦接,适于输入所述第四延时反相信号y,所述第二锁存器52a的第一输出端适于输出所述相应路的锁存信号,即第二锁存信号data2p,所述第二锁存器52a的第二输出端适于输出所述相应路的锁存反相信号,即第二锁存反相信号data2n。

75.继续参照图5,所述第二锁存器52a可以具有与第一锁存器51a相同的结构,作为一具体示例,所述第二锁存器52a可以包括:第三pmos晶体管pm3、第四pmos晶体管pm4、第五nmos晶体管nm5、第六nmos晶体管nm6、第七nmos晶体管nm7和第八nmos晶体管nm8,其中:所述第七nmos晶体管的栅极适于输入所述第三延时反相信号x;所述第八nmos晶体管nm8的栅极适于输入所述第四延时反相信号y;所述第三pmos晶体管pm3的源极和所述第四pmos晶体管pm4的源极均与电源vcc耦接;所述第五nmos晶体管nm5、所述第六nmos晶体管nm6、所述第七nmos晶体管nm7和所述第八nmos晶体管nm8的漏极均与地耦接;所述第五nmos晶体管nm5的源极、所述第七nmos晶体管nm7的源极和所述第三pmos晶体管pm3的漏极以及所述第六nmos晶体管nm6的栅极和所述第四pmos晶体管pm4的栅极交叉耦合,并适于输出所述第二锁存信号data2p;所述第六nmos晶体管nm6的源极、所述第八nmos晶体管nm8的源极和所述第四pmos晶体管pm4的漏极以及所述第五nmos晶体管nm5的栅极和所述第七pmos晶体管pm7的栅极交叉耦合,并适于输出所述第二锁存反相信号data2n。

76.采用上述锁存电路模块,基于输入信号data1和data2,分别生成中间节点信号m、n、x和y,并基于所述中间节点信号m、n、x和y,得到输出信号:data1p、data1n、data2p和

data2n。采用上述结构的锁存电路模块,由于所述第一非门not11、第二非门not12、第三非门not21和第四非门not22,以及所述第一锁存器51a和所述第二锁存器52a均为最基本的电路单元,因此可以降低所述第一锁存信号data1p和第一锁存反相信号data1n边沿的延时,以及所述第二锁存信号data2p和第二锁存反相信号data2n边沿的延时,从而可以进一步提高在所述第一路输入信号data1和所述第二路输入信号data2切换过程中的切换性能,提高切换效率。

77.在具体实施中,所述第一锁存器51a和所述第二锁存器52a还可以采用其他结构的锁存器,只要能够基于所述第一延时反相信号m和所述第二延时反相信号n,输出同步反相的所述第一锁存信号data1p和所述第一锁存反相信号data1n,以及基于所述第三延时反相信号x和所述第四延时反相信号y,输出同步反相的所述第二锁存信号data2p和所述第二锁存反相信号data2n即可。

78.可以理解的是,所述锁存电路模块还可以为其他形式的锁存结构。在本说明书一具体实施例中,所述锁存电路模块中两个结构相同的锁存子模块,可以仅由两个串联的非门组成。具体而言,参照图5,第一锁存子模块51可以仅包括:依次串联的所述第一非门not11和所述第二非门not12;第二锁存子模块52可以仅包括:依次串联的所述第三非门not21和所述第四非门not22。在本实施例中,可以直接将所述第一非门not11的输出信号m作为第一锁存反相信号data1n,将所述第二非门not12的输出信号n作为所述第一锁存信号data1p;以及直接将所述第三非门not21的输出信号x作为第二锁存反相信号data2n,将所述第四非门not22的输出信号y作为所述第二锁存信号data2p。在具体实施中,可以在后续的驱动电路模块中调整所述第一锁存信号data1p、第一锁存反相信号data1n、第二锁存信号data2p和所述第二锁存反相信号data2n的时序,使得四者的时序保持同步即可。

79.为使本领域技术人员更好地理解和实施本说明书实施例中通过使任一时刻任一电流源支路对应的开关组子模块中均有开关处于导通状态,来驱动相应电流源支路中的电流源,避免电流源重建的一些示例方案。

80.图6示出了一种电流源驱动电路中各个模块的连接关系示意图,图7示出了一种差分互补电路模块的结构示意图,图8示出了一种驱动电路模块的结构示意图,以下结合图6至图8详细说明所述电流源驱动电路的驱动原理。

81.在本说明书一些实施例中,差分互补电路模块可以为全差分互补电路模块,也可以为半差分互补电路模块。如图7所示的一种全差分互补电路模块,其中,全差分互补电路70分别与第一电流源支路和第二电流源支路耦接,形成全差分互补电流源。其中,第一电流源支路i1包括:耦接于电源vcc和地之间的流向相反的第一支路第一电流源ip1和第一支路第二电流源in1;第二电流源支路包括:耦接于电源vcc和地之间的流向相反的第二支路第一电流源ip2和第二支路第二电流源in2,所述第一电流源支路和所述第二电流源支路分别包括电流流向相反的两个输出端。具体地,如图7所示,所述第一电流源支路包括:电流流向相反的第一输出端iop1和第二输出端ion1;所述第二电流源支路包括:电流流向相反的第一输出端iop2和ion2。

82.如图6所示的一种电流源驱动电路,其中,电流源驱动电路60包括锁存电路模块61、驱动电路模块80,和差分互补电流源70,其中,所述差分互补电流源中集成有差分互补电路模块、所述第一电流源支路和所述第二电流源支路。以下基于信号流向简单说明其工

作原理:

83.锁存电路模块61可以基于输入的第一路输入信号data1输出第一锁存信号data1p和第一锁存反相信号data1n,基于输入的第二路输入信号data2,输出第二锁存信号data2p和第二锁存反相信号data2n。进而所述驱动电路模块62基于所述第一锁存信号data1p、所述第一锁存反相信号data1n和所述第二锁存信号data2p和所述第二锁存反相信号data2n,在相应地输出端swn1_o、swn1_inv_o、swp1_o、swp1_inv_o、ex_swn1_o、ex_swn1_inv_o、ex_swp1_o、ex_swp1_inv_o、swn2_o、swn2_inv_o、swp2_o、swp2_inv_o、ex_swn2_o、ex_swn2_inv_o、ex_swp2_o、ex_swp2_inv_o共16路开关控制信号至所述差分互补电流源70。

84.在具体实施中,对于差分互补电路模块中的任一开关组子模块,均可以包括:导通开关单元和切换开关单元,其中:

85.所述导通开关单元,包括耦接于相应电流源支路的电流源和相应电流源支路输出端之间,适于基于接收到的开关使能控制信号导通相应电流源支路上的电流源与相应支路输出端形成的电流源输出通路;

86.所述切换开关单元,耦接于不同的电流源支路的输出端之间,适于基于接收到的开关使能控制信号切换与其耦接的电流源的输出端。

87.由上可知,所述导通开关单元中包括多个导通开关,所述切换开关单元中包括多个切换开关。

88.继续参照图6和图7所示,其中,在图7所示的全差分互补电路模块7a中,通过耦接于所述第一电流源支路和所述第二电流源支路之间的多个mos管作为导通开关或者切换开关,形成全差分互补电流源70,其中包括多个n型晶体管和p型晶体管,为与前述锁存电路模块中的晶体管进行区分,以下将全差分互补电路模块中的nmos型晶体管统一称为n型开关管,简称n型管,将全差分互补电路模块中的pmos型晶体管统一称为p型开关管,简称p型管。

89.具体而言,如图7所示,全差分互补电路70中,第一n型管n1、第二n型管n2、第一p型管p1和第二p型管p2作为导通开关,和第一电流源支路i1的电流源i1p、i1n组成第一互补全差分电流源i01,其中,swn1、swp1、swn1_inv和swp1_inv为开关使能控制端,开关使能控制端swn1和swn1_inv接收到的为互补信号,开关使能控制端swp1和swp1_inv接收到的为互补信号;第三n型管n3、第四n型管n4、第三p型管p3和第四p型管p4和第二电流源支路i2的电流源i2p、i2n组成第二互补全差分电流源i02,其中,swn2、swp2、swn2_inv和swp2_inv为开关使能控制端,开关使能控制端swn2和swn2_inv接收到的为互补信号,开关使能控制端swp2和swp2_inv接收到的为互补信号;互补全差分电流源ip1、in1的输出为iop1和ion1;互补全差分电流源ip2、in2的输出为iop2和ion2。第五n型管n5、第六n型管n6、第七n型管n7、第八n型管n8和第五p型管p5、第六p型管p6、第七p型管p7、第八p型管p8作为所述第一互补全差分电流源i01和第一互补全差分电流源i02的切换开关,ex_swn1、ex_swp1、ex_swn2、ex_swp2、ex_swn1_inv、ex_swp1_inv、ex_swn2_inv、ex_swp2_inv为切换开关的使能控制端。

90.以下参照图8所示的驱动电路模块的结构示意图,示例一种驱动电路模块基于锁存电路模块输出的信号,对所述差分电路模块中的开关进行通断控制,使得任一时刻所述任一电流源支路对应的开关组子模块中均有开关处于导通状态的具体方案。

91.在本说明书一些实施例中,如图8所示,驱动电路模块80包括:逻辑控制

92.所述驱动电路模块包括:逻辑控制子模块81,以及分别与所述逻辑控制子模块耦

接且结构相同的两个互不交叠时钟子模块,即第一互不交叠时钟子模块82、第二互不交叠时钟子模块83,其中:

93.所述逻辑控制子模块81,适于基于所述第一锁存信号data1p和所述第二锁存信号data2p,进行预设的逻辑运算,输出第一控制信号a和第二控制信号b。

94.所述两个互不交叠时钟子模块,分别输出开关控制信号至所述互补的开关组子模块,其中,对于任一互不交叠时钟子模块,适于分别基于对应的锁存子模块输入的所述锁存信号、锁存反相信号、所述第一控制信号a和所述第二控制信号b,输出多路开关控制信号至相应的电流源支路对应的开关组子模块,使得相应的电流源支路对应的开关组子模块中在任一时刻均有开关处于导通状态。

95.具体而言,如图8所示,所述第一互不交叠时钟子模块82,适于基于输入的所述第一锁存信号data1p、所述第一锁存反相信号data1n、所述第一控制信号a和所述第二控制信号b,输出多路开关控制信号至所述第一电流源支路i1对应的开关组子模块,使得所述第一电流源支路i1对应的开关组子模块中在任一时刻均有开关处于导通状态;

96.所述第二互不交叠时钟子模块83,适于基于输入的所述第二锁存信号data2p、所述第二锁存反相信号data2n、所述第一控制信号a和所述第二控制信号b,输出多路开关控制信号至第二电流源支路i2对应的开关组子模块,使得所述第二电流源支路i2对应的开关组子模块中在任一时刻均有开关处于导通状态。

97.在本说明书一些实施例中,继续参照图8,所述逻辑控制子模块81可以包括:异或门单元xor、第一延时单元delay1和第二延时单元delay2,其中:

98.所述异或门单元xor,其第一输入端适于输入所述第一锁存信号data1p,其第二输入端适于输入所述第二锁存信号data2p,其输出端分别与所述第一延时单元delay1的输入端和所述第二延时单元dalay2的第一输入端耦接;

99.所述第一延时单元delay1,其输入端与所述异或门单元xor的输出端耦接,其输出端适于输出所述第一控制信号a,并与所述第二延时单元delay2的第二输入端耦接;

100.所述第二延时单元delay2,适于输出所述第二控制信号b;

101.其中:所述第二延时单元delay2的延时时长小于所述第一延时单元delay1的延时时长。

102.作为一具体示例,所述第二延时单元delay2包括:第一与非门单元nand1和第五非门not5,其中:

103.所述第一与非门单元nand1,其第一输入端适于与所述异或门单元xor的输出端和所述第一延时单元delay1的输入端耦接,其第二输入端与所述第一延时单元delay1的输出端耦接,适于输入所述第一控制信号a,其输出端与所述第五非门not5的输入端耦接;

104.所述第五非门not5,其输入端与所述第一与非门单元nand1的输出端耦接,其输出端适于输出所述第二控制信号b。

105.在具体实施中,所述互不交叠时钟子模块可以包括:两个结构相同且相互耦合的互不交叠时钟单元,作为具体示例,所述互不交叠时钟单元可以包括:第三延时单元、第二与非门单元、第一或非门单元和第六非门,其中:

106.所述第三延时单元,其第一输入端与交叠时钟子模块对应,适于对应输入所述第一锁存信号、所述第一锁存反相信号、所述第二锁存信号和所述第二锁存反相信号其中之

一,其第二输入端适于与同一互不交叠子模块中另一互不交叠时钟单元的第三延时单元的输出端耦接,其包括两个反相的第一输出端和第二输出端,所述第三延时单元的延时时长小于所述第一延时单元的延时时长,且大于所述第二延时单元的延时时长;

107.所述第二与非门单元,其第一输入端适于与所述第三延时单元的第一输出端耦接,其第二输入端适于输入所述第一控制信号,其输出端适于向与其耦接的控制开关输出对应的开关控制信号,控制与其耦接的控制开关的通断;

108.所述第一或非门单元,其第一输入端适于与所述第三延时单元的第二输出端耦接,其第二输入端适于输入所述第二控制信号,其输出端与所述第六非门的输出端耦接;

109.所述第六非门,适于向与其耦接的控制开关输出对应的开关控制信号,控制与其耦接的控制开关的通断;

110.所述第七非门,其输入端与所述第二与非门单元的输出端耦接,其输出端适于向与其耦接的控制开关输出对应的开关控制信号,控制与其耦接的控制开关的通断;

111.所述第八非门,其输入端适于与所述第六非门的输出端耦接,其输出端适于向与其耦接的控制开关输出对应的开关控制信号,控制与其耦接的控制开关的通断。

112.作为具体示例,所述第三延时单元可以包括:依次耦接的与门、第四延时单元和第九非门,其中:所述第九非门的输出端作为所述第三延时单元的第一输出端,所述第四延时单元的输出端作为所述第三延时单元的第二输出端。

113.在具体实施中,所述第一延时单元的延时时长大于所述第四延时单元的延时时长。

114.为使本领域技术人员更好地理解和实施,以下参照图8示出的第一互不交叠时钟子模块82一具体电路结构进行说明。

115.所述第一互不交叠时钟子模块82包括:两个结构相同且相互耦合的互不交叠时钟单元,即第一互不交叠时钟单元82a和第二互不交叠时钟单元82b,其中:

116.第一互不交叠时钟单元82a包括:第三延时单元delay3、第二与非门单元nand2、第一或非门单元nor1、第六非门not6、第七非门not7和第八非门not8,其中:

117.所述第三延时单元delay3,其第一输入端与交叠时钟子模块对应,适于对应输入所述第一锁存信号data1p,其第二输入端适于与第二互不交叠时钟单元82b的第三延时单元delay3的输出端耦接,其包括两个反相的第一输出端和第二输出端,所述第三延时单元delay3的延时时长小于所述第一延时单元delay1的延时时长,且大于所述第二延时单元delay2的延时时长。

118.所述第二与非门单元nand2,其第一输入端适于与所述第三延时单元delay3的第一输出端耦接,其第二输入端适于输入所述第一控制信号a,其输出端适于向与其耦接的控制开关输出对应的开关控制信号swp1_o,控制与其耦接的控制开关的通断。结合图6至图8可知,第一互不交叠时钟单元82a中信号经与非门nand2后,输出的开关控制信号适于控制全差分互补电路模块70中的第二p型管p1,当其输出低电平时,所述第二p型管p2导通,第一电流源支路i1中的电流源ip1可以通过输出端ion1输出电流。

119.所述第一或非门单元nor1,其第一输入端适于与所述第三延时单元dealy3的第二输出端耦接,其第二输入端适于输入所述第二控制信号b,其输出端与所述第六非门not6的输出端耦接,所述第六非门not6,适于向与其耦接的控制开关输出对应的开关控制信号,控

制与其耦接的控制开关的通断。结合图6、图7和图8可知,控制的开关为第八p型晶体管p8,当第八p型晶体管p8导通时,第一电流源支路i1中的电流源ip1可以通过输出端ion2输出电流。

120.所述第七非门not7,其输入端与所述第二与非门单元nand2的输出端耦接,其输出端适于向与其耦接的控制开关输出对应的开关控制信号,控制与其耦接的控制开关的通断。结合图6-图8可知,控制的开关为第一n型晶体管n1,当第一n型晶体管n1导通时,第一电流源支路i1中的电流源in1可以通过输出端iop1流入电流。

121.所述第八非门not8,其输入端适于与所述第六非门not6的输出端耦接,其输出端适于向与其耦接的控制开关输出对应的开关控制信号,控制与其耦接的控制开关的通断。结合图6、图7和图8可知,控制的开关为第五n型晶体管n5,当第五n型晶体管n5导通时,第一电流源支路i1中的电流源in1可以通过输出端iop2流入电流。

122.结合图6-图8,可以看出图8所示的驱动电路模块80中各个输出端输出的开关控制信号与图7所示的全差分互补电路模块中各个开关之间的控制关系,通过驱动电路模块80,可以实现图7中的任一电流源连接的开关均不会同时关闭。

123.以下简要描述采用本说明书实施例中的电流源驱动电路的工作特性。

124.在任何情况下(包括第一路输入信号data1、第二路输入信号data2二者同时为1、同时为0,或者一个为0一个为1):

125.1)电流源in1连接的n型晶体管n1、n2、n5、n8不会同时关闭,即开关使能控制端swp1_inv、swn1_inv、ex_swn1_inv、ex_swp1_inv不会同时为低电平;

126.2)电流源in2连接的n型晶体管n3、n4、n6、n7不会同时关闭,即开关使能控制端swp2_inv、swn2_inv、ex_swp2_inv、ex_swn2_inv不会同时为低电平;

127.3)电流源ip1连接的p型晶体管p1、p2、p5、p8不会同时关闭,即开关使能控制端swn1、swp1、ex_swn1、ex_swp1不会同时为高电平;

128.4)电流源ip2连接的p型晶体管p3、p4、p6、p7不会同时关闭,即开关使能控制端swn2、swp2、ex_swn2、ex_swp2不会同时为高电平。

129.5)当第一路输入信号data1和第二路输入信号data2相同时,第一电流源支路的电流源ip1和in1流入或者流出输出端iop1和ion1,第二电流源支路的电流源ip2和in2流入或流出输出端iop2和ion2;

130.6)当第一路输入信号data1和第二路输入信号data2不同时,第一电流源支路的电流源ip1和in1流入或者流出输出端iop2和ion2,第二电流源支路的电流源ip2和in2流入或流出输出端iop1和ion1。

131.在电流源开关控制端信号发生变化时,上述工作特性可以避免在第一路和第二路切换过程中与电流源相连的开关同时关闭,导致电流源需要重新建立的过程,本说明书实施例中上述电流源电路能避免这一现象,因而可以提高电路性能。

132.对于第一路输入信号data1和第二路输入信号data2,如前所述,其可能的情况有二者均为0(对应低电平),二者均为1(对应高电平),二者中其中一个从0切换至1,二者中其中一个从1切换至0。相应地,第一锁存信号data1p和第二锁存信号data2p经过所述锁存电路模块对应的延时后输出,所述第一锁存信号data1p与所述第一路输入信号data1保持一致,所述第二锁存信号data2p与所述第二路输入信号data2保持一致。参照图9a-图9d所示

的输入信号切换过程中相应的开关组子模块的开关控制信号的波形图,其中示出了对应第一锁存信号data1p和第二锁存信号data2p各种情况下晶体管p1、p2、p5、p8对应的开关使能信号swn1、swp1、ex_swn1和ex_swp1的电压波形图。

133.具体地,图9a示出了第一锁存信号data1p保持为0,第二锁存信号data2p从0切换至1过程中对应的锁存信号及相应开关的电压波形图。参照图6-图8并结合图9a,由图9a可知,在第一锁存信号data1p和第二锁存信号data2p均为0时,晶体管p1对应的开关使能信号swn1为0,因此,与之耦接的第一电流源ip1不会关闭;在第二锁存信号data2p从0切换至1的过程中,由图9a可以看出,晶体管p2、p5、p8中始终有一个保持为0,使得与之耦接的第一电流源ip1始终处于导通状态,而在切换完成后,晶体管p5保持为0,使得第一电流源ip1可以通过输出端iop2输出电流。

134.图9b示出了第一锁存信号data1p从0切换为1,第二锁存信号data2p同步从1切换至0过程中对应的锁存信号及相应开关的电压波形图,也即对应交换电流源的情形。参照图6-图8并结合图9b,由图9b可知,在第一锁存信号data1p为0,第二锁存信号data2p为1时,晶体管p5对应的开关使能信号ex_swn1为0,因此,与之耦接的第一电流源ip1不会关闭;在第二锁存信号data2p从0切换至1的过程中,由图9b可以看出,晶体管p5保持为0,使得与之耦接的第一电流源ip1仍然处于导通状态,而在切换完成后,晶体管p2保持为0,使得第一电流源ip1可以通过输出端ion1输出电流。

135.图9c示出了第一锁存信号data1p从0切换为1,第二锁存信号data2p始终保持为1过程中对应的锁存信号及相应开关的电压波形图。参照图6-图8并结合图9c,由图9c可知,在第一锁存信号data1p为0,且第二锁存信号data2p为1时,晶体管p5对应的开关使能信号ex_swn1为0,因此,与之耦接的第一电流源ip1不会关闭;在第一锁存信号data1p从0切换至1的过程中,由图9c可以看出,晶体管p5保持为0,使得与之耦接的第一电流源ip1仍然处于导通状态,而在切换完成后,晶体管p8保持为0,使得第一电流源ip1可以通过输出端ion2输出电流。

136.图9d示出了第一锁存信号data1p从1切换为0,第二锁存信号data2p也同步从1切换为0过程中对应的锁存信号及相应开关的电压波形图。参照图6-图8并结合图9d,由图9d可知,在第一锁存信号data1p为1,且第二锁存信号data2p为1时,晶体管p8对应的开关使能信号ex_swp1为0,因此,与之耦接的第一电流源ip1不会关闭,通过输出端ion2输出电流;在第一锁存信号data1p和第二锁存信号data2p同步从1切换至0的过程中,由图9d可以看出,晶体管p8保持为0,使得与之耦接的第一电流源ip1一直处于导通状态,而在切换完成后,即第一锁存信号data1p和第二锁存信号data2p同步切换为0后,晶体管p1保持为0,使得第一电流源ip1可以通过输出端iop1输出电流。

137.由以上分别耦接在第一电流源ip1和四个输出端之间的晶体管p1、p2、p5和p8对应的使能开关控制信号随第一锁存信号data1p和第二锁存信号data2而变化的电压波形图可知,不论第一锁存信号data1p和第二锁存信号data2输入为何值,也不论第一锁存信号data1p和第二锁存信号data2如何变化,在所述第一电流源ip1和输出端iop1、iop2、ion1和ion2之间,总有开关处于导通状态,因此不论所述第一路输入信号data1和所述第二路输入信号data2如何变化,所述第一电流源ip1均不会被关闭,即使在快速切换过程中。

138.类似地,不论所述第一路输入信号data1和所述第二路输入信号data2如何变化,

第一支路第二电流源in1、第二支路第一电流源ip2和第二支路第二电流源in2与输出端iop1、iop2、ion1和ion2耦接的开关中,也始终至少有一个处开关于导通状态,从而在任何情况下,所述第一支路第二电流源in1、第二支路第一电流源ip2和第二支路第二电流源in2均存在导通的电流流入或流出的路径,此处不再赘述。

139.在具体实施中,所采用的差分互补电路模块也可以为半差分互补电路模块,参照图7所示的差分互补电路模块的电路结构示意图,在具体实施中,所采用的差分互补电路模块可以为耦接在所述第一支路第一电流源ip1和第二支路第一电流源ip2和多个输出端iop1、iop2、ion1和ion2之间的差分互补电路模块7a,此时,所述第一支路第二电流源in1和第二支路第二电流源in2与所述多个输出端iop1、iop2、ion1和ion2之间直接连接,且所述第一支路第一电流源ip1和所述第二支路第一电流源ip2的电流值。类似的,所采用的差分互补电路模块也可以为耦接在所述第一支路第二电流源in1和第二支路第二电流源in2和输出端iop1、iop2、ion1和ion2之间的差分互补电路模块7b,此时,所述第一支路第一电流源ip1和第二支路第一电流源ip2与所述多个输出端iop1、iop2、ion1和ion2之间直接连接,且所述第一支路第二电流源in1和所述第二支路第二电流源in2的电流值加倍。

140.相应地,可以匹配得到上述半差分互补电路模块7a和7b对应的驱动电路模块的结构,参照图8,若根据需要,电流源驱动电路中采用半差分互补电路模块7a或7b,对应的驱动电路模块各互不交叠时钟单元中未使用到的控制信号保持开路即可,即不与其他模块产生连接关系;或者,若确定所述电流源驱动电路仅适于半差分互补电路模块,则所采用的半差分互补电路模块7a或7b中,可以不包括相应的器件,例如可以不包含第七非门not7个第八非门not8。

141.由上述工作特性1)-4)可知,任一电流源与各输出端连接的开关不会同时关闭,这意味着在边沿时刻存在共同导通的时间,共同导通时间大小可以通过调节第四延时单元delay4和第一延时单元delay1的延时时长而得到。

142.在高速应用中,对延时时长的要求很高,就各延时单元delay2、delay3、delay1对应的延时时长t2、t3、t1而言,除了需要满足t2<t3<t1之外,延时的绝对时间越短越好。为此,在本说明书一些实施例中,提供了一种时延检测方法,能够在满足上述条件的基础上,将绝对的延时时间降至最低。

143.具体而言,可以采用一时延校准模块与所述第一延时单元delay1和所述第四延时单元delay4分别耦接,其中初始设置所述第四延时单元dealy4的延时时长t4为固定值,所述第一延时单元delay1的延时时长t1,t1>t4,且t1调节步长为所述第一延时单元delay1总调节延时时长的1/2n,之后将预设的测试时钟信号输入所述时延校准模块,并使所述第一延时单元delay1进行累积计数,直至所述时延校准模块的输出满足预设条件时所述第一延时单元delay1对应的时长为所述电流源驱动电路中所述第一延时单元dealy1的延时时长。

144.在本说明书一些实施例中,如图10所示的时延校准模块的结构示意图,时延校准模块100可以包括时钟输入单元ck、第一触发器d1、第二触发器d2和两个结构相同的重置单元rs1、rs2,其中:

145.所述时钟输入单元ck,其第一输入端适于输入所述测试时钟信号test_clk,其第二输入端适于输入测试使能信号test_en,其输出端适于输出第一时钟信号clk至所述第一

延时单元delay1和所述第四延时单元delay4;

146.所述第一触发器d1,其d输入端适于与电源vdd耦接,其时钟信号输入端ck与所述第四延时单元delay4的输出端耦接,其输出端适于输出第一检测信号q1;

147.所述第二触发器d2,其d输入端适于与电源vdd耦接,其时钟信号输入端ck与所述第一延时单元delay1的输出端耦接,其输出端适于输出第二检测信号q2;

148.所述重置单元rs1,适于基于输入的重置信号,向与其耦接的第一触发器d1的重置端rst输出重置信号rst1;

149.所述重置单元rs2,适于基于输入的重置信号,向与其耦接的第二触发器d2的重置端rst输出重置信号rst2;

150.其中,所述预设条件为所述第一检测信号q1和所述第二检测信号q2随着所述第一延时单元delay1的延时时长累加发生跳变。

151.更具体地,继续参照图10,所述时钟输入单元ck包括:依次耦接的第三与非门单元nand3和第十非门not10,其中:

152.所述第三与非门单元nand3,其第一输入端适于输入所述测试时钟信号test_clk,其第二输入端适于输入测试使能信号test_en;

153.所述第十非门not10,适于基于所述第三与非门单元nand3输出的第二时钟信号clk1,输出所述第一时钟信号clk0。

154.作为具体示例,所述重置单元rs1可以包括:第二或非门单元nor2和第十一非门not9,其中:

155.所述第二或非门单元nor2,其第一输入端适于输入所述重置信号rst,其第二输入端适于与第二触发器d2(即非待重置的触发器)的输出端q2耦接,其输出端适于与所述第十一非门not11的输入端耦接;

156.所述第十一非门not11,与第一触发器d1(对应的待重置的触发器)的重置端rst耦接。

157.所述重置单元rs2与所述重置单元rs1具有相同结构,此处不再赘述。

158.以下结合图11,说明图10所示的时延校准模块基于第四延时单元delay4的延时时长t4得到第一延时单元delay1的延时时长的自动校准过程。

159.在检测之前,复位所述第一触发器d1和第二触发器d2,q1和q2输出均为0(表示低电平),固定第四延时单元delay4的延时时长t4,调整第一延时单元delay1的初始值。在具体实施中,可以采用一多比特存储单元trim《x:0》存储所述第一延时单元delay1的设置值。作为一具体示例,6比特存储单元存储所述delay1的设置值trim《5:0》,基于设置值trim《5:0》,可以得到所述第一延时单元delay1的延时时长t1。

160.当设置值trim《5:0》=000000时,t1《t4;当设置值trim《5:0》=111111时,t1》t4,此时输入测试时钟test_clock。观察输出,因为调整到最小的t1<t4,所以q1=0、q2=1(0为低电平,与地gnd等效;1为高电平,与电源vdd等效),下一步将trim《5:0》值加1,重复上述过程,直到q1=1、q2=0,则delay2》delay1,且绝对时延为最小,此时得到校准值delay1_num为trim《5:0》当前累计计数值,即delay1_num=trim《5:0》。

161.校准流程图如图11所示,具体可以包括如下步骤:

162.步骤s10,即对应初始状态,测试时钟使能信号test_en设置为0,重置信号rst设置

为1;

163.步骤s11,进行如下设置:重置信号rst=0,trim《5:0》=000000,测试使能信号test_en=1。

164.步骤s12,确定第一触发器的输出q1是否等于1,且第二触发器q2的输出是否等于0,如果是,则执行步骤s13;否则执行步骤s14;

165.步骤s13,所述第一延时单元delay1对应的延时调整值delay_num=trim《5:0》;

166.步骤s14,令trim《5:0》=trim《5:0》+1,即将设置值trim《5:0》累计计数;

167.步骤s15,重新设置测试时钟使能信号test_en为0,重置信号rst为1。

168.经步骤s11~s13,所得到的第一延时单元delay1的延时时长t1和第四延时单元delay4的延时时长t4之差的绝对值最小,则取此时第一延时单元delay1对应的delay1_num=trim《5:0》,并执行步骤s15,即使所述时延校准模块重新回到初始状态。

169.在具体实施中,所述第一延时单元delay1与所述第四延时单元delay4的时延差值的绝对值的精度与设置值trim《x:0》的比特数有关,比特数越多,相对精度更高,绝对时延差值更小。

170.在具体实施中,可以在所述电流源驱动电路正常工作前,使用上述实施例中自动校准电路及校准流程进行全自动校准,以满足电路具体应用需求。

171.可以理解的是,所述重置单元rs1、rs2也可以是其他的电路结构,只要能够基于所述第四延时单元delay4的延时时长,能够实现所述第一延时单元delay1延时时长的自动校准即可。

172.采用本说明书实施例中的电流源驱动电路,可以避免开关过程中电流源通路被短时间关闭。

173.本说明书实施例中的电流源驱动电路可以应用于模数转换器中,为使本领域技术人员更好地理解和实施,本说明书实施例还提供了对应的模数转换器,参照图12所示的一种模数转换器的结构示意图,其可以作为复数型模数转换装置,例如复数连续时间sdadc中,具体可以应用于接收机中用于射频调制。

174.如图12所示,模数转换器120可以包括:第一输入通路12i、第二输入通路12q和反馈通路12f,其中:

175.所述第一输入通路12i,适于基于第一输入信号inq和所述反馈通路12f输出的第一反馈信号i,得到第一路输出信号outi;

176.所述第二输入通路12q,适于基于第二输入信号inq和所述反馈通路12f输出的第一反馈信号q,得到第二路输出信号outq;

177.所述反馈通路12f,与所述第一输入通路12i和第二输入通路12q分别耦接,包括:第一电流源支路(未示出)和第二电流源支路(未示出)和电流源驱动电路12d和反馈通路模数转换装置,其中:

178.所述的电流源驱动电路12d,其第一输入端与所述第一输入通路的输出端耦接,将所述第一输入通路12i所输出的第一路输出信号outi作为反馈通路12f的第一路输入信号data1;其第二输入端与所述第二输入通路12q的输出端耦接,将所述第二输入通路12q所输出的第二路输出信号outq作为反馈通路12f的第二路输入信号data2,基于所述第一路输入信号data1和所述第二路输入信号data2,导通所述反馈通路数模转换器和所述第一电流源

支路,以及导通所述第二反馈通路数模转换器和所述第二电流源支路;

179.反馈通路数模转换装置daci+dacq,适于基于所述电流源驱动电路12d的开关控制,输出所述第一反馈信号i至所述第一输入通路12i,以及输出所述第二反馈信号q至所述第二输入通路12q。

180.其中,所述反馈通路中的电流源驱动电路可以采用本说明书前述任一实施例中的电流源驱动电路,具体可以参见前述实施例,此处不再展开描述。

181.采用上述实施例中的模数转换器,所述电流源驱动电路12d可以同时驱动两路dac,作为具体示例,一路可以驱动i路dac,即daci;另一路可以驱动q路dac,即dacq。

182.在反馈通路12f中,可以按照一定规律交换i路和q路的dac电流源,即交换所述daci和dacq对应的第一电流源支路和所述第二电流源支路的电流源,来减小或消除i路和q路对应的反馈dac(即daci+dacq)的失配。例如,可以当iq两路反馈dac(即daci+dacq)对应的输入信号data1和data2相同时,交换iq两路对应的电流源,即切换对应的电流源;当iq两路反馈dac(即daci+dacq)对应的输入信号data1和data2不同时,则无须交换iq两路对应的电流源。

183.由前述实施例可知,不论第一路(例如i路)输入信号data1和第二路(例如q路)输入信号data2输入的具体是什么数据,或者如何切换,所述daci对应的i路和q路均有电流源导通,因而不会出现电流源暂时关闭而需要重建的情况,因此,可以减小反馈通路12f的失配,将所述电流源驱动电路12d应用于模数转换器,用于信号解调,可以提高解调性能。

184.在具体实施中,所述第一输入通路12i和所述第二输入通路12q中均可以包括:加法器和量化器,其中:所述加法器,适于将相应通路的输入信号和反馈信号进行累加,得到一连续信号;所述量化器,适于将所述连续信号量化成离散信号,以完成模数转换的基本功能。

185.如图12所示,所述第一输入通路12i可以包括加法器1和量化器1,所述第二输入通路12q可以包括加法器2和量化器2。

186.在具体实施中,为滤除量化噪声,所述第一输入通路12i和第二输入通路12q中均还包括滤波器,可以设置于所述加法器和量化器之间。在环路中,所述滤波器可以和其他模块一起形成一个滤波电路,滤除带内量化噪声。如图12所示,第一输入通路12i还包括滤波器1,所述第二输入通路12q还包括滤波器2。

187.在具体实施中,所述反馈通路12f还可以包括:数据加权平均器(data weighted averager,dwa),耦接于相应的输入通路的输出端与所述电流源驱动电路12d之间,适于将相应输入通路量化得到的离散信号进行预设的变换,得到dwa变换后的数字信号,所述反馈dac(即daci+dacq)可以将dwa变换后的数字信号转换成模拟信号后送入调制解调器的输入端,即第一输入通路(i路)的输入端和第二输入通路(q路)的输入端。

188.如图12所示,所述反馈通路12f可以包括dwa1和dwa2,其中:dwa1,耦接于所述第一输入通路12i的输出端与所述电流源驱动电路12d之间;dwa2,耦接于所述第二输入通路12q的输出端与所述电流源驱动电路12d之间。

189.在具体实施中,所述反馈通路数模转换装置(dac+dacq)中,可以采用多路反馈dac,也即对于i路dac和q路dac,均可以采用多个dac单元,所述多个dac单元均并联于相应的电流源支路,并共用电流源输出端。

190.在本说明书实施例中,锁存电路模块、驱动电路模块和差分互补电路模块及相应的电流源,可以构成一个基本的电流源单元,如图13所示的一种多路反馈dac的结构示意图,作为一具体示例,其中多路反馈dac130包含32个dac单元13i,所述32个dac单元13i可以并联连接,对于所述32个dac单元中的任一dac单元13i,其中均包括本说明书前述实施例所示的锁存电路模块、驱动电路模块和所述差分互补电路模块(例如所述全差分互补电路模块),并共用各电流源支路的输出端iop1、ion1、iop2和ion2,如图13所示。

191.此外,在反馈通路中,多个dac单元的输入和量化器的输出一一对应,即使反馈通路中设置有dwa来改变二者之间的对应关系,但是二者的位数依然保持一致。

192.例如,量化器输出的是5级的温度计码,对应的输出为:0000,0001,0011,0111,1111,有4个比特。由于iq两路是集成在一起的,因此i路有4个比特,q路也有4个比特,假设i路对应的4个比特从高到低依次为biti3 biti2 biti1 biti0,q路对应的4个比特从高到低依次为bitq3 bitq2 bitq1 bitq0,则相应位数的比特值为一个锁存电路模块的输入,例如biti3 bitq3为一个锁存电路模块的输入,biti2 bitq2为另一个锁存电路模块的输入,依此类推,共有四个锁存电路模块,相应的驱动电路模块和差分互补电路模块及相应的电流源也分为4组,这四组电流源共用输出。

193.采用dwa,通过将量化器输出的数字信号进行一定的变换后送到dac,可以用于消除多位dac单元之间的失配,例如可以消除图13所示的32个dac单元13i之间的失配。

194.在具体实施中,可以将上述模数转换器应用于接收机中,例如可以应用于低中频接收机。本说明书实施例中,参照图14所示的接收机的结构示意图,其中,接收机140可以包括:解调装置141和模数转换器142,其中:

195.解调装置141,适于对射频输入信号rf进行解调处理,得到同相正交的第一输入信号ini和第二输入信号inq;

196.模数转换器142,适于对所述第一输入信号和所述第二输入信号进行模数转换,得到第一通路输出信号outi和第二通路输出信号outq。

197.其中,所述模数转换器142的具体实现可以采用前述模数转换器的具体实施例,此处不再展开描述。

198.在具体实施中,为进一步提高接收机性能,所述接收机140还可以包括如下电路器件:

199.低噪声放大器lna,适于对所述输入信号rf进行低噪声放大处理,得到电压信号;

200.跨导放大器gm,适于将所述经低噪声放大处理后的电压信号转换为电流信号并输出;

201.跨阻放大器tia,适于将所述电流信号转换为电压信号并输出。

202.上述各器件的位置及连接关系可以参照图14所示。

203.在具体实施中,可以根据需要仅使用本说明书实施例中的部分电路或器件,也可以根据需要将多个实施例组合使用。

204.虽然本说明书实施例披露如上,但本发明实施例并非限定于此。任何本领域技术人员,在不脱离本发明实施例的精神和范围内,均可作各种更动与修改,因此本发明实施例的保护范围应当以权利要求所限定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1