驱动保护电路的制作方法

1.本技术涉及电力电子技术领域,具体涉及一种驱动保护电路。

背景技术:

2.对于llc电路(即谐振电路)的demo(demonstration,原型或演示版),调试时易出现炸管。具体地,驱动电路中的外挂大阻值下拉电阻对lc谐振有衰减作用,且能降低电磁干扰(electromagnetic interference,emi)、电磁兼容性(electromagnetic compatibility,emc);但是下拉电阻大,驱动受电压的变化率(dv/dt)影响较大,会在驱动电路中产生一定程度的驱动串扰。尤其是驱动电路中采用阈值电压较小的场效应管(field

‑

effect transistor,fet)时,容易出现场效应管误开启,从而引起炸管。

技术实现要素:

3.鉴于此,本技术提供一种驱动保护电路,以改善现有的驱动电路中的下拉电阻的大小不易进行平衡控制及存在的驱动串扰、阈值电压小于传统硅mos管的fet误开启引起炸管等问题。

4.本技术提供了一种驱动保护电路,该驱动保护电路包括电连接的至少两个驱动保护模块,每个所述驱动保护模块包括驱动模块、下拉电阻、反相电路、第一开关管和第二开关管,所述驱动模块的第一输出端与所述第二开关管的第一端连接,所述驱动模块的第一输出端通过所述反相电路与所述第一开关管的第一端连接,所述驱动模块的第二输出端与所述第一开关管的第三端连接,所述第一开关管的第二端与所述第二开关管的第一端连接,所述下拉电阻与所述第一开关管并联,所述第二开关管的第二端与相邻的前一个驱动保护模块中的第二开关管的第三端连接。

5.其中,所述反相电路包括反相器,所述反相器的输入端与所述驱动模块的第一输出端连接,所述反相器的输出端与所述第一开关管的第一端连接。

6.其中,所述第一开关管包括第一mos管,所述第一开关管的第一端为所述第一mos管的栅极,所述第一开关管的第二端为所述第一mos管的漏极,所述第一开关管的第三端为所述第一mos管的源极。

7.其中,所述第二开关管包括第二mos管,所述第二开关管的第一端为所述第二mos管的栅极,所述第二开关管的第二端为所述第二mos管的漏极,所述第二开关管的第三端为所述第二mos管的源极。

8.其中,所述第二mos管为氮化镓(gan)高电子迁移率晶体管(high electron mobility transistor,hemt)、n型硅mos管或碳化硅(sic)mos管。

9.其中,所述驱动模块包括驱动芯片。

10.其中,所述驱动保护模块还包括上拉电阻,所述驱动模块的第一输出端通过所述上拉电阻与所述第二开关管的第一端连接。

11.其中,所述下拉电阻并联在所述第一开关管的第二端与第三端之间。

12.其中,所述驱动保护模块还包括串联电阻,所述串联电阻设置在所述反相电路与所述第一开关管之间。

13.其中,所述串联电阻的一端与所述反相电路的输出端连接,所述串联电阻的另一端与所述第一开关管的第一端连接。

14.本技术的上述驱动保护电路,通过在电连接的每个驱动保护模块中设置反相电路和第一开关管,使驱动模块的第一输出端通过反相电路与第一开关管的第一端连接,第一开关管的第二端与第二开关管的第一端连接。如此,当第一开关管关断时,其所在的驱动保护模块能够保留原有的下拉电阻,从而使得驱动保护电路能够有效抑制振铃、emi及emc;当第一开关管导通时,第一开关管通过旁路下拉电阻能够强拉低第二开关管的第一端的电压,使其小于阈值电压,从而避免驱动保护电路出现驱动串扰及第二开关管误开启引起炸管。因此,本技术的驱动保护电路可有效抑制振铃、emi、emc,避免出现驱动串扰及开关管误开启引起炸管。

附图说明

15.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

16.图1是现有技术中的一种驱动电路的电路结构示意图;

17.图2是现有技术中的另一种驱动电路的电路结构示意图;

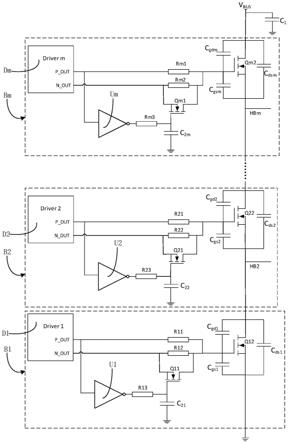

18.图3是本技术实施例提供的一种驱动保护电路的电路结构示意图;

19.图4是本技术实施例提供的另一种驱动保护电路的电路结构示意图。

具体实施方式

20.下面结合附图,对本技术实施例中的技术方案进行清楚描述,在不冲突的情况下,下述各个实施例及其技术特征可以相互组合。

21.在现有的驱动电路中,虽然外挂大阻值下拉电阻对lc谐振有衰减作用,且能降低emi、emc,但是下拉电阻大,驱动受电压的变化率(dv/dt)影响较大,会在驱动电路中产生一定程度的驱动串扰,甚至会引起驱动电路中的fet误开启引起炸管。

22.具体地,如图1所示,是现有技术中的一种驱动电路的电路结构示意图,该驱动电路包括电连接的m个第一驱动模块a1、a2、

……

、am,m为大于或等于2的整数;例如,m=3或4等。如图2所示,是m=2时的驱动电路的电路结构示意图,在电路中,第二开关管q12、q22交替开通。当第二开关管q12关断时,下拉电阻r12阻值过小,关断时会产生较大的振铃,因此,下拉电阻r12阻值不能太小。经过死区时间,第二开关管q22导通瞬间,因为第二开关管q12保持关断,高压会直接加在第二开关管q12上的第二端(如漏极)上,在第一端(如栅极)出现驱动串扰。原因是此时第二开关管q12的寄生电容c

ds1

(漏源电容)的dv/dt值较大,寄生电容c

gd1

(米勒电容)的电流会返回到第二开关管q12的第一端(如栅极),流经下拉电阻r12将第一端(如栅极)的电压抬高到若u

g

高于第二开关管q12的阈值电压

(vth),导致第二开关管q12误开启,会引起第二开关管q12和q22直通,即炸管;此时若下拉电阻r12小,受dv/dt影响小,第一端(如栅极)的电压也会小,可避免炸管。

23.传统的硅mos管由于vth比较高,在3v左右,误开启情况较少,但是对于vth较小的开关管(例如gan hemt的vth只有1v左右)却是致命的,因此,对于vth较小的开关管,第二开关管q22导通瞬间,第二开关管q12的下拉电阻r12越小越好。可见,仅通过平衡设置下拉电阻r12的阻值,驱动电路不能实现在降低振铃、emi、emc的同时,避免出现驱动串扰和第二开关管q12误开启引起炸管。

24.为了解决相关技术中存在的问题,本技术实施例提供一种驱动保护电路。该驱动保护电路可以包括电连接的至少两个驱动保护模块,请参阅图3,图3是本技术实施例提供的一种驱动保护电路的电路结构示意图。图3中以m个驱动保护模块b1、b2、

……

、bm作为示例进行说明,其中,m为大于或等于2的整数;例如,m=3或4等。

25.每个驱动保护模块均包括驱动模块、下拉电阻、反相电路、第一开关管和第二开关管,例如,驱动保护模块b1包括驱动模块d1、下拉电阻r12、反相电路u1、第一开关管q11和第二开关管q12,驱动保护模块b2包括驱动模块d2、下拉电阻r22、反相电路u2、第一开关管q21和第二开关管q22,

……

,驱动保护模块bm包括驱动模块dm、下拉电阻rm2、反相电路um、第一开关管qm1和第二开关管qm2。

26.以驱动保护模块b1为例,驱动保护模块b1中的驱动模块d1的第一输出端与第二开关管q12的第一端连接,驱动模块d1的第一输出端通过反相电路u1与第一开关管q11的第一端连接,驱动模块d1的第二输出端与第一开关管q11的第三端连接,第一开关管q11的第二端与第二开关管q12的第一端连接,下拉电阻r12与第一开关管q11并联,第二开关管q12的第二端与相邻的前一个驱动保护模块b2中的第二开关管q22的第三端连接。

27.本实施例中,通过在电连接的每个驱动保护模块b1(b2,

……

,或bm)中设置反相电路u1(u2,

……

,或um)和第一开关管q11(q21,

……

,或qm1),使驱动模块d1(d2,

……

,或dm)的第一输出端通过反相电路u1(u2,

……

,或um)与第一开关管q11(q21,

……

,或qm1)的第一端连接,第一开关管q11(q21,

……

,或qm1)的第二端与第二开关管q12(q22,

……

,或qm2)的第一端连接。如此,当驱动模块d1(d2,

……

,或dm)的第一输出端输出正电压时,正电压经反相电路u1(u2,

……

,或um)后输出为负电压,则第一开关管q11(q21,

……

,或qm1)关断,电流流经与第一开关管q11(q21,

……

,或qm1)并联的下拉电阻r12(r22,

……

,或rm2),这样可以保证驱动保护电路在第二开关管q12关断时有较大的下拉电阻,从而使得驱动保护电路能够有效抑制振铃、emi及emc。驱动模块d1(d2,

……

,或dm)的第一端输出低电平时,第一开关管q11(q21,

……

,或qm1)导通,第一开关管q11(q21,

……

,或qm1)通过旁路(即短接)下拉电阻r12(r22,

……

,或rm2)能够强拉低第二开关管q12(q22,

……

,或qm2)的第一端的电压至小于第二开关管q12(q22,

……

,或qm2)自身的阈值电压,从而避免驱动保护电路出现驱动串扰及第二开关管误开启引起炸管。

28.在一些实施例中,反相电路u1(u2,

……

,或um)包括反相器,反相器的输入端与驱动模块d1(d2,

……

,或dm)的第一输出端连接,反相器的输出端与第一开关管q11(q21,

……

,或qm1)的第一端连接。如此,反相器的输出端能够为第一开关管的第一端提供一个与驱动模块的第一输出端的电压的正负性相反的电压,从而:通过第一开关管的关断使驱动保护电路流经下拉电阻,以及通过第一开关管的导通使下拉电阻被旁路,起到保护

第二开关管的作用。具体地,当驱动模块d1的第一输出端输出正电压时,正电压经反相器后输出为负电压,则第一开关管q11关断,电流流经与第一开关管q11并联的下拉电阻r12,这样可以保证驱动保护电路在第二开关管q12在关断时有较大的下拉电阻,从而使得驱动保护电路能够有效抑制振铃、emi及emc。当驱动模块d1的第一输出端输出为零时,经反相器后输出为正电压,第一开关管q11导通,旁路下拉电阻r12,在电路中形成强拉断,将第二开关管q12的第一端的电压强拉低至小于第二开关管q12自身的阈值电压,从而避免第二开关管q12在相邻驱动保护模块中的第二开关管q22导通瞬间误开启引起炸管,起到保护第二开关管的作用。

29.在一些实施例中,第一开关管q11(q21,

……

,或qm1)包括第一mos管,第一开关管q11(q21,

……

,或qm1)的第一端为第一mos管的栅极,第一开关管q11(q21,

……

,或qm1)的第二端为第一mos管的漏极,第一开关管q11(q21,

……

,或qm1)的第三端为第一mos管的源极。如此,通过在第一开关管中设置第一mos管,当第一mos管的栅极施加一定的电压时,可以高速开启或关闭第一mos管,当驱动模块d1的第一输出端输出为零时,经反相器后输出为正电压,第一开关管q11可以快速导通,从而快速旁路下拉电阻r12,在电路中形成强拉断,将第二开关管q12的第一端的电压强拉低至小于第二开关管q12自身的阈值电压,进而避免第二开关管q12在相邻驱动保护模块中的第二开关管q22导通瞬间误开启引起炸管,起到保护第二开关管的作用。

30.在一些实施例中,第二开关管q12(q22,

……

,或qm2)包括第二mos管,第二开关管q12(q22,

……

,或qm2)的第一端为第二mos管的栅极,第二开关管q12(q22,

……

,或qm2)的第二端为第二mos管的漏极,第二开关管q12(q22,

……

,或qm2)的第三端为第二mos管的源极。

31.可选的,第一mos管可为高速mos管;高速mos管的开启和关闭的速度快,采用高速mos管作为第一开关管,能够使第一开关管对施加在第一开关管的第一端的正/负电压快速响应:导通/关断。进一步地,高速mos管的导通电阻可为毫欧(mω)级。如此,当第一开关管q11导通时,旁路下拉电阻r12,此时第一开关管q11的导通电阻较小,电流流经第一开关管q11时形成较小的电压,从而强拉低第二开关管q12的第一端的电压,使第二开关管q12的第一端的电压小于其自身的阈值电压,因此可以避免出现第二开关管q12误开启引起的炸管。

32.在一些实施例中,第一mos管可为硅mos管,例如n型硅mos管。硅mos管具有导通电压低、开关速度极快、驱动能力要求相对低的特点,采用硅mos管作为第一开关管,能够使第一开关管对施加在第一开关管的第一端的正/负电压快速响应:导通/关断。进一步地,第一mos管具有较小内阻,无需具有太高电压,仅作为举例而不作限定,第一mos管可为2sk2158 50v或2sk508g 50v等低压高频mos。

33.可选的,第二mos管可为但不限于gan hemt管、n型硅mos管或sic mos管。上述范围的第二mos管的阈值电压小,通过本技术的驱动保护电路可以将其第一端的电压强拉低至小于其自身的阈值电压,从而有效避免第二mos管误开启引起炸管。

34.在一些实施例中,驱动保护电路可为半桥电路或全桥电路。半桥电路包括用于驱动各个下部晶体管和上部晶体管的低端驱动模块和高端驱动模块。全桥电路是四个三极管或mos管组成的振荡。半桥电路和全桥电路均包括至少两个与本技术的驱动保护电路中的第二开关管相同情况的开关管,因此,通过本技术的驱动保护电路可以将半桥电路或全桥

电路中的开关管的第一端的电压强拉低至小于其自身的阈值电压,从而有效避免半桥电路或全桥电路中的开关管误开启引起炸管。

35.在一些实施例中,驱动模块d1(d2,

……

,或dm)包括驱动芯片driver 1(driver 2,

……

,或driver m);驱动芯片具有集成化高的特点,采用驱动芯片作为驱动模块可以减小驱动保护电路的体积。可选的,驱动芯片driver 1(driver 2,

……

,或driver m)可为半桥驱动芯片或全桥驱动芯片;例如,半桥驱动芯片可为ir2104半桥驱动芯片,还可以为氮化镓驱动芯片。

36.在一些实施例中,驱动模块d1(d2,

……

,或dm)的第一输出端为p型输出端(p_out),第二输出端为n型输出端(n_out)。进一步的,第二输出端具有较小的内阻。如此,当第一开关管q11导通时,旁路下拉电阻r12,则第二输出端小的内阻与第一开关管q12小的导通电阻一起能够进一步确保第一开关管q11在电路中形成强拉断,从而确保将第二开关管q12的第一端的电压强拉低至小于第二开关管q12自身的阈值电压,进而避免第二开关管q12在相邻驱动保护模块中的第二开关管q22导通瞬间误开启引起炸管,起到保护第二开关管的作用。

37.在一些实施例中,驱动保护模块b1(b2,

……

,或bm)还包括上拉电阻r11(r21,

……

,或rm1),驱动模块d1(d2,

……

,或dm)的第一输出端通过上拉电阻r11(r21,

……

,或rm1)与第二开关管q12(q22,

……

,或qm2)的第一端连接。

38.在一些实施例中,下拉电阻r12(r22,

……

,或rm2)并联在第一开关管q11(q21,

……

,或qm1)的第二端与第三端之间。如此,当驱动模块d1的第一输出端的输出为零时,经反相电路u1对第一开关管施加正电压,第一开关管导通,能够旁路下拉电阻,在电路中形成强拉断,将第二开关管q12的第一端的电压强拉低至小于第二开关管q12自身的阈值电压,进而避免第二开关管q12在相邻驱动保护模块中的第二开关管q22导通瞬间误开启引起炸管,从而起到保护第二开关管的作用。当驱动模块d1的第一输出端的输出为正电压时,经反相电路u1对第一开关管q11施加负电压,则第一开关管q11关断,电流流经与第一下开关管q11并联的下拉电阻r12,这样可以保证驱动保护电路在第二开关管q12在关断时有较大的下拉电阻,从而使得驱动保护电路能够有效抑制振铃、emi及emc。

39.进一步的,在一些实施例中,驱动模块d1(d2,

……

,或dm)的第二输出端通过下拉电阻r12(r22,

……

,或rm2)与第二开关管q12(q22,

……

,或qm2)的第一端连接。

40.在一些实施例中,驱动保护模块b1(b2,

……

,或bm)还包括串联电阻r13(r23,

……

,或rm3),串联电阻r13(r23,

……

,或rm3)设置在反相电路u1(u2,

……

,或um)与第一开关管q11(q21,

……

,或qm1)之间。如此,通过在反相电路与第一开关管之间设置串联电阻,能够降低流经第一开关管的电流,从而延迟第一开关管的导通时间。

41.进一步的,在一些实施例中,串联电阻r13(r23,

……

,或rm3)的一端与反相电路u1(u2,

……

,或um)的输出端连接,串联电阻r13(r23,

……

,或rm3)的另一端与第一开关管q11(q21,

……

,或qm1)的第一端连接。如此,通过在反相电路与第一开关管之间设置串联电阻,能够降低流经第一开关管的电流,从而延迟第一开关管的导通时间。

42.进一步的,在一些实施例中,驱动保护模块b1(b2,

……

,bm)还包括第二电容c21(c22,

……

,或c2m),第二电容c21(c22,

……

,或c2m)的一端分别接第一开关管q11(q21,

……

,或qm1)的第一端和串联电阻r13(r23,

……

,或rm3)的另一端,第二电容c21

(c22,

……

,或c2m)的另一端接地。如此,设置的第二电容c21(c22,

……

,或c2m)与串联电阻r13(r23,

……

,或rm3)连接构成rc滤波电路,该rc滤波电路具有滤波和信号延迟作用。

43.应当理解的是,寄生电容c

gd1

、c

gd2

、

……

、c

gdm

均为米勒电容,寄生电容c

gs1

、c

gs2

、

……

、c

gsm

均为栅源电容,寄生电容c

ds1

、c

ds2

、

……

、c

dsm

均为漏源电容。

44.在一些实施例中,驱动保护电路还包括第一电容c1,第一电容c1的一端分别接电源v

bus

和一个驱动保护模块bm中的第二开关管qm2的第二端,第一电容c1的另一端接地。第一电容c1作为去耦(decoupling,也称退耦)电容,用来滤除驱动保护电路的输出信号的干扰。仅作为举例而不作限定,电源v

bus

的电压可以为5v。

45.在一些实施例中,一个驱动保护模块b1中的第二开关管q12的第三端接地。

46.应当理解的是,hb2、hb3、

……

、hbm均为输出端口。

47.请参阅图4,图4是本技术实施例提供的另一种驱动保护电路的电路结构示意图。驱动保护电路的工作原理如下:当驱动模块d1的第一输出端输出正电压时,正电压经反相电路u1后输出为负电压,则第一开关管q11关断;当驱动模块d1的第一输出端输出为零时,经反相电路u1输出为正电压,此时第一开关管q11导通,且驱动模块d1内部的第一输出端的内阻及第一开关管q11的内阻均较小,则第一开关管q11通过旁路(即短接)下拉电阻r12在电路中形成强拉断,从而强拉低第二开关管q12的第一端的电压,使其电压降低到小于阈值电压,从而避免出现第二开关管q12误开启引起的炸管。

48.因此,相对于现有技术,本技术的驱动保护电路的有益效果是:当驱动模块d1的第一输出端的输出为正电压时,经反相电路u1对第一开关管q11施加负电压,则第一开关管q11关断,电流流经与第一开关管q11并联的下拉电阻r12,这样可以保证驱动保护电路在第二开关管q12在关断时有较大的下拉电阻,从而使驱动保护电路能够有效抑制振铃、emi和emc。当驱动模块d1的第一输出端的输出为零时,经反相电路u1对第一开关管q11施加正电压,第一开关管q11导通,第一开关管q11通过旁路下拉电阻r12能够强拉低第二开关管q12的第一端的电压,使第二开关管q12的第一端的电压降低到小于第二开关管q12自身的阈值电压,从而使避免驱动保护电路出现驱动串扰及开关管误开启引起炸管。

49.尽管已经相对于一个或多个实现方式示出并描述了本技术,但是本领域技术人员基于对本说明书和附图的阅读和理解将会想到等价变型和修改。本技术包括所有这样的修改和变型,并且仅由所附权利要求的范围限制。

50.即,以上所述仅为本技术的实施例,并非因此限制本技术的专利范围,凡是利用本技术说明书及附图内容所作的等效结构或等效流程变换,例如各实施例之间技术特征的相互结合,或直接或间接运用在其他相关的技术领域,均同理包括在本技术的专利保护范围内。

51.另外,对于特性相同或相似的结构元件,本技术可采用相同或者不相同的标号进行标识。此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个特征。在本技术的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1