一种可以实现分布式存储器功能的查找表结构的制作方法

1.本发明涉及一种可以实现分布式存储器功能的查找表结构,属于集成电路设计技术领域。

背景技术:

2.现可编程逻辑单元是fpga芯片可以实现各种逻辑功能的基本构建模块,其基本结构包括查找表、触发器和多路选择器等。

3.在现代fpga中,除了可编程逻辑单元,往往还会在fpga结构中嵌入块存储器和乘法器。其中存储器主要用来存储在用户电路中待处理或产生的数据。同时为了提高块存储器的效果,块存储器的容量一般不能太小,容量太小,会造成面积效率的低下。

4.考虑到fpga的可编程性是通过配置存储器来实现的,一个具有100k逻辑单元的fpga往往包括数千万的配置存储单元,这些单元占据了大量的面积,如果能够将这些配置存储器利用起来,在特定模式下实现用户数据存储的功能,则有利于进一步提高fpga的面积利用率。

5.一个三输入查找表结构如图4所示,当中包括8bit sram单元和一个8选1多路选择器,当输入为某种组合时,通过多路选择器将对应地址的sram值读出。从而可以实现任意的3输入函数。

6.现有商用fpga一般会对查找表进行结构改进,使得查找表中用于存储用户数据的sram可以实现用户存储器的功能。其基本方法一般是对sram增加写电路。该方法实现了较小粒度的sram,充分利用了可编程逻辑单元查找表的特性。却存在以下问题:1、现有fpga芯片的可编程逻辑块多采用固定粒度的查找表结构,并且一般支持分布式存储器功能,例如xilinx的slice;2、现有fpga支持查找表拆分结构的可编程逻辑单元包括intel公司的alm,该结构支持分布式存储器功能,但是该结构在逻辑模式下实现不同函数组合的时候需要具有较多的公共输入端口。

技术实现要素:

7.本发明要解决技术问题是:克服上述技术的缺点,针对具有多个不同粒度查找表的可编程逻辑单元,提出一种与其相适配的分布式存储器方案,进一步增强了多粒度查找表的功能,可以实现更多独立的功能函数的多粒度查找表结构。

8.为了解决上述技术问题,本发明提出的技术方案是:一种可以实现分布式存储器功能的查找表结构,包括:地址译码器、字节使能模块、六输入查找表、五输入查找表、第一四输入查找表、第二四输入查找表和独立输入端;所述独立输入端与第一选择器的第一输入端、第二选择器的第一输入端、第三选择器的第一输入端均连接;所述六输入查找表的输入端中的一个输入与所述第一选择器的第二输入端、第二选择器的第二输入端均连接;所述五输入查找表的输入端中的一个输入与第三选择器的第二输入端连接;所述第一四输入查找表的输出端与第二四输入查找表的输出端分别连接第五选择器的第一输入端与第二

输入端;所述第三选择器的输出端连接所述第五选择器的选择端;所述第五选择器的输出端与所述五输入查找表的输出端分别连接第六选择器的第一输入端与第二输入端;所述第一选择器的输出端连接所述第六选择器的选择端;所述第六选择器的输出端与所述六输入查找表的输出端分别连接第七选择器的第一输入端与第二输入端;所述第二选择器的输出端连接所述第七选择器的选择端;所述地址译码器与字节使能模块均连接所述六输入查找表、五输入查找表、第一四输入查找表和第二四输入查找表。

9.上述方案进一步的改进在于:当查找表结构工作在64*2的双端口存储器功能时,所述六输入查找表构成相连的第一64选1选择器及第一存储器;所述六输入查找表的输入作为第一64选1选择器的读地址输入,输出作为第一64选1选择器的第一读数据输出;所述六输入查找表的存储上具有第一写数据输入;所述第一四输入查找表、第二四输入查找表、五输入查找表和第三选择器、第五选择器和第六选择器构成相连的第二64选1选择器及第二存储器;所述第一四输入查找表的输入端的全部输入与所述第二四输入查找表的输入端的全部输入一一对应,且与所述五输入查找表的输入端的除掉与所述第三选择器连接的输入外的四个输入一一对应,作为第二64选1选择器的读地址的四个输入,所述五输入查找表的输入端的与所述第三选择器连接的输入以及独立输入端作为第二64选1选择器的读地址的另外两个输入,所述第六选择器的输出作为第二64选1选择器的读数据输出;所述第二存储器上具有第二写数据输入;所述地址译码器上具有写地址输入端,且所述地址译码器与第一存储器、第二存储器均连接。

10.上述方案进一步的改进在于:当查找表结构工作在4个32 *1的双端口存储器功能时;所述六输入查找表拆分为相连的第一32选1选择器和第一存储器、以及第二32选1选择器和第二存储器,且所述六输入查找表中的5个输入作为第一和第二32选1选择器的读地址输入,第一和第二32选1选择器的输出分别作为第一和第二读数据输出;第一存储器和第一存储器分别具有第一写数据输入和第二写数据输入;所述五输入查找表构成相连的第三32选1选择器和第三存储器;所述五输入查找表的输入作为第三32选1选择器的读地址输入,输出作为第三读数据输出;第三存储器具有第三写数据输入;所述第一四输入查找表、第二四输入查找表、第三选择器和第五选择器构成相连的第四32选1选择器和第四存储器;所述第一四输入查找表的输入端的全部输入与所述第二四输入查找表的输入端的全部输入一一对应作为第四32选1选择器的读地址的四个输入,所述五输入查找表的输入端中与所述第三选择器连接的输入作为第四32选1选择器的读地址的另一个输入;所述第五选择器的输出作为第四读数据输出;第四存储器具有第四写数据输入;所述地址译码器上具有写地址输入端,且所述地址译码器与第一存储器、第二存储器、第三存储器、第四存储器均连接;所述字节使能模块与第一32选1选择器、第二32选1选择器、第三32选1选择器、第四32选1选择器均连接。

11.本发明提供的可以实现分布式存储器功能的查找表结构,在多粒度查找表的基础上,只增加了写地址译码器,和字节使能模块,通过对端口连接的重新分配,实现了两种模式的简单双端口存储器。该结构的读出功能复用了原来lut表的多路选择器,从而减少了面积。

附图说明

12.下面结合附图对本发明作进一步说明。

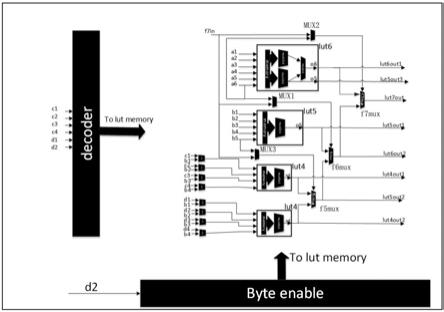

13.图1是本发明一个优选的实施例电路结构示意图。

14.图2是图1的实施例工作于64*2的双端口存储器功能时的等效电路结构示意图。

15.图3是图1的实施例工作于4个32 *1的双端口存储器功能时的等效电路结构示意图。

16.图4是三输入查找表结构电路结构示意图。

具体实施方式实施例

17.本实施例的可以实现分布式存储器功能的查找表结构,如图1所示,包括:地址译码器、字节使能模块、六输入查找表、五输入查找表、第一四输入查找表、第二四输入查找表和独立输入端f7in;独立输入端f7in与第一选择器mux1的第一输入端、第二选择器mux2的第一输入端、第三选择器mux3的第一输入端均连接;六输入查找表的输入端中的a6与第一选择器mux1的第二输入端、第二选择器mux2的第二输入端均连接;五输入查找表的输入端中的b5与第三选择器mux3的第二输入端连接;第一四输入查找表的输出端与第二四输入查找表的输出端分别连接第五选择器f5mux的第一输入端与第二输入端;第三选择器mux3的输出端连接第五选择器f5mux的选择端;第五选择器f5mux的输出端与五输入查找表的输出端分别连接第六选择器f6mux的第一输入端与第二输入端;第一选择器mux1的输出端连接第六选择器f6mux的选择端;第六选择器f6mux的输出端与六输入查找表的输出端分别连接第七选择器f7mux的第一输入端与第二输入端;第二选择器mux2的输出端连接第七选择器f7mux的选择端;地址译码器与字节使能模块均连接六输入查找表、五输入查找表、第一四输入查找表和第二四输入查找表。

18.如图4所示,是一种常见的三输入查找表结构包括8bit sram单元和一个8选1选择器,而其中的8选1选择器有三层2选1选择器构成,第一层4个,第二层2个,第三层1个。如果自第二层的2选1选择器输出,即得到了4选1选择器。同样的原理,将两个同样的查找表通过选择器连接在一起,也就是增加了选择器的层,也就能构成更多路的多路选择器。

19.基于以上原理,本实施例的技术方案可以实现64*2的双端口存储器功能,也就是说,构成两个64选1选择器,如图2所示。其中六输入查找表本身所具有的选择器即是64选1选择器,因此,直接使用即可,也就是六输入查找表由构成相连的第一64选1选择器及第一存储器;六输入查找表的输入作为第一64选1选择器的读地址输入,输出作为第一64选1选择器的第一读数据输出;六输入查找表的存储上具有第一写数据输入。

20.第一四输入查找表和第二四输入查找表组组合,配合第五选择器,构成32选1选择器,再结合五输入查找表和第六选择器f6mux就构成相连的第二64选1选择器及第二存储器;第一四输入查找表的输入端的全部输入与第二四输入查找表的输入端的全部输入一一对应,且与五输入查找表的输入端的除掉b5外的四个输入一一对应,作为第二64选1选择器的读地址的四个输入,五输入查找表的输入端的b5以及独立输入端f7in作为第二64选1选择器的读地址的另外两个输入,第六选择器f6mux的输出作为第二64选1选择器的读数据输

出;第一四输入查找表、第二四输入查找表和五输入查找表的存储器联合构成第二存储器,且第二存储器上具有第二写数据输入;地址译码器上具有写地址输入端,且地址译码器与第一存储器、第二存储器均连接。

21.本实施例中的查找表结构是完整功能的集成电路,因此,预留了20路输入,也即是图1中的a1到a6、b1到b5、c1到c4,d1到d4以及f7in。参考图2,工作在64*2的双端口存储器功能时,两个四输入查找表的输入于五输入查找表的b1到b4完全相同,此时,c1到c4,d1到d4是闲置的,因此,将其连接至地址译码器的写地址输入端,存储器的写数据输入等位置,实现引脚复用。

22.为了避免干扰,两个四输入查找表的输入,均使用2选1选择器于五输入查找表的b1到b4进行连接,如图1所示。

23.如图3所示,当查找表结构工作在4个32 *1的双端口存储器功能时;六输入查找表拆分为相连的第一32选1选择器和第一存储器、以及第二32选1选择器和第二存储器,也即是说,自前一层引出一路输出,且最后一层的2选1选择器的输出固定,不再选择即可。由此,六输入查找表中的5个输入作为第一和第二32选1选择器的读地址输入,第一和第二32选1选择器的输出分别作为第一和第二读数据输出;第一存储器和第一存储器分别具有第一写数据输入和第二写数据输入;五输入查找表构成相连的第三32选1选择器和第三存储器;五输入查找表的输入作为第三32选1选择器的读地址输入,输出作为第三读数据输出;第三存储器具有第三写数据输入;第一四输入查找表、第二四输入查找表、第三选择器mux3和第五选择器f5mux构成相连的第四32选1选择器和第四存储器;第一四输入查找表的输入端的全部输入与第二四输入查找表的输入端的全部输入一一对应作为第四32选1选择器的读地址的四个输入,五输入查找表的输入端中与第三选择器mux3连接的输入作为第四32选1选择器的读地址的另一个输入;第五选择器f5mux的输出作为第四读数据输出;第四存储器具有第四写数据输入;地址译码器上具有写地址输入端,且地址译码器与第一存储器、第二存储器、第三存储器、第四存储器均连接;字节使能模块与第一32选1选择器、第二32选1选择器、第三32选1选择器、第四32选1选择器均连接。字节使能模块能够实现2/4位宽控制。即字节使能功能开启时:可以实现每次对2位数据的读写,关闭时,可以实现每次对4位数据的读写。

24.根据以上两种工作模式,当输入数据与输出数据通过布线连接同样信号时,可以实现单端口模式。当写模式关闭时,可以实现rom模式。

25.本发明不局限于上述实施例。凡采用等同替换形成的技术方案,均落在本发明要求的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1