一种增益与带宽可调低噪声放大器

1.本发明涉及生物医学领域,具体涉及生物医学信号中的心电信号(ecg)和脑电信号(eeg)采集的低噪声低频信号放大器。

背景技术:

2.每年因非传染性疾病(ncd)死亡病例占总死亡人数的71%,其中首位的致死原因仍然是心脑血管疾病,占所有ncd死亡病例的44%,是癌症死亡病例的两倍。因此,预防和检测心脑血管疾病一直被各国医学界所重视,其中,eeg信号包含了脑部状况的重要信息。在生物医疗应用中,使用eeg信号诊断肿瘤、癫痫、脑病和脑死亡等疾病是很常见的,同时ecg信号也是预测心血管疾病的一个重要指标。

3.便携式传感器的开发在医疗保健系统中非常重要,特别是在医疗诊断和检测系统的长期检测方面。eeg和ecg信号都被认为是对诊断系统有用的信号。但它们本身都是微弱信号,eeg信号的振幅为uv量级,ecg信号的振幅为mv量级,容易受到各种噪声的影响,此外,eeg信号通带为0.5hz~50hz;ecg信号通带为0.05hz~150hz若要实现同一仪器检测两种信号,则有必要设计一个可调增益和可调带宽电路。通常一个电路只能检测一种信号,而心脑血管疾病往往伴随着脑电信号的波动,多功能便携式设备又是当前医疗检测仪器发展的一个趋势,所以一台设备检测两种信号具有重要的意义。

技术实现要素:

4.为了解决现有技术的缺陷并实现上述功能,本发明提供一种同时检测ecg和eeg信号的模拟前端电路,本发明的输出不受输入阻抗的影响,能有效降低信号输入噪声。

5.本发明要解决的技术问题通过以下技术方案实现:一种增益与带宽可调低噪声放大器,包括差分斩波单元、电容分压单元、可调带宽增益滤波单元、斩波时钟、开关电容时钟,差分斩波单元具有两个输入信号端用于将经过第一斩波单元的输入信号进行放大后输出,再将差分斩波单元的输出输入到可调带宽增益滤波单元和电容反馈单元,电容分压单元将信号分压处理后输出到差分斩波单元的反馈端口,可调带宽增益滤波单元将差分斩波单元的输出信号进行增益放大和相应带宽的滤波,其特征在于:差分斩波单元包括差分输入器,差分反馈,第一直流偏置器,第二直流偏置器,两级放大器,第一输入斩波单元,第二输入斩波单元,输出斩波单元,

6.其中两级放大器包括第九nmos,第十nmos,第十四nmos,第十一pmos,第十二pmos,第十三pmos,第三电容,第九nmos源极连接gnd,第九nmos栅极连接输出斩波单元的正相输出,第九nmos漏极连接第十一pmos的漏极;

7.第十nmos源极连接gnd,第十nmos栅极连接输出斩波单元的反相输出,第十nmos漏极连接第十二pmos的漏极和栅极;

8.第十一pmos源极连接vcc,第十一pmos栅极连接第十二pmos的栅极和漏极,第十一pmos漏极连接第九nmos的漏极、第十三pmos的栅极和第三电容的一端;

9.第十二pmos源极连接vcc,第十二pmos栅极连接第十二pmos的漏极并与第十nmos的漏极连接;

10.第十三pmos源极连接vcc,第十三pmos漏极连接第十四nmos的漏极,第十三pmos栅极连接第三电容的一端和第十一pmos的漏极;

11.第十四nmos漏极连接第十三pmos的漏极,第十四nmos源极连接gnd,第十四nmos栅极连接vbias;

12.第三电容一端连接第十一pmos的漏极,第三电容另一端连接第十三pmos的漏极。

13.与现有技术相比,本发明的有益效果在于:本发明能有效降低信号输入噪声;由于输入采用全差分结构,输入阻抗不匹配度对输出影响很小,并且输入阻抗不匹配不会影响共模抑制比的大小。对斩波电路处理,能有效防止时钟馈通和对模拟信号的影响。使用电容作为分压元件不存在因制造原因存在的漂移问题,可调节增益和带宽单元,可以在不同的工作模式下处理不同的输入信号。开关电容做电阻比起电阻在同等阻值的情况下能减小50%热噪声。本发明分时切换,且采用mos开关控制电容的容抗进行不同的增益和带宽的切换,用于实现一个电路检测两种不同信号的的目的。

附图说明

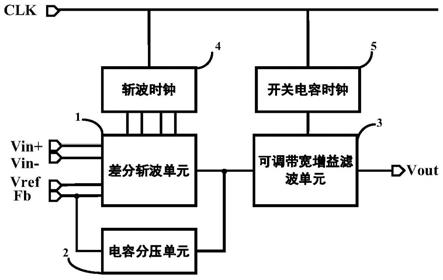

14.图1为本发明实施的一种可变带宽增益的低噪声放大器的整体示意图。

15.图2为本发明实施例提供的差分斩波单元的电路图。

16.图3为本发明实施例提供的斩波时钟电路图。

17.图4基于差分斩波单元的直流偏置电路图。

18.图5为本发明实施例的可调带宽增益滤波单元电路图。

19.图6基于可调带宽增益滤波单元的开关电容时钟电路图。

20.图7斩波电路示意图。

21.图8灰色部分为图5的等效电路示意图。

22.图中,差分斩波单元1、差分输入器101、差分反馈102、第一直流偏置器103、第二直流偏置器104、两级放大器105、第一输入斩波单元106、第二输入斩波单元107、输出斩波单元108、电容分压单元2、可调带宽增益滤波单元3、可调增益单元301、可调节带宽单元302、斩波时钟4、开关电容时钟5。

具体实施方式

23.下面结合附图和实施例,详细描述本发明的技术实施方案。

24.本发明提出一种应用于ecg信号和eeg信号的低噪声可调带宽增益的差分斩波放大器,如图1所示,本发明包括差分斩波单元1、电容分压单元2、可调带宽增益滤波单元3、斩波时钟4、开关电容时钟5。差分斩波单元1具有两个输入信号端(vin+,vin-)用于将经过第一斩波单元的输入信号,进行放大后输出,再将差分斩波单元1的输出输入到可调带宽增益滤波单元3和电容反馈单元(2)。电容分压单元2将信号分压处理后输出到差分斩波单元1的反馈端口(fb)。可调带宽增益滤波单元3将差分斩波单元1的输出信号,对ecg信号和eeg信号进行相应增益放大,和相应带宽的滤波。

25.本发明的斩波时钟4为第一输入斩波单元106,第二输入斩波单元107,输出斩波单

元108提供时钟,开关电容时钟5为开关电容提供时钟。

26.如图3所示,本发明的斩波时钟单元(4)包括第十五pmos(mp15)、第十六nmos(mn16)、补偿电容(ch)。第十五pmos(mp15)漏极连接时钟输出(clkb)并与第十六nmos(mn16)漏极连接,第十五pmos(mp15)栅极连接输入时钟(clk),第十五pmos(mp15)的源极连接vcc。第十六nmos(mn16)的源极连接gnd,第十六nmos(mn16)的栅极连接输入时钟(clk),第十六nmos(mn16)的漏极连接时钟输出(clkb)并与第十五pmos(mp15)漏极连接。补偿电容一端接在第十六nmos(mn16)的源极,另一端接在第十六nmos(mn16)的漏极。增加补偿电容的好处是,能够减小时钟馈通对clkb的影响。从而减小对斩波器输出信号的干扰。减小时钟馈通引起的误差电压δv由如下式所得:

[0027][0028]

由上式可知通过增加补偿电容ch能减小时钟馈通引起的误差电压。在clk为1.8v情况,经过处理后δv的值能减小到0.1mv。

[0029]

如图2所示,本发明的差分斩波单元1具有两个心电输入信号端,将心电信号进行频率调制和解调,解调的心电信号放大后输出到可调增益放大单元。差分斩波单元1包括差分输入器101,差分反馈102,第一直流偏置器103,第二直流偏置器104,两级放大器105,第一输入斩波单元106,第二输入斩波单元107,输出斩波单元108。

[0030]

本发明的差分输入器101包括第三pmos(mp3),第四pmos(mp4),第六pmos(mp6),第七pmos(mp7),第八pmos(mp8),其中第六pmos(mp6)提供稳定的电流,作为电流源,第三pmos(mp3),第四pmos(mp4)作为差分输入将输入的eeg信号和ecg信号从电压信号转化为电流信号,第七pmos(mp7)和第八pmos(mp8)将第三pmos(mp3),第四pmos(mp4)漏极上的电流信号转变为电压信号再拷贝给两级放大器105的输入。第三pmos(mp3)的栅极连接第二斩波单元(107)的输出信号,第三pmos(mp3)的源极连接第六pmos(m6)的漏极,第三pmos(mp3)的漏极连接第七nmos(mn7)的漏极和栅极以及第一pmos(mp1)的漏极。第四pmos(mp4)的栅极连接第二斩波单元(107)的输出信号,第四pmos(mp4)源极连接第六pmos(m6)的漏极,第四pmos(mp4)漏极连接第八nmos(mn8)的漏极和栅极以及第二pmos(mp2)的漏极。第六pmos(mp6)的栅极连接偏置电压(vbias),第六pmos(mp6)的源极连接vcc,第六pmos(mp6)的漏极连接第三pmos(mp3)和第四pmos(mp4)的源极。第七nmos(mn7)的漏极连接第三pmos(mp3)的漏极,第七nmos(mn7)的栅极连接第七nmos(mn7)的漏极并与输出斩波单元108的一个输入连接,第七nmos(mn7)源极连接gnd。第八nmos(mn8)的漏极连接第四pmos(mp4)的漏极,第八nmos(mn8)栅极连接第八nmos(mn8)的漏极并与输出斩波单元108的另一个输入连接,第八nmos(mn8)源极连接gnd。

[0031]

差分反馈器(102)包括第一pmos(mp1),第二pmos(mp2),第五pmos(mp5),差分反馈器(102)主要作用是将电容分压单元2的输出信号转化为电流信号用于调节差分输入器101信号。参考电压端(vref)控制差分斩波单元1的输出直流电压。第一pmos(mp1)的栅极连接电容分压单元2的输出经过第一斩波单元(106)的输出信号,第一pmos(mp1)的源极连接第五pmos(mp5)的漏极,第一pmos(mp1)的漏极连接第七nmos(mn7)的漏极和栅极以及第三pmos(mp3)的漏极。第二pmos(mp2)的栅极连接参考电压(vref)经过第一斩波单元(106)的另一个输出信号,第二pmos(mp2)的源极连接第五pmos(mp5)的漏极,第二pmos(mp2)的漏极

连接第八nmos(mn8)的漏极和栅极以及第四pmos(mp4)的漏极。第五pmos(mp5)的栅极连接偏置电压(vbias),第五pmos(mp5)的源极连接vcc,第五pmos(mp5)的漏极连接第一pmos(mp1)和第二pmos(mp2)的源极。

[0032]

如图2和图4所示,第一直流偏置器103包括第一nmos(mdc1)、第二nmos(mdc2),第一输入电容(cdc1),第一直流偏置器103将输入信号的本身的直流隔离后再从直流偏置器中得到电路所需的直流电压,避免了由于携带者由于身体移动导致输入直流的失配。第一输入电容(cdc1)一端连接输入信号(vin+),第一输入电容(cdc1)另一端连接第二斩波单元(107)的同相输入和第一nmos(mdc1)的漏极和栅极。第一nmos(mdc1)漏极连接第一输入电容(cdc1)的输出,第一nmos(mdc1)栅极连接第一nmos(mdc1)的漏极,源极连接第二nmos(mdc2)的漏极和栅极。第二nmos(mdc2)漏极和栅极连接第一nmos(mdc1)的源极,第二nmos(mdc2)源极连接直流偏置电压(vbias)。

[0033]

如图2和图4所示,第二直流偏置器104包括第三nmos(mdc3),第四nmos(mdc4),第二输入电容(cdc2),第二直流偏置器104作用与第一直流偏置器相同。第二输入电容(cdc2)一端连接输入信号(vin-),第二输入电容(cdc2)另一端输出给第二斩波单元(107)的反相输入。第三nmos(mdc3)漏极和栅极连接第二输入电容(cdc2)的输出,第三nmos(mdc3)源极连接第四nmos(mdc4)的漏极和栅极。第四nmos(mdc4)漏极和栅极连接第三nmos(mdc3)的源极,第四nmos(mdc4)源极连接直流偏置电压(vbias)。

[0034]

两级放大器105包括第九nmos(mn9),第十nmos(mn10),第十四nmos(mn14),第十一pmos(mp11),第十二pmos(mp12),第十三pmos(mp13),第三电容(cc)。两级放大器将经过输出斩波单元108后的差分输入器101与差分反馈102的输出电流信号转化为电压信号再放大,再将输出给电容分压单元2和可调带宽增益滤波单元3。差分斩波单元1的输入输出关系为:

[0035][0036]

由此公式可以看出输出不受输入阻抗的影响。

[0037]

第九nmos(mn9)源极连接gnd,第九nmos(mn9)栅极连接输出斩波单元108的正相输出,第九nmos(mn9)漏极连接第十一pmos(mp11)的漏极。第十nmos(mn10)源极连接gnd,第十nmos(mn10)栅极连接输出斩波单元108的反相输出,第十nmos(mn10)漏极连接第十二pmos(mp12)的漏极和栅极。第十一pmos(mp11)源极连接vcc,第十一pmos(mp11)栅极连接第十二pmos(mp12)的栅极和漏极,第十一pmos(mp11)漏极连接第九nmos(mn9)的漏极、第十三pmos(mp13)的栅极和第三电容(cc)的一端。第十二pmos(mp12)源极连接vcc,第十二pmos(mp12)栅极连接第十二pmos(mp12)的漏极并与第十nmos(mn10)的漏极连接。第十三pmos(mp13)源极连接vcc,第十三pmos(mp13)漏极连接第十四nmos(mn14)的漏极,第十三pmos(mp13)栅极连接第三电容(cc)的一端和第十一pmos(mp11)的漏极。第十四nmos(mn14)漏极连接第十三pmos(mp13)的漏极,第十四nmos(mn14)源极连接gnd,第十四nmos(mn14)栅极连接vbias。第三电容(cc)一端连接第十一pmos(m11)的漏极,第三电容(cc)另一端连接第十三pmos(mp13)的漏极。

[0038]

第一输入斩波单元106将差分反馈器(102)的输入信号调制到高频,与低频噪声分离。

[0039]

第二输入斩波单元107将差分输入器101的输入信号调制到高频,与低频噪声分离。

[0040]

输出斩波单元108是将有用信号解调回基带还原信号,将低频噪声调制到高频与有用信号分离,再输入给两级放大器105进行放大。

[0041]

第一输入斩波单元106、第二输入斩波单元107、输出斩波单元108为现有电路,其电路结构可以如图7所示电路。

[0042]

如图5所示,本发明的可调带宽增益滤波单元3包括可调增益单元(301)、可调带宽单元(302)和一个用于有源滤波器的运算放大器。

[0043]

可调增益单元(301)包括第一开关nmos管(msw1),第二开关nmos管(msw2),第六电容(c6)、第七电容(c7)、第八电容(c8)。图8中r3、r4并非实际存在,是为了说明方便而进行的等效。r3为为一端接运放反相输入端,另一端接gnd的等效电容的总阻抗,r4为一端接运放输出端,另一端接反相输入端等效电容的总阻抗。

[0044]

第一开关nmos(msw1)源极连接gnd并与第六电容(c6)的一端连接,第一开关nmos(msw1)栅极连接外接控制信号,第一开关nmos(msw1)漏极连接第二开关nmos(msw2)的漏极并与第八电容(c8)的一端链接。第二开关nmos(msw2)漏极接在第八电容(c8)的一端,第二开关nmos(msw2)栅极连接外接控制反相信号(φ),第二开关nmos(msw2)源极连接运放的输出。第六电容一端连接运放的反相输入并与第八电容(c8)的一端连接,第六电容另一端接第一开关nmos(msw1)的源极和gnd。第七电容(c7)一端接在运放的反相输入端以及c6和c8的一端,第七电容(c7)另一端运放的输出端。第八电容一端接在第二开关nmos(msw2)的漏极,第八电容另一端接在运放反相输入端以及第六电容(c6)和第七电容(c7)的交点。

[0045]

可调带宽单元(302),包括第三开关电容nmos管(msw3),第四开关电容nmos管(msw4),第五开关电容nmos管(msw5),第六开关电容nmos(msw6),第七开关电容nmos管(msw7),第八开关电容nmos管(msw8),第九开关电容nmos管(msw9),第十开关电容nmos(msw10),第一开关电容(csw1),第二开关电容(csw2),第十一开关nmos管(msw11),第十二开关nmos管(msw12),第九电容(c9),第十电容(c10),第十一电容(c11)。图8中r1、r2、c1并非实际存在,是为了说明方便而进行的等效。c2可以等效为c10。r1为开关电容1(csw1)的等效电阻值,r2为开关电容2(csw2)的等效电阻值,c1为一端接gnd,另一端接运放同相输入端的等效电容值。c2为一端接运放输出端,另一端接r1,r2交点的等效电容值。

[0046]

第三开关电容nmos管(msw3)漏极连接差分斩波单元1的输出信号,第三开关电容nmos管(msw3)栅极连接开关电容时钟单元(5)的时钟信号clk1,第三开关电容nmos管(msw3)源极连接第一开关电容(csw1)的一端以及第四开关电容nmos(msw4)的漏极。

[0047]

第四开关电容nmos管(msw4)源极连接gnd,第四开关电容nmos管(msw4)栅极连接开关电容时钟单元(5)的时钟信号clkb1,第四开关电容nmos管(msw4)漏极连接第一开关电容(csw1)的一端以及第三开关nmos(msw3)的源极。

[0048]

第五开关电容nmos管(msw5)漏极连接第一开关电容(csw1)的一端,第五开关电容nmos管(msw5)栅极连接开关电容时钟单元(5)的时钟信号clkb1,第五开关电容nmos管(msw5)源极连接第七开关电容nmos(msw7)的漏极以及第十电容(c10)的一端。

[0049]

第六开关电容nmos管(msw6)漏极连接第一开关电容(csw1)的一端,第六开关电容nmos管(msw6)栅极连接开关电容时钟单元(5)的时钟信号clk1,第六开关电容nmos管

(msw6)源极连接gnd。

[0050]

第七开关电容nmos管(msw7)漏极连接第五开关nmos(msw5)的源极和第十电容(c10)的一端,第七开关电容nmos管(msw7)栅极连接开关电容时钟单元(5)的时钟信号clkb1,第七开关电容nmos管(msw7)源极连接第二开关电容(csw2)的一端以及第八开关电容nmos(msw8)的漏极。

[0051]

第八开关电容nmos管(msw8)源极连接gnd,第八开关电容nmos管(msw8)栅极连接开关电容时钟单元(5)的时钟信号clk1,第八开关电容nmos管(msw8)漏极连接第二开关电容(csw2)的一端以及第七开关nmos(msw7)的源极。

[0052]

第九开关电容nmos管(msw9)漏极连接第二开关电容(csw2)的一端和第十开关电容nmos管(msw10)的漏极,第九开关电容nmos管(msw9)栅极连接开关电容时钟单元(5)的时钟信号clk1,第九开关电容nmos管(msw9)源极连接第十一开关电容nmos(msw11)管的漏极。

[0053]

第十开关电容nmos管(msw10)漏极连接第二开关电容(csw2)的一端以及第九开关电容nmos管(msw9)的漏极,第十开关电容nmos管(msw10)栅极连接开关电容时钟单元(5)的时钟信号clkb1,第十开关电容nmos管(msw10)源极连接gnd。

[0054]

第十一开关nmos管(msw11)漏极连接第九电容(c9)的一端、第九开关电容nmos管(msw9)的源极和运放的正相输入,第十一开关nmos管(msw11)栅极外接控制信号第十一开关nmos管(msw11)源极接第十一电容(c11)的一端。

[0055]

第十二开关nmos管(msw12)漏极连接第十一开关nmos管(msw11)的源极以及第十一电容(c11)的一端,第十二开关nmos管(msw12)栅极外接控制信号φ,第十二开关nmos管(msw12)源极接第十一电容(c11)的另一端和gnd。

[0056]

第一开关电容(csw1)一端连接第三开关电容nmos管(msw3)的源极和第四开关电容管nmos(msw4)的漏极,另一端连接第五开关电容nmos管(msw5)的漏极和第六开关电容nmos管(msw6)的漏极。

[0057]

第二开关电容(csw2)一端连接第七开关电容nmos管(msw7)的源极和第八开关电容nmos管(msw8)的漏极,另一端连接第九开关电容nmos(msw9)的漏极和十开关电容nmos(msw10)的漏极。

[0058]

第九电容(c9)一端连接第九开关nmos管(msw9)的源极以及第十一开关nmos管(msw11)的漏极、运放的正相输入,另一端接gnd。

[0059]

第十电容(c10)一端连接第五开关nmos管(msw5)的源极和第七开关nmos管(msw7)的漏极,另一端接运放的输出。

[0060]

第十一电容(c11)一端连接第十一开关nmos管(msw11)的源极和第十二开关nmos(msw12)管的漏极,另一端接gnd。

[0061]

如图2所示,本发明的电容分压单元2包括第五电容(c5),第四电容(c4)。第五电容(c5)一端连接第十四nmos(mn14)漏极,另一端连接第一输入斩波单元106的输入。第四电容(c4)一端连接第一输入斩波单元106的输入,另一端连接gnd。

[0062]

如图6所示,本发明的开关电容时钟单元(5)包括第一输入非门(not1),第二输入非门(not2),第三输入非门(not3),第四输入非门(not4),第五输入非门(not5),第一或非门(nor1),第二或非门(nor2),第六输出非门(not6),第七输出非门(not7),第八输出非门(not8),第九输出非门(not9),开关电容时钟单元(5)产生两个非重叠时钟,输入信号为

clk,产生一对幅值为vdd,高电平非重叠的时钟信号clk1和clkb1。

[0063]

第一输入非门(not1)输入端连接clk,输出端连接第四输入非门(not4)的输入端。第二输入非门(not2)输入端连接clk,输出端连接第三输入非门(not3)的输入端。第三输入非门(not3)输出端连接第一或非门(nor1)第一输入端。第四输入非门(not4)输入端连接第一输入非门(not1)的输出,输出端连接第五输入非门(not5)的输入端。第五输入非门(not5)输出端连接第二或非门(nor2)的第二输入端。第一或非门(nor1)第二输入连接第九输出非门(not9)的输出。第二或非门(nor2)第一输入连接第七输出非门(not7)的输出。第六输出非门(not6)输入端连接第一或非门(nor1)的输出端,输出端连接第七输出非门(not7)的输入。第七输出非门(not7)输入端连接第六输出非门(not6),输出端输出时钟信号clk1。第八输出非门(not8),入端连接第二或非门(nor2)的输出端,输出端连接第九输出非门(not9)的输入。第九输出非门(not9)输入端连接第八输出非门(not8),输出端输出时钟信号clkb1。

[0064]

本说明书中,pmos管未经说明衬底均连接vcc,nmos管衬底均连接gnd。

[0065]

本发明的低频信号由第一输入斩波单元106,第二输入斩波单元107在斩波时钟4的控制下进行工作:

[0066][0067]

进行调制得到:

[0068][0069]

上式的s

vi

(f)为原信号叠加噪声后经过输入斩波单元调制后的信号,sn(f)为噪声在频域的表示,s

vin

(f-f

chop

)为原信号经过输入斩波单元调制后,所变成的奇次谐波。f

chop

是斩波频率:

[0070]fchop

≥k

·

bw

signal

+f

corner

[0071]

上式中f

chop

为斩波频率即斩波时钟所需要的频率,k为常数通常k≥2,bw

signal

为信号带宽即输入原始信号的带宽,f

corner

为噪声的转折频率。从而将噪声与信号分离,再由输出斩波单元108将信号调回基带,噪声调到高频后再由后一级进行处理,该单元能有效去除闪烁噪声。

[0072]

第一直流偏置器103、第二直流偏置器(104其提供的稳定直流电压为:v

out

=k

·vbias

k值为v

out

与随v

bias

改变的变化率,其中k值随nmos管工艺w/l改变,或者由vbias的大小决定,vbias是外接的偏置电压,用于控制直流偏置器的输出直流电压。

[0073]

如图8所示,本发明的可调带宽增益滤波单元3连接到的可调带宽滤波单元,将对应信号放大合适增益后输出到可调带宽滤波单元。可调带宽增益滤波单元3将对应的放大信号进行不同通带低通滤波后输出信号。可调带宽增益滤波单元3使用sallen-key低通滤波的结构得到以下参数:

[0074]

增益:

[0075]

上述r3为一端接运放反相输入端,另一端接gnd的等效电容的总阻抗,r4一端接运

放输出端,另一端接反相输入端等效电容的总阻抗。附图8中的灰色代号部分代表该部分的等效电阻或电容值,其并不是实际存在的电阻。

[0076]

截止频率:

[0077]

上述r1为开关电容1(csw1)的等效电阻值,r2为开关电容2(csw2)的等效电阻,c1为一端接gnd,另一端接运放同相输入端的等效电容值。c2为一端接运放输出端,另一端接r1,r2交点的等效电容值。

[0078]

在此结构上用开关电容做电阻,开关电容的等效阻值为:f代表开关电容的投入信号频率,c为电容值。

[0079]

调整增益和带宽是用外接的控制信号控制,达到分时复用的效果。这样本发明利用同一个电路测量两种不同的信号,该电路是分时复用电路,若想同时测量需要对本发明的电路进行多通道改进。

[0080]

若为高电平,该模式下处理eeg信号:

[0081]

增益为:

[0082]

截止频率为:

[0083]

若为低电平,该模式下处理ecg信号:

[0084]

增益为:

[0085]

上述c6为一端接gnd,另一端接运放同相输入端的等效电容值。c7、c8为一端接运放输出端,另一端接r1,r2交点的等效电容值。

[0086]

截止频率为:上述公式csw1和csw2为开关电容,c9为一端接gnd,另一端接运放同相输入端的电容。c10为一端接运放输出端,另一端接第五开关电容nmos(msw5)的源极和第六开关电容nmos(msw6)漏极的电容。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1