高速比较器系统的制作方法

1.本发明涉及一种高速比较器系统。

背景技术:

2.高速比较器可以广泛应用于如数字稳压器、模拟对数字转换器等电路模块,以监测输入电压的差值,输出数字电平。伴随着移动装置的频率频率(clock)逐年提升,对于监测信号响应速度的要求亦不断提高,故高速比较器的应用前景十分看好。因此,有必要提出一种全新的解决方案,以改良传统高速比较器的各种缺陷。

技术实现要素:

3.在优选实施例中,本发明提出一种高速比较器系统,包括比较器主体、稳压器、共模改良电路、模拟对数字转换器以及匹配校正电路。其中,比较器主体包括:电压输入电路,接收第一输入电压和第二输入电压,并耦接第一控制节点和第二控制节点;稳压电流源,输出第一电流至该第一控制节点,并输出第二电流至该第二控制节点;稳压电阻组件,耦接于该第一控制节点和该第二控制节点之间;以及差分输出电路,耦接该第一控制节点和该第二控制节点,并产生第一输出电压和第二输出电压。

4.相较于传统设计,本发明所提的高速比较器系统至少具有下列优点:(1)响应速度快、精确度高,结构简单;(2)对制程变异,如电源电压、温度波动等皆不敏感;(3)无论高速、低速信号变化均可监测;(4)速度及功耗可调节;(5)适合各种应用条件,不用重复校准;以及(6)输出至不同电压域的比较结果,但不会大幅增加功耗。

附图说明

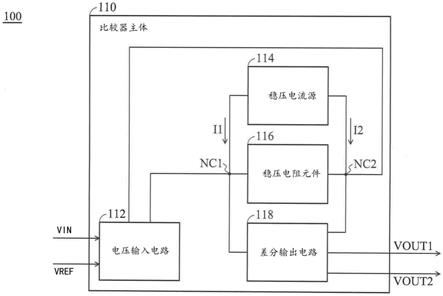

5.图1为本发明一实施例所述的高速比较器系统100的示意图。

6.图2为本发明一实施例所述的比较器主体210的示意图。

7.图3为本发明一实施例所述的高速比较器系统300的示意图。

8.图4为本发明一实施例所述的稳压器320的示意图。

9.图5为本发明一实施例所述的共模改良电路330的示意图。

10.图6为本发明一实施例所述的模拟对数字转换器340的示意图。

11.图7为本发明一实施例所述的匹配校正电路350的示意图。

12.图8为本发明一实施例所述的比较器主体810的示意图。

13.图9为本发明一实施例所述的稳压器820的示意图。

14.图10为本发明一实施例所述的共模改良电路830的示意图。

15.图11为本发明一实施例所述的模拟对数字转换器840的示意图。

具体实施方式

16.为让本发明的目的、特征和优点能更明显易懂,下文特举出本发明的具体实施例,

并配合附图,作详细说明如下。

17.在说明书及权利要求书当中使用了某些词汇来指称特定的组件。本领域技术人员应可理解,硬件制造商可能会用不同的名词来称呼同一个组件。本说明书及权利要求书并不以名称的差异来作为区分组件的方式,而是以组件在功能上的差异来作为区分的准则。在通篇说明书及权利要求书当中所提及的“包含”及“包括”一词为开放式的用语,故应解释成“包含但不仅限定于”。“大致”一词则是指在可接受的误差范围内,本领域技术人员能够在一定误差范围内解决所述技术问题,达到所述基本的技术效果。此外,“耦接”一词在本说明书中包含任何直接及间接的电性连接手段。因此,若文中描述一第一装置耦接一第二装置,则代表该第一装置可直接电性连接至该第二装置,或经由其它装置或连接手段而间接地连接至该第二装置。

18.图1为本发明一实施例所述的高速比较器系统100的示意图。如图1所示,高速比较器系统100至少包括一比较器主体(comparator body)110,该比较器主体110包括电压输入电路(differential input circuit)112、稳压电流源(regulated current source)114、稳压电阻组件(regulated resistive element)116以及差分输出电路(differential output circuit)118。

19.大致而言,电压输入电路112可接收第一输入电压vin和第二输入电压vref,并可耦接第一控制节点nc1和第二控制节点nc2,其中,第二输入电压vref为一参考电压。稳压电流源114可输出第一电流i1至第一控制节点nc1,并可输出第二电流i2至第二控制节点nc2。例如,第二电流i2可大致等同于第一电流i1。稳压电阻组件116可耦接于第一控制节点nc1和第二控制节点nc2之间。差分输出电路118可耦接第一控制节点nc1和第二控制节点nc2,并可产生差分的第一输出电压vout1和第二输出电压vout2。

20.以下将介绍高速比较器系统100的各种细部结构及变化配置。必须理解的是,这些附图和叙述仅为举例,而非用于限制本发明。

21.图2为本发明一实施例所述的比较器主体210的示意图。在图2的实施例中,比较器主体210包括电压输入电路212、稳压电流源214、稳压电阻组件216以及差分输出电路218。

22.电压输入电路212包括第一n型晶体管mn1、第二n型晶体管mn2以及第三n型晶体管mn3。例如,本说明书中每一n型晶体管可各自为一n型金属氧化物半导体场效应晶体管,但亦不仅限于此。第一n型晶体管mn1具有控制端、第一端以及第二端,其中第一n型晶体管mn1的控制端用于接收第一输入电压vin,第一n型晶体管mn1的第一端耦接第一节点n1,而第一n型晶体管mn1的第二端耦接第一控制节点nc1。第二n型晶体管mn2具有控制端、第一端以及第二端,其中第二n型晶体管mn2的控制端用于接收第二输入电压vref,第二n型晶体管mn2的第一端耦接第一节点n1,而第二n型晶体管mn2的第二端耦接第二控制节点nc2。第三n型晶体管mn3具有控制端、第一端以及第二端,其中第三n型晶体管mn3的控制端耦接第一偏压节点nb1,第三n型晶体管mn3的第一端耦接接地电压vss(例如:0v),而第三n型晶体管mn3的第二端耦接第一节点n1。

23.稳压电流源214包括第一p型晶体管mp1和第二p型晶体管mp2。例如,本说明书中每一p型晶体管可各自为一p型金属氧化物半导体场效应晶体管,但亦不仅限于此。第一p型晶体管mp1具有控制端、第一端以及第二端,其中第一p型晶体管mp1的控制端耦接第二偏压节点nb2,第一p型晶体管mp1的第一端耦接第一供应电压vdd1,而第一p型晶体管mp1的第二端

耦接第一控制节点nc1以输出第一电流i1。第二p型晶体管mp2具有控制端、第一端以及第二端,其中第二p型晶体管mp2的控制端耦接第二偏压节点nb2,第二p型晶体管mp2的第一端耦接第一供应电压vdd1,而第二p型晶体管mp2的第二端耦接第二控制节点nc2以输出第二电流i2。

24.稳压电阻组件216包括第一电阻器r1和第二电阻器r2。第一电阻器r1具有第一端和第二端,其中第一电阻器r1的第一端耦接第一控制节点nc1,而第一电阻器r1的第二端耦接第二节点n2。第二电阻器r2具有第一端和第二端,其中第二电阻器r2的第一端耦接第二控制节点nc2,而第二电阻器r2的第二端耦接第二节点n2。其中,第一电阻器r1和第二电阻器r2也可合并为一个电阻器耦接在第一控制节点nc1与第二控制节点nc2之间。

25.差分输出电路218包括第一电容器c1、第二电容器c2、第三p型晶体管mp3、第四p型晶体管mp4、第五p型晶体管mp5、第六p型晶体管mp6、第四n型晶体管mn4、第五n型晶体管mn5、第六n型晶体管mn6以及第七n型晶体管mn7。

26.第一电容器c1具有第一端和第二端,其中第一电容器c1的第一端耦接第一控制节点nc1,而第一电容器c1的第二端耦接第三节点n3。第三p型晶体管mp3具有控制端、第一端以及第二端,其中第三p型晶体管mp3的控制端耦接第三节点n3,第三p型晶体管mp3的第一端耦接第一控制节点nc1,而第三p型晶体管mp3的第二端耦接第三节点n3。第四n型晶体管mn4具有控制端、第一端以及第二端,其中第四n型晶体管mn4的控制端耦接第三节点n3,第四n型晶体管mn4的第一端耦接接地电压vss,而第四n型晶体管mn4的第二端耦接第三节点n3。第四p型晶体管mp4具有控制端、第一端以及第二端,其中第四p型晶体管mp4的控制端耦接第四节点n4,第四p型晶体管mp4的第一端耦接第一控制节点nc1,而第四p型晶体管mp4的第二端耦接第一输出节点nout1以输出第一输出电压vout1。第五n型晶体管mn5具有控制端、第一端以及第二端,其中第五n型晶体管mn5的控制端耦接第四节点n4,第五n型晶体管mn5的第一端耦接接地电压vss,而第五n型晶体管mn5的第二端耦接第一输出节点nout1。

27.第二电容器c2具有第一端和第二端,其中第二电容器c2的第一端耦接第二控制节点nc2,而第二电容器c2的第二端耦接第四节点n4。第五p型晶体管mp5具有控制端、第一端以及第二端,其中第五p型晶体管mp5的控制端耦接第四节点n4,第五p型晶体管mp5的第一端耦接第二控制节点nc2,而第五p型晶体管mp5的第二端耦接第四节点n4。第六n型晶体管mn6具有控制端、第一端以及第二端,其中第六n型晶体管mn6的控制端耦接第四节点n4,第六n型晶体管mn6的第一端耦接接地电压vss,而第六n型晶体管mn6的第二端耦接第四节点n4。第六p型晶体管mp6具有控制端、第一端以及第二端,其中第六p型晶体管mp6的控制端耦接第三节点n3,第六p型晶体管mp6的第一端耦接第二控制节点nc2,而第六p型晶体管mp6的第二端耦接第二输出节点nout2以输出第二输出电压vout2。第七n型晶体管mn7具有控制端、第一端以及第二端,其中第七n型晶体管mn7的控制端耦接第三节点n3,第七n型晶体管mn7的第一端耦接接地电压vss,而第七n型晶体管mn7的第二端耦接第二输出节点nout2。

28.在一些实施例中,第三p型晶体管mp3和第四n型晶体管mn4可以提供一偏压电压,其位于第六p型晶体管mp6和第七n型晶体管mn7所形成的反相器的一翻转阈值附近。另外,第五p型晶体管mp5和第六n型晶体管mn6可以提供另一偏压电压,其位于第四p型晶体管mp4和第五n型晶体管mn5所形成的另一反相器的另一翻转阈值附近。在此设计下,输入信号的差模部分将能快速地被响应。第一电容器c1和第二电容器c2可加速高频信号比较。第一电

阻器r1和第二电阻器r2可用于限制两侧第一控制节点nc1和第二控制节点nc2间的电压差。即使输入电压的摆幅(swing)较大,也可快速恢复,不致对比较速度造成影响。还有值得一提的是,比较器主体210的左右两侧结构对称,因此可以实现差分输出、且抗共模波动的能力较强。

29.图3为本发明一实施例所述的高速比较器系统300的示意图。在图3的实施例中,除了比较器主体110(或210)以外,高速比较器系统300还可包括稳压器(voltage regulator)320、共模改良电路(common-mode improvement circuit)330、模拟对数字转换器(analog-to-digital converter,adc)340以及匹配校正电路(matching calibration circuit)350,其详细结构及电路连接方式可如下所述。

30.其中,该高速比较器系统300的翻转阈值不同于图2所示的两组反相器的翻转阈值,但可快速响应于该两组反相器的翻转阈值,且该两组反相器的翻转阈值可能因电路失配(工艺制程所致)而有所不同。

31.图4为本发明一实施例所述的稳压器320的示意图。稳压器320包括运算放大器(operational amplifier)322、第七p型晶体管mp7、第八p型晶体管mp8,以及第八n型晶体管mn8。运算放大器322具有正输入端、负输入端以及输出端,其中运算放大器322的正输入端用于接收一共模电压vcom,运算放大器322的负输入端耦接第七节点n7,而运算放大器322的输出端耦接第二偏压节点nb2。第七p型晶体管mp7具有控制端、第一端以及第二端,其中第七p型晶体管mp7的控制端耦接第二偏压节点nb2,第七p型晶体管mp7的第一端耦接第一供应电压vdd1,而第七p型晶体管mp7的第二端耦接第七节点n7。第八p型晶体管mp8具有控制端、第一端以及第二端,其中第八p型晶体管mp8的控制端耦接第八节点n8,第八p型晶体管mp8的第一端耦接第七节点n7,而第八p型晶体管mp8的第二端耦接第八节点n8。第八n型晶体管mn8具有控制端、第一端以及第二端,其中第八n型晶体管mn8的控制端耦接第八节点n8,第八n型晶体管mn8的第一端耦接接地电压vss,而第八n型晶体管mn8的第二端耦接第八节点n8。

32.在一些实施例中,稳压器320可藉由共模电压vcom来钳制第一控制节点nc1和第二控制节点nc2处的电压。即使电源(第一供应电压vdd1)有波动,高速比较器系统300的翻转阈值仍可大致维持不变。因此,可以通过共模电压vcom的设置来调节系统的功耗及速度。

33.图5为本发明一实施例所述的共模改良电路330的示意图。共模改良电路330包括第九p型晶体管mp9、第十p型晶体管mp10、第十一p型晶体管mp11、第九n型晶体管mn9、第十n型晶体管mn10、第十一n型晶体管mn11、第十二n型晶体管mn12、第十三n型晶体管mn13,以及第十四n型晶体管mn14。

34.第九p型晶体管mp9具有控制端、第一端以及第二端,其中第九p型晶体管mp9的控制端耦接第二偏压节点nb2,第九p型晶体管mp9的第一端耦接第一供应电压vdd1,而第九p型晶体管mp9的第二端耦接第九节点n9。第十p型晶体管mp10具有控制端、第一端以及第二端,其中第十p型晶体管mp10的控制端耦接第二输出节点nout2,第十p型晶体管mp10的第一端耦接第九节点n9,而第十p型晶体管mp10的第二端耦接第十节点n10。第十一p型晶体管mp11具有控制端、第一端以及第二端,其中第十一p型晶体管mp11的控制端耦接第一输出节点nout1,第十一p型晶体管mp11的第一端耦接第九节点n9,而第十一p型晶体管mp11的第二端耦接第十一节点n11。

35.第九n型晶体管mn9具有控制端、第一端以及第二端,其中第九n型晶体管mn9的控制端耦接第一输出节点nout1,第九n型晶体管mn9的第一端耦接第二输出节点nout2,而第九n型晶体管mn9的第二端耦接第一输出节点nout1。第十n型晶体管mn10具有控制端、第一端以及第二端,其中第十n型晶体管mn10的控制端耦接第二输出节点nout2,第十n型晶体管mn10的第一端耦接第一输出节点nout1,而第十n型晶体管mn10的第二端耦接第二输出节点nout2。第十一n型晶体管mn11具有控制端、第一端以及第二端,其中第十一n型晶体管mn11的控制端耦接第十一节点n11,第十一n型晶体管mn11的第一端耦接第十节点n10,而第十一n型晶体管mn11的第二端耦接至第十一节点n11。第十二n型晶体管mn12具有控制端、第一端以及第二端,其中第十二n型晶体管mn12的控制端耦接第十节点n10,第十二n型晶体管mn12的第一端耦接第十一节点n11,而第十二n型晶体管mn12的第二端耦接第十节点n10。第十三n型晶体管mn13具有控制端、第一端以及第二端,其中第十三n型晶体管mn13的控制端耦接第十节点n10,第十三n型晶体管mn13的第一端耦接接地电压vss,而第十三n型晶体管mn13的第二端耦接第十节点n10。第十四n型晶体管mn14具有控制端、第一端以及第二端,其中第十四n型晶体管mn14的控制端耦接第十一节点n11,第十四n型晶体管mn14的第一端耦接接地电压vss,而第十四n型晶体管mn14的第二端耦接第十一节点n11。

36.在一些实施例中,共模改良电路330可将前一级电路的比较结果的共模部分提高,以利于后一级电路进行比较。另外,第九n型晶体管mn9、第十n型晶体管mn10的加入有助于限制本级输入信号的摆幅,而第十一n型晶体管mn11以及第十二n型晶体管mn12的加入有助于限制本级输出信号的摆幅。

37.图6为本发明一实施例所述的模拟对数字转换器340的示意图。模拟对数字转换器340包括第十二p型晶体管mp12、第十三p型晶体管mp13、第十四p型晶体管mp14、第十五n型晶体管mn15、第十六n型晶体管mn16以及第十七n型晶体管mn17。第十二p型晶体管mp12具有控制端、第一端以及第二端,其中第十二p型晶体管mp12的控制端耦接第十二节点n12,第十二p型晶体管mp12的第一端耦接第二供应电压vdd2,而第十二p型晶体管mp12的第二端耦接第十二节点n12。第十三p型晶体管mp13具有控制端、第一端以及第二端,其中第十三p型晶体管mp13的控制端耦接第十二节点n12,第十三p型晶体管mp13的第一端耦接第二供应电压vdd2,而第十三p型晶体管mp13的第二端耦接第十三节点n13。第十五n型晶体管mn15具有控制端、第一端以及第二端,其中第十五n型晶体管mn15的控制端耦接第十一节点n11,第十五n型晶体管mn15的第一端耦接接地电压vss,而第十五n型晶体管mn15的第二端耦接第十二节点n12。第十六n型晶体管mn16具有控制端、第一端以及第二端,其中第十六n型晶体管mn16的控制端耦接第十节点n10,第十六n型晶体管mn16的第一端耦接接地电压vss,而第十六n型晶体管mn16的第二端耦接第十三节点n13。第十四p型晶体管mp14具有控制端、第一端以及第二端,其中第十四p型晶体管mp14的控制端耦接第十三节点n13,第十四p型晶体管mp14的第一端耦接第二供应电压vdd2,而第十四p型晶体管mp14的第二端耦接最终输出节点noutf以输出最终输出电压voutf。第十七n型晶体管mn17具有控制端、第一端以及第二端,其中第十七n型晶体管mn17的控制端耦接第十三节点n13,第十七n型晶体管mn17的第一端耦接接地电压vss,而第十七n型晶体管mn17的第二端耦接最终输出节点noutf。

38.在一些实施例中,第二供应电压vdd2小于前述第一供应电压vdd1。模拟对数字转换器340可将高电压域的比较结果转至低电压域。由于前一级电路的输出结果(作用于第十

一节点n11以及第十节点n10)的摆幅相对较大,也就是第十五n型晶体管mn15以及第十六n型晶体管mn16接收的控制信号摆幅较大,而使模拟对数字转换器340可提供相对较小的静态功耗。

39.图7为本发明一实施例所述的匹配校正电路350的示意图。匹配校正电路350包括逻辑电路352、多个第一校正器354以及多个第二校正器356。逻辑电路352可根据最终输出电压voutf来产生多个第一校正电压vl1和多个第二校正电压vl2。逻辑电路352的实际结构及运算方式皆可根据不同需求而进行调整。

40.该等第一校正器354彼此并联,该等第一校正器354的每一个包括第一校正n型晶体管mcn1和第二校正n型晶体管mcn2。例如,本说明书中每一校正n型晶体管可各自为n型金属氧化物半导体场效应晶体管,但亦不仅限于此。第一校正n型晶体管mcn1具有控制端、第一端以及第二端,其中第一校正n型晶体管mcn1的控制端用于接收该等第一校正电压vl1中的一个,第一校正n型晶体管mcn1的第一端耦接第一连接节点ne1,而第一校正n型晶体管mcn1的第二端耦接第一控制节点nc1。第二校正n型晶体管mcn2具有控制端、第一端以及第二端,其中第二校正n型晶体管mcn2的控制端耦接第一偏压节点nb1,第二校正n型晶体管mcn2的第一端耦接接地电压vss,而第二校正n型晶体管mcn2的第二端耦接第一连接节点ne1。在一些实施例中,该等第一校正器354的总数量可至少为10,以调整关于第一控制节点nc1的各种因制程、温度、电源电压的差异而产生的不匹配(mismatch)情况。

41.该等第二校正器356彼此并联,该等第二校正器356的每一个包括第三校正n型晶体管mcn3和第四校正n型晶体管mcn4。第三校正n型晶体管mcn3具有控制端、第一端以及第二端,其中第三校正n型晶体管mcn3的控制端用于接收该等第二校正电压vl2中的一个,第三校正n型晶体管mcn3的第一端耦接第二连接节点ne2,而第三校正n型晶体管mcn3的第二端耦接第二控制节点nc2。第四校正n型晶体管mcn4具有控制端、第一端以及第二端,其中第四校正n型晶体管mcn4的控制端耦接第一偏压节点nb1,第四校正n型晶体管mcn4的第一端耦接接地电压vss,而第四校正n型晶体管mcn4的第二端耦接第二连接节点ne2。在一些实施例中,该等第二校正器356的总数量可至少为10,以调整关于第二控制节点nc2的各种因制程、温度、电源电压的差异而产生的不匹配情况。

42.在一些实施例中,匹配校正电路350可根据比较器主体210的比较结果,将第一控制节点nc1和第二控制节点nc2两者中电压偏高者经由分支电流路径耦接接地电压vss,此可消除因制程、温度、电源电压的差异而产生的电路不匹配所带来的对比较精确的影响。

43.必须注意的是,本发明的电路方块并不仅限于以上结构。在另一些实施例中,高速比较器系统300可包括比较器主体810、稳压器820、共模改良电路830以及模拟对数字转换器840,其具有相似的操作原理,详细将如下列实施例所述。

44.图8为本发明一实施例所述的比较器主体810的示意图。在图8的实施例中,比较器主体810包括电压输入电路812、稳压电流源814、稳压电阻组件816以及差分输出电路818。

45.电压输入电路812包括第一n型晶体管mn1、第二n型晶体管mn2以及第三n型晶体管mn3。第一n型晶体管mn1具有控制端、第一端以及第二端,其中第一n型晶体管mn1的控制端用于接收第一输入电压vin,第一n型晶体管mn1的第一端耦接第一节点n1,而第一n型晶体管mn1的第二端耦接第二节点n2。第二n型晶体管mn2具有控制端、第一端以及第二端,其中第二n型晶体管mn2的控制端用于接收第二输入电压vref,第二n型晶体管mn2的第一端耦接

第一节点n1,而第二n型晶体管mn2的第二端耦接第三节点n3。第三n型晶体管mn3具有控制端、第一端以及第二端,其中第三n型晶体管mn3的控制端耦接第一偏压节点nb1,第三n型晶体管mn3的第一端耦接接地电压vss,而第三n型晶体管mn3的第二端耦接第一节点n1。

46.稳压电流源814包括第一p型晶体管mp1、第二p型晶体管mp2、第三p型晶体管mp3以及第四p型晶体管mp4。第一p型晶体管mp1具有控制端、第一端以及第二端,其中第一p型晶体管mp1的控制端耦接第二偏压节点nb2,第一p型晶体管mp1的第一端耦接第一供应电压vdd1,而第一p型晶体管mp1的第二端耦接第二节点n2。第二p型晶体管mp2具有控制端、第一端以及第二端,其中第二p型晶体管mp2的控制端耦接第二偏压节点nb2,第二p型晶体管mp2的第一端耦接第一供应电压vdd1,而第二p型晶体管mp2的第二端耦接第三节点n3。第三p型晶体管mp3具有控制端、第一端以及第二端,其中第三p型晶体管mp3的控制端耦接第三偏压节点nb3,第三p型晶体管mp3的第一端耦接第二节点n2,而第三p型晶体管mp3的第二端耦接第一控制节点nc1以输出第一电流i1。第四p型晶体管mp4具有控制端、第一端以及第二端,其中第四p型晶体管mp4的控制端耦接第三偏压节点nb3,第四p型晶体管mp4的第一端耦接第三节点n3,而第四p型晶体管mp4的第二端耦接第二控制节点nc2以输出第二电流i2。

47.稳压电阻组件816包括第一电阻器r1和第二电阻器r2。第一电阻器r1具有第一端和第二端,其中第一电阻器r1的第一端耦接第一控制节点nc1,而第一电阻器r1的第二端耦接第四偏压节点nb4。第二电阻器r2具有第一端和第二端,其中第二电阻器r2的第一端耦接第二控制节点nc2,而第二电阻器r2的第二端耦接第四偏压节点nb4。其中,第一电阻器r1和第二电阻器r2也可合并为一个电阻器耦接在第一控制节点nc1与第二控制节点nc2之间。

48.差分输出电路818包括第五p型晶体管mp5、第六p型晶体管mp6、第七p型晶体管mp7、第八p型晶体管mp8、第九p型晶体管mp9、第十p型晶体管mp10、第四n型晶体管mn4、第五n型晶体管mn5、第六n型晶体管mn6、第七n型晶体管mn7、第八n型晶体管mn8、第九n型晶体管mn9以及第三电阻器r3。

49.第五p型晶体管mp5具有控制端、第一端以及第二端,其中第五p型晶体管mp5的控制端耦接第四节点n4,第五p型晶体管mp5的第一端耦接第一控制节点nc1,而第五p型晶体管mp5的第二端耦接第五节点n5。第四n型晶体管mn4具有控制端、第一端以及第二端,其中第四n型晶体管mn4的控制端耦接第四节点n4,第四n型晶体管mn4的第一端耦接第五偏压节点nb5,而第四n型晶体管mn4的第二端耦接第五节点n5。第六p型晶体管mp6具有控制端、第一端以及第二端,其中第六p型晶体管mp6的控制端耦接第五节点n5,第六p型晶体管mp6的第一端耦接第一控制节点nc1,而第六p型晶体管mp6的第二端耦接第五节点n5。第五n型晶体管mn5具有控制端、第一端以及第二端,其中第五n型晶体管mn5的控制端耦接第五节点n5,第五n型晶体管mn5的第一端耦接第五偏压节点nb5,而第五n型晶体管mn5的第二端耦接第五节点n5。第七p型晶体管mp7具有控制端、第一端以及第二端,其中第七p型晶体管mp7的控制端耦接第四节点n4,第七型晶体管mp7的第一端耦接第一控制节点nc1,而第七p型晶体管mp7的第二端耦接第一输出节点nout1以输出第一输出电压vout1。第六n型晶体管mn6具有控制端、第一端以及第二端,其中第六n型晶体管mn6的控制端耦接第四节点n4,第六n型晶体管mn6的第一端耦接第五偏压节点nb5,而第六n型晶体管mn6的第二端耦接第一输出节点nout1。

50.第八p型晶体管mp8具有控制端、第一端以及第二端,其中第八p型晶体管mp8的控

制端耦接第五节点n5,第八p型晶体管mp8的第一端耦接第二控制节点nc2,而第八p型晶体管mp8的第二端耦接第四节点n4。第七n型晶体管mn7具有控制端、第一端以及第二端,其中第七n型晶体管mn7的控制端耦接第五节点n5,第七n型晶体管mn7的第一端耦接第五偏压节点nb5,而第七n型晶体管mn7的第二端耦接第四节点n4。第九p型晶体管mp9具有控制端、第一端以及第二端,其中第九p型晶体管mp9的控制端耦接第四节点n4,第九p型晶体管mp9的第一端耦接第二控制节点nc2,而第九p型晶体管mp9的第二端耦接第四节点n4。第八n型晶体管mn8具有控制端、第一端以及第二端,其中第八n型晶体管mn8的控制端耦接第四节点n4,第八n型晶体管mn8的第一端耦接第五偏压节点nb5,而第八n型晶体管mn8的第二端耦接第四节点n4。第十p型晶体管mp10具有控制端、第一端以及第二端,其中第十p型晶体管mp10的控制端耦接第五节点n5,第十型晶体管mp10的第一端耦接第二控制节点nc2,而第十p型晶体管mp10的第二端耦接第二输出节点nout2以输出第二输出电压vout2。第九n型晶体管mn9具有控制端、第一端以及第二端,其中第九n型晶体管mn9的控制端耦接第五节点n5,第九n型晶体管mn9的第一端耦接第五偏压节点nb5,而第九n型晶体管mn9的第二端耦接第二输出节点nout2。第三电阻器r3具有第一端和第二端,其中第三电阻器r3的第一端耦接第五偏压节点nb5,而第三电阻器r3的第二端耦接接地电压vss。

51.在一些实施例中,第六p型晶体管mp6和第五n型晶体管mn5可以提供一偏压电压,其位于第十p型晶体管mp10和第九n型晶体管mn9所形成的反相器的一翻转阈值附近。另外,第九p型晶体管mp9和第八n型晶体管mn8可以提供另一偏压电压,其位于第七p型晶体管mp7和第六n型晶体管mn6所形成的另一反相器的另一翻转阈值附近。在此设计下,输入信号的差模部分将能快速地被响应。第五p型晶体管mp5和第四n型晶体管mn4,以及第八p型晶体管mp8和第七n型晶体管mn7可分别用于增大比较器主体810的增益,提高比较器主体810的比较精度。第一电阻器r1和第二电阻器r2可用于限制两侧第一控制节点nc1和第二控制节点nc2间的电压差。即使输入电压的摆幅(swing)较大,也可快速恢复,不致对比较速度造成影响。还有值得一提的是,比较器主体810的左右两侧结构对称,因此可以实现差分输出、且抗共模波动的能力较强。

52.图9为本发明一实施例所述的稳压器820的示意图。在图9的实施例中,稳压器820包括运算放大器822、第十一p型晶体管mp11、第十二p型晶体管mp12、第十三p型晶体管mp13、第十四p型晶体管mp14、第十n型晶体管mn10、第十一n型晶体管mn11以及第四电阻器r4。

53.运算放大器822具有正输入端、负输入端以及输出端,其中运算放大器822的正输入端用于接收共模电压vcom,运算放大器822的负输入端耦接第十二节点n12,而运算放大器822的输出端耦接第二偏压节点nb2。第十一p型晶体管mp11具有控制端、第一端以及第二端,其中第十一p型晶体管mp11的控制端耦接第二偏压节点nb2,第十一p型晶体管mp11的第一端耦接第一供应电压vdd1,而第十一p型晶体管mp11的第二端耦接第十二节点n12。第十二p型晶体管mp12具有控制端、第一端以及第二端,其中第十二p型晶体管mp12的控制端耦接第十三节点n13,第十二p型晶体管mp12的第一端耦接第十二节点n12,而第十二p型晶体管mp12的第二端耦接第十三节点n13。第十n型晶体管mn10具有控制端、第一端以及第二端,其中第十n型晶体管mn10的控制端耦接第十三节点n13,第十n型晶体管mn10的第一端耦接第十四节点n14,而第十n型晶体管mn10的第二端耦接第十三节点n13。第四电阻器r4具有第

一端和第二端,其中第四电阻器r4的第一端耦接第十四节点n14,而第四电阻器r4的第二端耦接接地电压vss。

54.第十三p型晶体管mp13具有控制端、第一端以及第二端,其中第十三p型晶体管mp13的控制端耦接第二偏压节点nb2,第十三p型晶体管mp13的第一端耦接第一供应电压vdd1,而第十三p型晶体管mp13的第二端耦接第三偏压节点nb3。第十四p型晶体管mp14具有控制端、第一端以及第二端,其中第十四p型晶体管mp14的控制端耦接第十五节点n15,第十四p型晶体管mp14的第一端耦接第三偏压节点nb3,而第十四p型晶体管mp14的第二端耦接第十五节点n15。第十一n型晶体管mn11具有控制端、第一端以及第二端,其中第十一n型晶体管mn11的控制端耦接第十五节点n15,第十一n型晶体管mn11的第一端耦接接地电压vss,而第十一n型晶体管mn11的第二端耦接第十五节点n15。

55.在一些实施例中,稳压器820可藉由共模电压vcom来钳制第一控制节点nc1和第二控制节点nc2处的电压。即使电源(第一供应电压vdd1)有波动,系统的翻转阈值仍可大致维持不变。因此,可以通过共模电压vcom的设置来调节系统的功耗及速度。第十三p型晶体管mp13、第十四p型晶体管mp14、第十一n型晶体管mn11的加入将使节点nb3处的电压可作为比较器主体810的第三偏置节点nb3的电压,扩大比较器主体810可处理的输入电压共模部分的范围。电阻r4可用于调节比较器主体810以及稳压器820的功耗,例如当流经第十二p型晶体管mp12以及第十n型晶体管mn10的电流增大时,可以减小第十二节点n12与第十四节点n14之间的压差,抑制功耗增长。

56.图10为本发明一实施例所述的共模改良电路830的示意图。在图10的实施例中,共模改良电路830包括第十五p型晶体管mp15、第十六p型晶体管mp16、第十七p型晶体管mp17、第十八p型晶体管mp18、第十九p型晶体管mp19、第二十p型晶体管mp20、第二十一p型晶体管mp21、第十二n型晶体管mn12、第十三n型晶体管mn13、第十四n型晶体管mn14、第十五n型晶体管mn15、第十六n型晶体管mn16、第十七n型晶体管mn17、第十八n型晶体管mn18、第十九n型晶体管mn19以及第二十n型晶体管mn20。

57.第十五p型晶体管mp15具有控制端、第一端以及第二端,其中第十五p型晶体管mp15的控制端耦接一接地节点ng,第十五p型晶体管mp15的第一端耦接第四偏压节点nb4,而第十五p型晶体管mp15的第二端耦接第十六节点n16。第十六p型晶体管mp16具有控制端、第一端以及第二端,其中第十六p型晶体管mp16的控制端耦接第二输出节点nout2,第十六p型晶体管mp16的第一端耦接第十六节点n16,而第十六p型晶体管mp16的第二端耦接第十七节点n17。第十七p型晶体管mp17具有控制端、第一端以及第二端,其中第十七p型晶体管mp17的控制端耦接第一输出节点nout1,第十七p型晶体管mp17的第一端耦接第十六节点n16,而第十七p型晶体管mp17的第二端耦接第十八节点n18。第十二n型晶体管mn12具有控制端、第一端以及第二端,其中第十二n型晶体管mn12的控制端耦接第一输出节点nout1,第十二n型晶体管m12的第一端耦接第二输出节点nout2,而第十二n型晶体管mn12的第二端耦接第一输出节点nout1。第十三n型晶体管m13具有控制端、第一端以及第二端,其中第十三n型晶体管mn13的控制端耦接第二输出节点nout2,第十三n型晶体管mn13的第一端耦接第一输出节点nout1,而第十三n型晶体管mn13的第二端耦接第二输出节点nout2。第十四n型晶体管mn14具有控制端、第一端以及第二端,其中第十四n型晶体管mn14的控制端耦接第十七节点n17,第十四n型晶体管mn14的第一端耦接第五偏压节点nb5,而第十四n型晶体管mn14

的第二端耦接第十七节点n17。第十五n型晶体管mn15具有控制端、第一端以及第二端,其中第十五n型晶体管mn15的控制端耦接第十七节点n17,第十五n型晶体管mn15的第一端耦接第五偏压节点nb5,而第十五n型晶体管mn15的第二端耦接第十八节点n18。

58.第十八p型晶体管mp18具有控制端、第一端以及第二端,其中第十八p型晶体管mp18的控制端耦接第十九节点n19,第十八p型晶体管mp18的第一端耦接第四偏压节点nb4,而第十八p型晶体管mp18的第二端耦接第十九节点n19。第十九p型晶体管mp19具有控制端、第一端以及第二端,其中第十九p型晶体管mp19的控制端耦接第十九节点n19,第十九p型晶体管mp19的第一端耦接第四偏压节点nb4,而第十九p型晶体管mp19的第二端耦接第十八节点n18。第十六n型晶体管mn16具有控制端、第一端以及第二端,其中第十六n型晶体管mn16的控制端耦接第二输出节点nout2,第十六n型晶体管mn16的第一端耦接第二十节点n20,而第十六n型晶体管mn16的第二端耦接第十九节点n19。第十七n型晶体管mn17具有控制端、第一端以及第二端,其中第十七n型晶体管mn17的控制端耦接第一输出节点nout1,第十七n型晶体管mn17的第一端耦接第二十节点n20,而第十七n型晶体管mn17的第二端耦接第十八节点n18。第十八n型晶体管mn18具有控制端、第一端以及第二端,其中第十八n型晶体管mn18的控制端耦接第二供应电压vdd2,第十八n型晶体管mn18的第一端耦接第五偏压节点nb5,而第十八n型晶体管的第二端耦接第二十节点n20。

59.第二十p型晶体管mp20具有控制端、第一端以及第二端,其中第二十p型晶体管mp20的控制端耦接第十八节点n18,第二十p型晶体管mp20的第一端耦接第四偏压节点nb4,而第二十p型晶体管mp20的第二端耦接第二十一节点n21。第十九n型晶体管mn19具有控制端、第一端以及第二端,其中第十九n型晶体管mn19的控制端耦接第十八节点n18,第十九n型晶体管mn19的第一端耦接第五偏压节点nb5,而第十九n型晶体管mn19的第二端耦接第二十一节点n21。第二十一p型晶体管mp21具有控制端、第一端以及第二端,其中第二十一p型晶体管mp21的控制端耦接第二十一节点n21,第二十一p型晶体管mp21的第一端耦接第四偏压节点nb4,而第二十一p型晶体管mp21的第二端耦接第二十二节点n22。第二十n型晶体管mn20具有控制端、第一端以及第二端,其中第二十n型晶体管mn20的控制端耦接第二十一节点n21,第二十n型晶体管mn20的第一端耦接第五偏压节点nb5,而第二十n型晶体管mn20的第二端耦接第二十二节点n22。

60.在一些实施例中,共模改良电路830可将前一级电路的比较结果的差模部分进一步放大,以利于后一级电路进行模数(电压域)转换。与图5所示的共模改良电路330不同的是,共模改良电路830采用第十七p型晶体管mp17以及第十七n型晶体管mn17两种晶体管接收前一级电路的输出信号nout1,采用第十六p型晶体管mp16以及第十六n型晶体管mn16两种晶体管接收前一级电路的输出信号nout2,将可适用于更大范围的差分信号nout1与nout2,起到增大输入(作为本级的输入)范围的作用。再者,共模改良电路830是分别以第四偏置节点nb4以及第五偏置节点nb5(即图8所示的第四偏置节点nb4以及第五偏置节点nb5)作为其电源供应端,而使信号nout1与nout2的摆幅接近于节点第四偏置节点nb4与第五偏置节点nb5的电压差,该电压差相当于图9所示的共模电压vcom与第十四节点n14的电压差。第十二n型晶体管mn12以及第十三n型晶体管mn13用于限制输入信号nout1的摆幅,增加恢复速度。相较于图5所示的共模改良电路330,共模改良电路830的输出信号(第二十一节点n21、第二十二节点n22的电压)的摆幅更大,方便后一级电路实施模数(电压域)转换。

61.图11为本发明一实施例所述的模拟对数字转换器840的示意图。在图11的实施例中,模拟对数字转换器840包括第二十二p型晶体管mp22、第二十三p型晶体管mp23、第二十四p型晶体管mp24、第二十五p型晶体管mp25、第二十一n型晶体管mn21、第二十二n型晶体管mn22、第二十三n型晶体管mn23以及第二十一n型晶体管mn24。

62.第二十二p型晶体管mp22具有控制端、第一端以及第二端,其中第二十二p型晶体管mp22的控制端耦接第二十三节点n23,第二十二p型晶体管mp22的第一端耦接第二供应电压vdd2,而第二十二p型晶体管mp22的第二端耦接第二十四节点n24。第二十三p型晶体管mp23具有控制端、第一端以及第二端,其中第二十三p型晶体管mp23的控制端耦接第二十四节点n24,第二十三p型晶体管mp23的第一端耦接第二供应电压vdd2,而第二十三p型晶体管mp23的第二端耦接第二十三节点n23。第二十一n型晶体管mn21具有控制端、第一端以及第二端,其中第二十一n型晶体管mn21的控制端耦接第二十二节点n22,第二十一n型晶体管mn21的第一端耦接接地电压vss,而第二十一n型晶体管mn21的第二端耦接第二十四节点n24。第二十二n型晶体管mn22具有控制端、第一端以及第二端,其中第二十二n型晶体管mn22的控制端耦接第二十一节点n21,第二十二n型晶体管mn22的第一端耦接接地电压vss,而第二十二n型晶体管mn22的第二端耦接第二十三节点n23。

63.第二十四p型晶体管mp24具有控制端、第一端以及第二端,其中第二十四p型晶体管mp24的控制端耦接第二十三节点n23,第二十四p型晶体管mp24的第一端耦接第二供应电压vdd2,而第二十四p型晶体管mp24的第二端耦接第二十五节点n25。第二十三n型晶体管mn23具有控制端、第一端以及第二端,其中第二十三n型晶体管mn23的控制端耦接第二十三节点n23,第二十三n型晶体管mn23的第一端耦接接地电压vss,而第二十三n型晶体管mn23的第二端耦接第二十五节点n25。第二十五p型晶体管mp25具有控制端、第一端以及第二端,其中第二十五p型晶体管mp25的控制端耦接第二十五节点n25,第二十五p型晶体管mp25的第一端耦接第二供应电压vdd2,而第二十五p型晶体管mp25的第二端耦接最终输出节点noutf以输出最终输出电压voutf。第二十四n型晶体管mn24具有控制端、第一端以及第二端,其中第二十四n型晶体管mn24的控制端耦接第二十五节点n25,第二十四n型晶体管mn24的第一端耦接接地电压vss,而第二十四n型晶体管mn24的第二端耦接最终输出节点noutf。

64.在一些实施例中,第二供应电压vdd2小于前述第一供应电压vdd1。模拟对数字转换器840可将高电压域的比较结果转至低电压域。由于前一级电路的输出结果(作用于第二十一节点n21以及第二十二节点n22)的摆幅相对较大,也就是第二十一n型晶体管mn21以及第二十二n型晶体管mn22接收的控制信号摆幅较大,而使模拟对数字转换器840可提供相对较小的静态功耗。

65.根据实际测量结果,本发明所提的高速比较器系统至少具有下列优点:(1)响应速度快、精确度高,结构简单;(2)对制程影响,电源电压、温度波动等皆不敏感;(3)无论高速、低速信号变化均可监测;(4)速度及功耗可调节;(5)适合各种应用条件,不用重复校准;以及(6)输出至不同电压域的比较结果,但不会大幅增加功耗。

66.值得注意的是,以上所述的电压、电流、电阻值、电感值、电容值,以及其余组件参数均非为本发明的限制条件。设计者可以根据不同需要调整这些设定值。本发明的高速比较器系统并不仅限于图1-11所图示的状态。本发明可以仅包括图1-11的任何一或多个实施例的任何一或多项特征。换句话说,并非所有图标的特征均须同时实施于本发明的高速比

较器系统当中。虽然本发明的实施例是使用金属氧化物半导体场效应晶体管为例,但本发明并不仅限于此,本领域技术人员可改用其他种类的晶体管,例如:接面场效应晶体管,或是鳍式场效应晶体管等等,而不致于影响本发明的效果。

67.在本说明书以及权利要求书中的序数,例如“第一”、“第二”、“第三”等等,彼此之间并没有顺序上的先后关系,其仅用于标示区分两个具有相同名字的不同组件。

68.本发明虽以优选实施例公开如上,然其并非用以限定本发明的范围,本领域技术人员,在不脱离本发明的精神和范围内,当可做些许的更动与润饰,因此本发明的保护范围当视所附权利要求书界定范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1